Reference Router Architecture

- NetFPGA Reference Router Architecture - Describes the architecture of the reference router.

- DE5 Reference Router Architecture - Describes the architecture of the DE5 NetFPGA reference router.

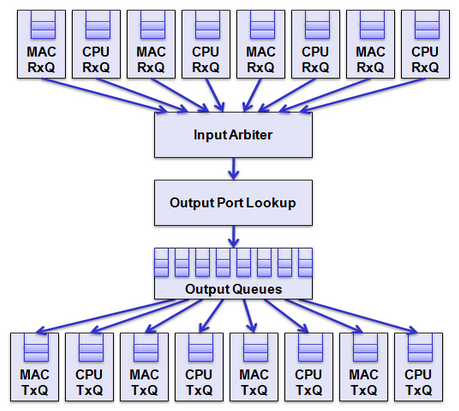

NetFPGA Reference Router Architecture

The NetFPGA reference router is a complete IPv4 router which is able to simultaneously forward packets from all four 1 Gbps interfaces on the NetFPGA card. As seen in Figure, the main components of the reference router include input queues (RxQ), an arbiter which selects packets from a specific input queue, an output port lookup, and interfaces to output queues (TxQ). The output port lookup requires an access to a forwarding table which indicates the packet destination based on information in the packet header. A detailed overview of the reference router architecture can be found at NetFPGA.

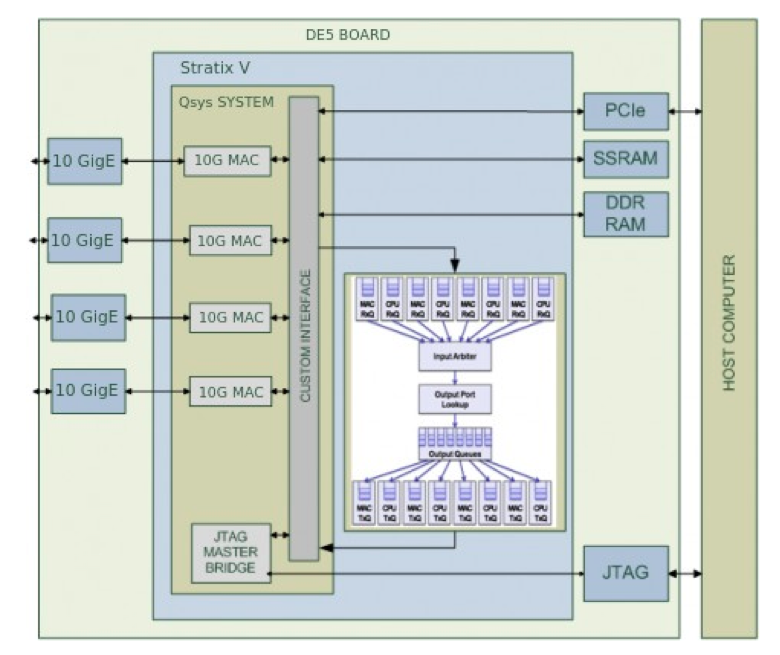

DE5 Reference Router Architecture

The DE5 reference router is implemented on a QSYS based system which provides easy integration of different interfaces to the FPGA fabric. The reference router is integrated along with this QSYS builder as illustrated in the Figure below. The MAC queues connect to the 10 Gigabit Ethernet Interface and the CPU queues connect to the PCI Express interface through the QSYS builder. The PCI Express Interface sends packets from the host machine through the PCI Express link. The JTAG interface provides an alternate interface for configuring the registers on the FPGA and also for debugging the design. A detailed overview of the reference router can be found at NetFPGA.

DE5 Reference Router Walk Through

Related Documents

- DE5 User Manual - Altera DE5 User Manual.

- Windriver Software Setup - Windriver software setup walkthrough.

- PCI Express IP Compiler User Guide

PCI Express IP Compiler provided by Altera was used to implement the PCIe Interface in this project. - Avalon-ST JTAG Interface Core User Guide

The Avalon® Streaming (Avalon-ST) JTAG Interface core was used to enable the communication between SOPC Builder systems and JTAG hosts.