Introduction to SimpleScalar

SimpleScalar (http://www.simplescalar.com) is an open source computer architecture simulator developed by Todd Austin (http://www.eecs.umich.edu/~taustin/) while he was a PhD student at the University of Wisconsin Madison.

It is a simulator, which in simple words means that it can be used to show that Machine A is better than Machine B without building either Machine A or Machine B. It is written using ‘C’ programming language.

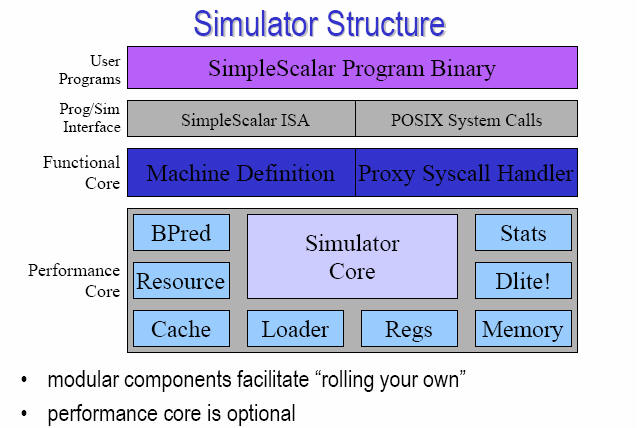

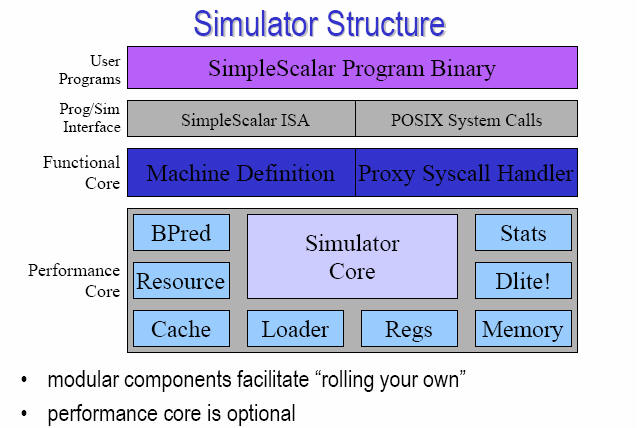

SimpleScalar is a set of tools that model a virtual computer system with CPU, Cache and Memory Hierarchy. Using the SimpleScalar tools, users can build modeling applications that simulate real programs running on a range of modern processors and systems. The tool set includes sample simulators ranging from a fast functional simulator to a detailed, dynamically scheduled processor model that supports non-blocking caches, speculative execution, and state-of-the-art branch prediction. In addition to simulators, the SimpleScalar tool set includes performance visualization tools, statistical analysis resources, and debug and verification infrastructure.

The SimpleScalar tools are used widely for research and instruction, for example, in 2000 more than one third of all papers published in top computer architecture conferences used the SimpleScalar tools to evaluate their designs.

Which Instruction Set Architectures (ISA) it can simulate?

SimpleScalar can simulate Alpha and PISA (Portable ISA). Others are being added to the SimpleScalar. The PISA instruction set is a simple MIPS-like instruction set maintained primarily for instructional use. The tool set takes binaries compiled for the SimpleScalar architecture and simulates their execution on one of several provided processor simulators. The machine running SimpleScalar is called the Host machine or Host while the ISA that one is targeting such as Alpha or PISA is called Target. Gcc cross-compiler for PISA is available on the internet. Cross-compiler creates a sort of illusion that the underlying machine where PISA instructions are executed is a PISA machine while it is not. The following figure illustrates this notion.

(Block diagram of SimpleScalar architecture)

Which Simulators are available in the SimpleScalar toolset?

The tool set itself consists of a collection of microarchitecture simulators that emulate the microprocessor at different levels of detail .The simulators that we will use are:

sim-fast: fast instruction interpreter, optimized for speed. This simulator does not account for the behavior of pipelines, caches, or any other part of the microarchitecture. It performs only functional simulation using in-order execution of the instructions (i.e. they are executed in the order they appear in the program).

sim-safe: slightly slower instruction interpreter, as it checks for memory alignment and memory access permission on all memory operations. This simulator can be used if the simulated program causes sim-fast to crash without explanation.

sim-profile: instruction interpreter and profiler. This simulator keeps track of and reports dynamic instruction counts, instruction class counts, usage of address modes, and profiles of the text and data segments.

sim-cache: memory system simulator. This simulator can emulate a system with multiple levels of instruction and data caches, each of which can be configured for different sizes and organizations. This simulator is ideal for fast cache simulation if the effect of cache performance on execution time is not needed.

sim-bpred: branch predictor simulator. This tool can simulate difference branch prediction schemes and reports results such as prediction hit and miss rates. Like sim-cache, this does not simulate accurately the effect of branch prediction on execution time.

sim-outorder: detailed microarchitectural simulator. This tool models in detail and out-of-order microprocessor with all of the bells and whistles, including branch prediction, caches, and external memory. This simulator is highly parameterized and can emulate machines of varying numbers of execution units.

You may find useful to view these slides Simulators and such in describing the simulators in brief and general.

References:

2) http://www.eecs.umich.edu/~taustin/papers/UWTR97-simple.pdf

3) http://www.cems.uwe.ac.uk/~rwilliam/ACA_ufeEHK-20-3/simplescalar_article_in_ieee_computer.pdf

4) www.cs.wisc.edu/~markhill/cs752/Fall2004/includes/ss_tutorial_fall2004.ppt