# ECE 697J – Advanced Topics in Computer Networks

ACE Programming Model and SDK 11/13/03

#### Overview

- Programming Model

- Active Computing Element (ACE) Abstraction

- Allocation of ACEs to microengines

- Packet Queues

- Software Development Kit

- Simulator

- Example: IP forwarding

- Lab 2: IP forwarding and classification on IXP1200

#### **Last Class**

Active Computing Element (ACE) abstraction:

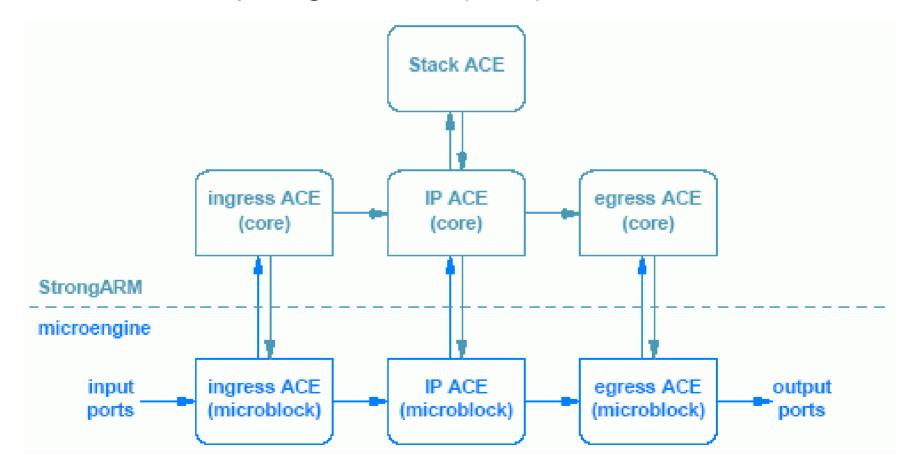

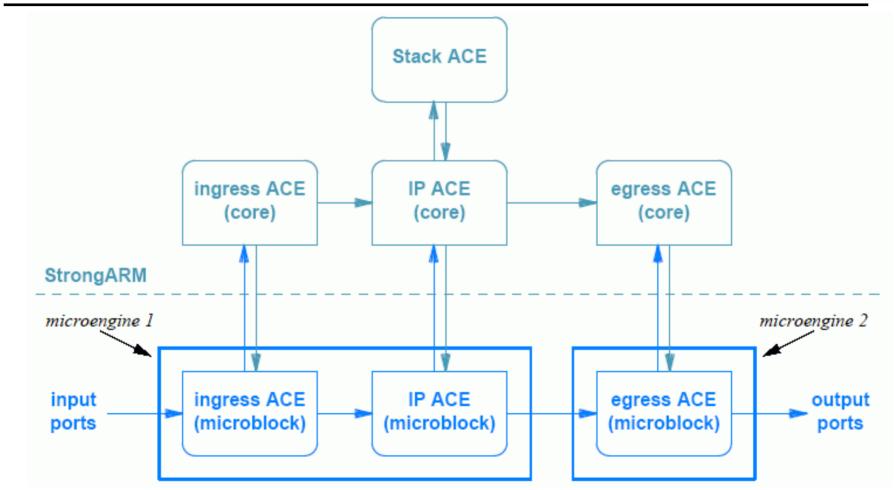

# Microengine Assignment

- Packet processing involves several microblocks

- How should microblocks be allocated to microengines?

- One microblock per micorengine

- Multiple microblocks per microengine (in pipeline)

- Multiple pipelines on multiple microengines

- What are pros and cons?

- Passing packets between microengines incurs overhead

- Pipelining causes inefficiencies if blocks are not equal in size

- Multiple blocks per microengine causes contention and requires more instruction storage

- Intel terminology: "microblock group"

- Set of microblock running on one microengine

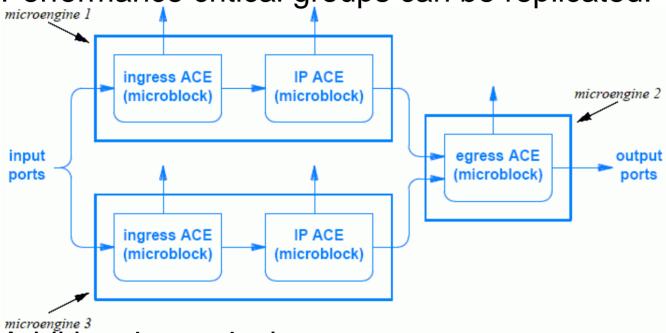

# Microblock Groups

Microblock groups can be replicated to increase parallelism

# Microblock Group Replication

Performance critical groups can be replicated:

- Additional complexity:

- Single core component (not replicated) communicates with multiple groups

- Multiple inputs, multiple output

#### **Control of Packet Flow**

- Packets require different processing blocks

- IP requires different microblocks than ARP

- Special packets get handed off to core

- "Dispatch Look" control packet flow among microblocks

- Each thread runs its own dispatch loop

- Infinite loop that grabs packets and hands them to microblocks

- Return value from microblock determines the next step

- Invocation of microblock is similar to function call

# **Dispatch Loop**

Example:

```

Two microblocks

(ingress + IP)

```

```

while (1) {

Get next packet from input device(s);

Invoke ingress microblock;

if (return code == 0) {

Drop the packet;

} else if ( return code == 1 ) {

Send packet to ingress core component;

} else { /* IP packet */

Invoke IP microblock;

if (return code == 0) {

Drop packet;

} else if ( return code == 1 ) {

Send packet to IP core component;

} else {

Send packet to egress microblock;

```

# **Dispatch Loop Conventions**

- Parameters passed to microblock:

- Buffer handle for frame that contains a packet

- Set of state registers that contain information about the frame

- A variable called dl\_next\_block in which return value gets stored

- State registers:

- Information about packet: length

- Information generated by software: classification result

- Registers can be changed by microblock

- Return values:

- Meaning assigned by programmer

- Conventions: zero = "drop packet", other values for "pass on" and "send to core" etc.

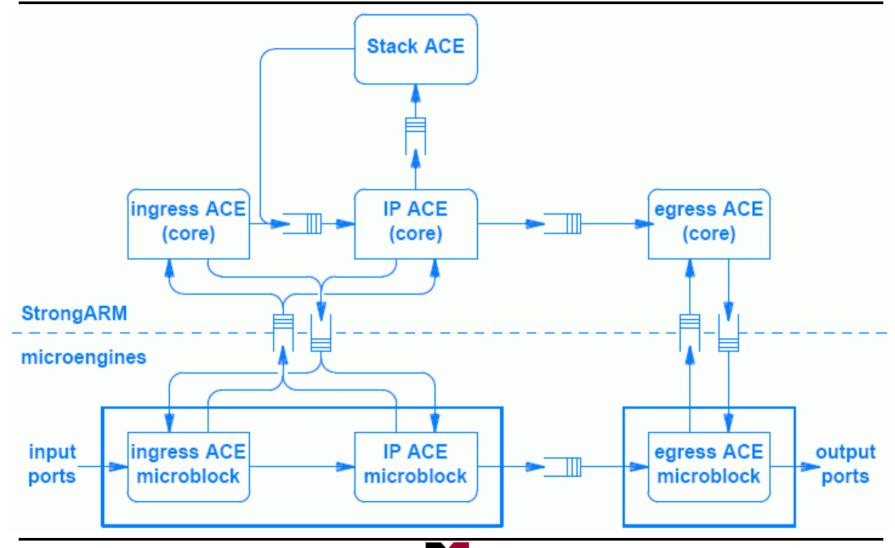

## **Packet Queues**

- Packet flow depends on packet data

- Processing time depends on packet data

- Packet movement can't be predicted

- Microblocks need to continue processing without waiting

- Packets need to be buffered

- "Communication Queues"

- Unidirectional FIFO (yes, really FIFO)

- Bidirectional communication requires two queues

- Also between microblocks and core

- Single queue for all microblock group instances

- Uses exception mechanism "IX\_EXCEPTION"

- Exception handler in core determines further steps

# Packet Queue Example

University of Massachusetts Amherst

#### Crosscalls

- Mechanism for non-packet communication between ACEs

- Similar to remote procedure calls and remote method invocations

- Caller and callee need to agree on parameters

- Interface Definition Language (IDL) specifies details

- IDL compiler creates "stubs" to handle marshaling

- Types of crosscalls

- Deferred: caller does not block, asynchronous notification

- Oneway: caller does not block, no return value

- Twoway: caller blocks, callee returns value

- ACEs are prohibited from twoway calls

- No blocking allowed

- Other control software (non-ACE) may use all types

# SDK

Software Development Kit:

| Software        | Purpose                                                                     |

|-----------------|-----------------------------------------------------------------------------|

| C compiler      | Compile C programs for the StrongARM                                        |

| NCL compiler    | Compile NCL programs for the StrongARM                                      |

| MicroC compiler | Compile C programs for the microengines                                     |

| Assembler       | Assemble programs for the microengines                                      |

| Simulator       | Simulate an IXP1200 to debug code                                           |

| Downloader      | Load software into the network processor                                    |

| Monitor         | Communicate with the network processor and interact with running software   |

| Bootstrap       | Start the network processor running                                         |

| Reference Code  | Example programs for the IXP1200 that show how to implement basic functions |

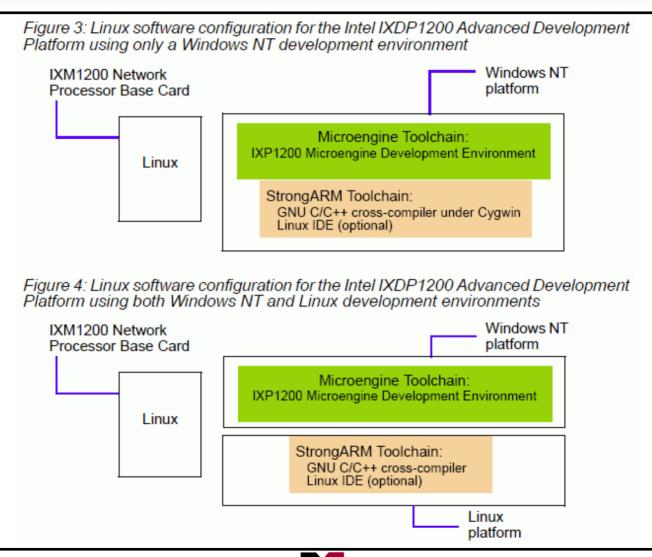

# Software Setup

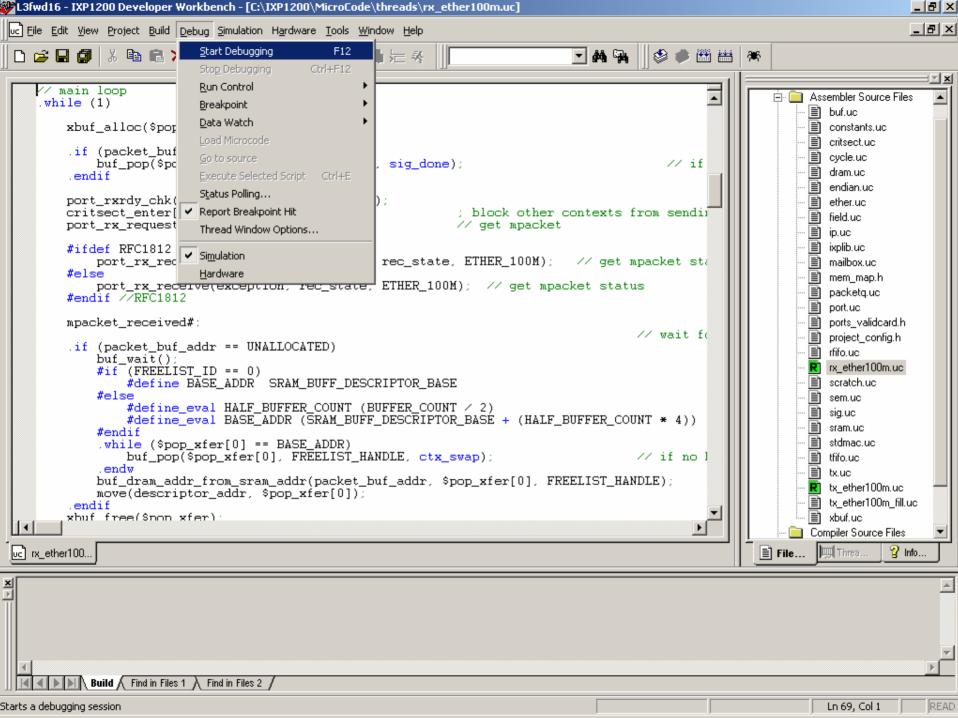

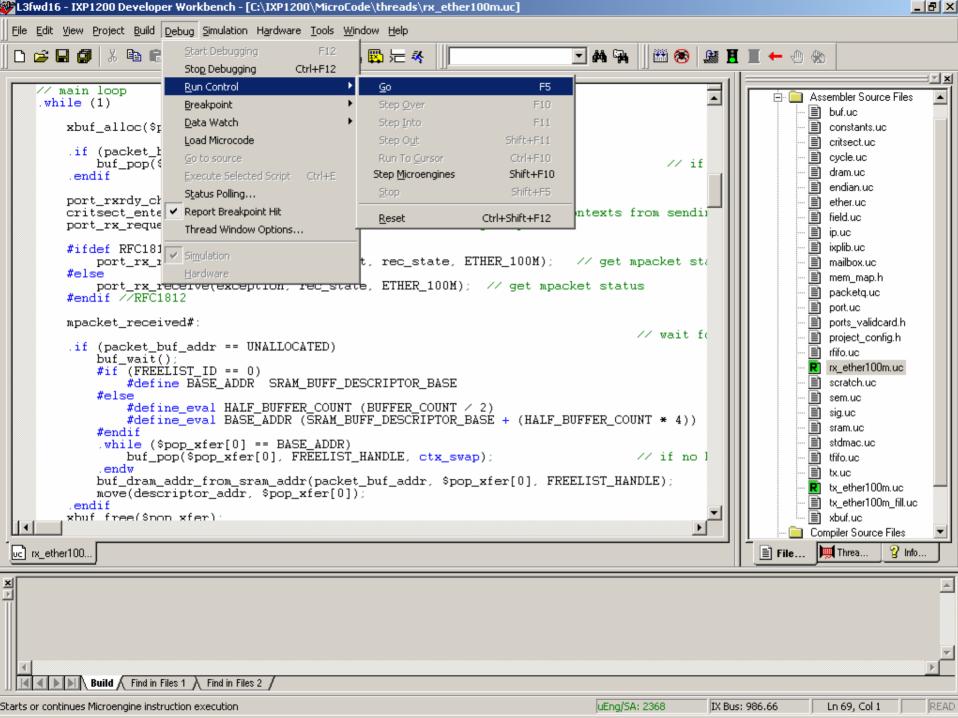

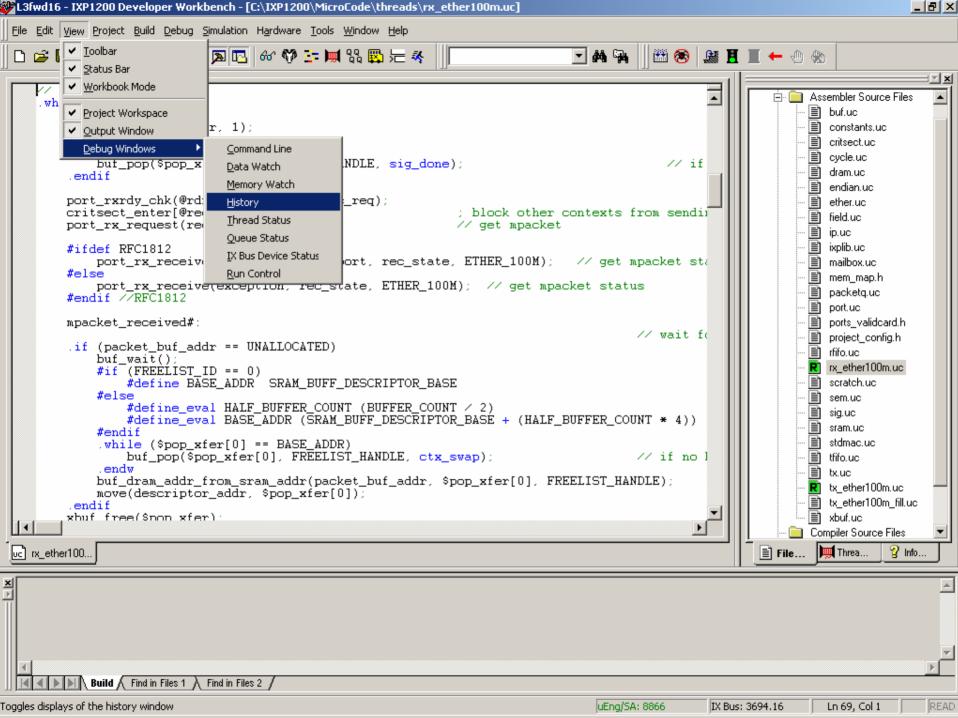

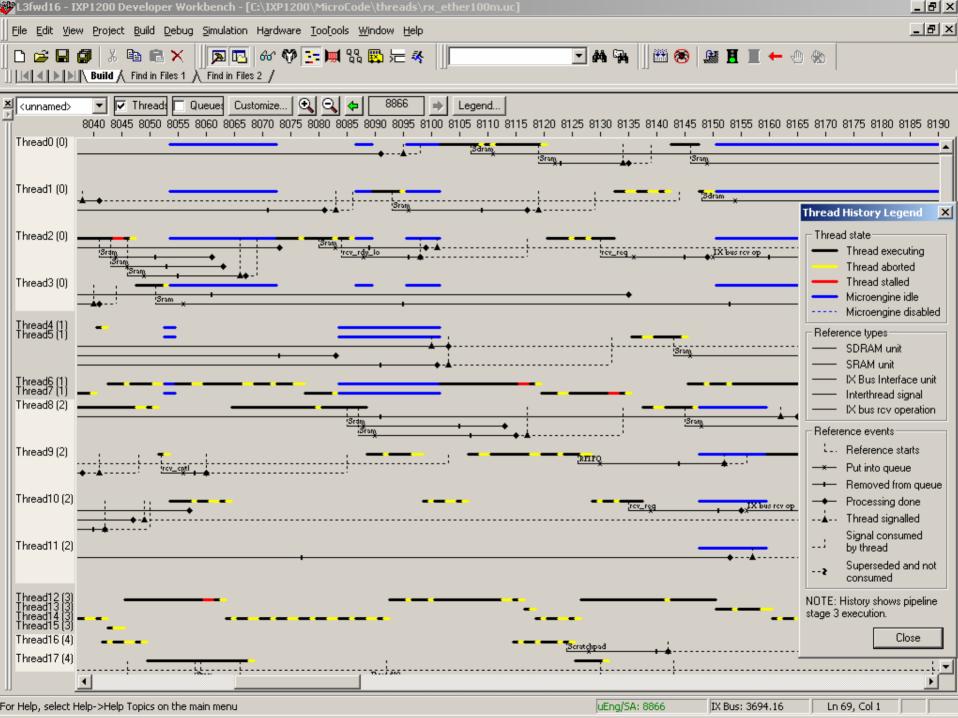

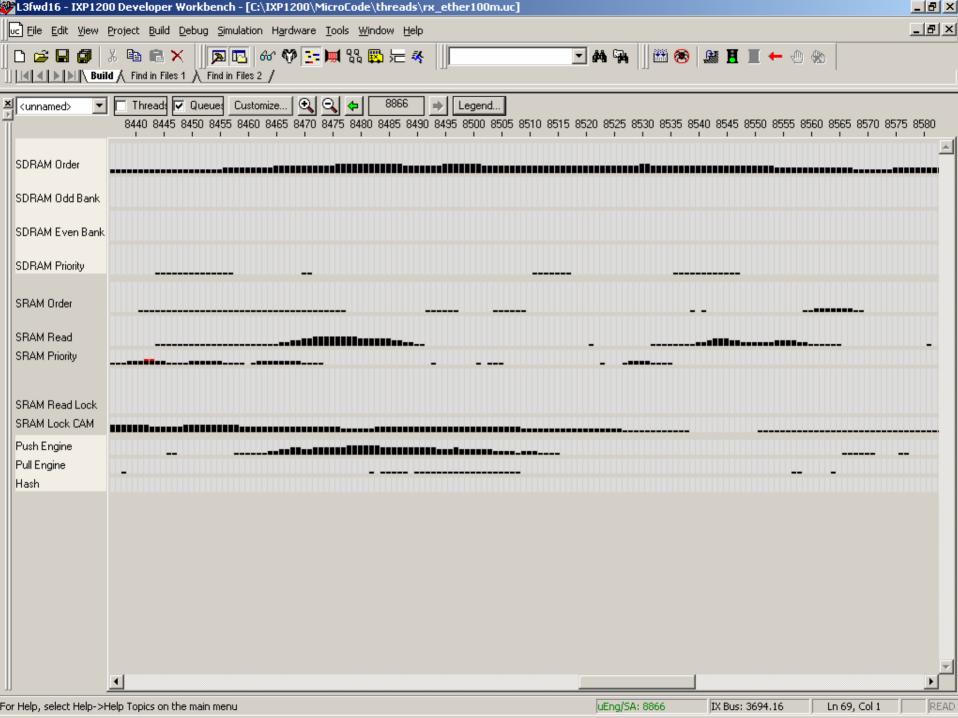

#### **Simulator**

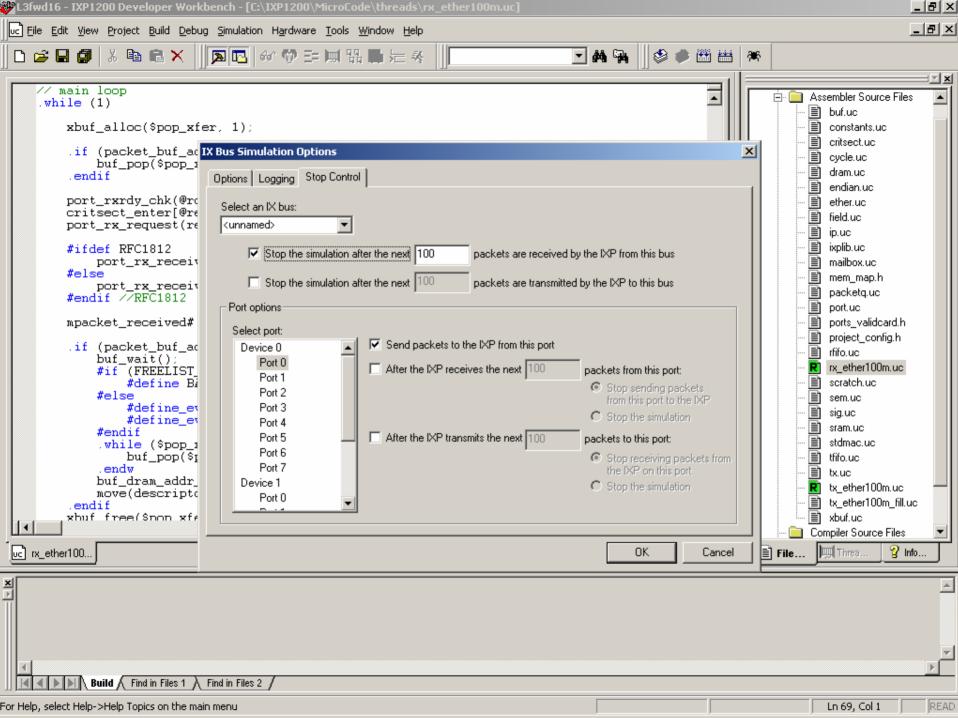

- Cycle-accurate simulation of IXP1200

- Allows for easy experimentation

- Packet generator

- Visualization for thread behavior, memory accesses

- Runs under Windows

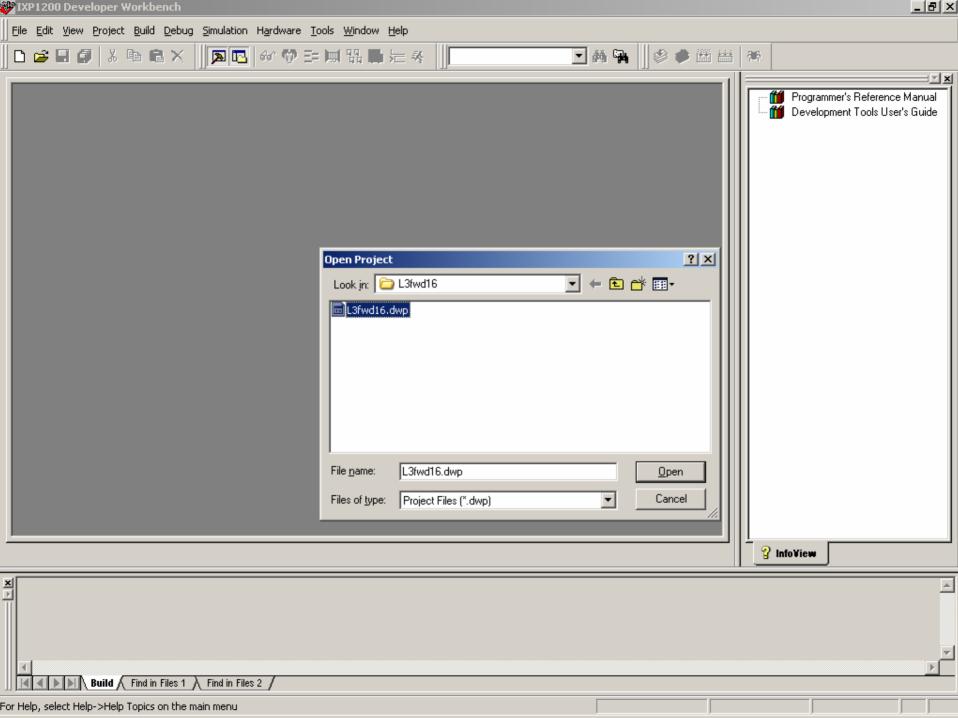

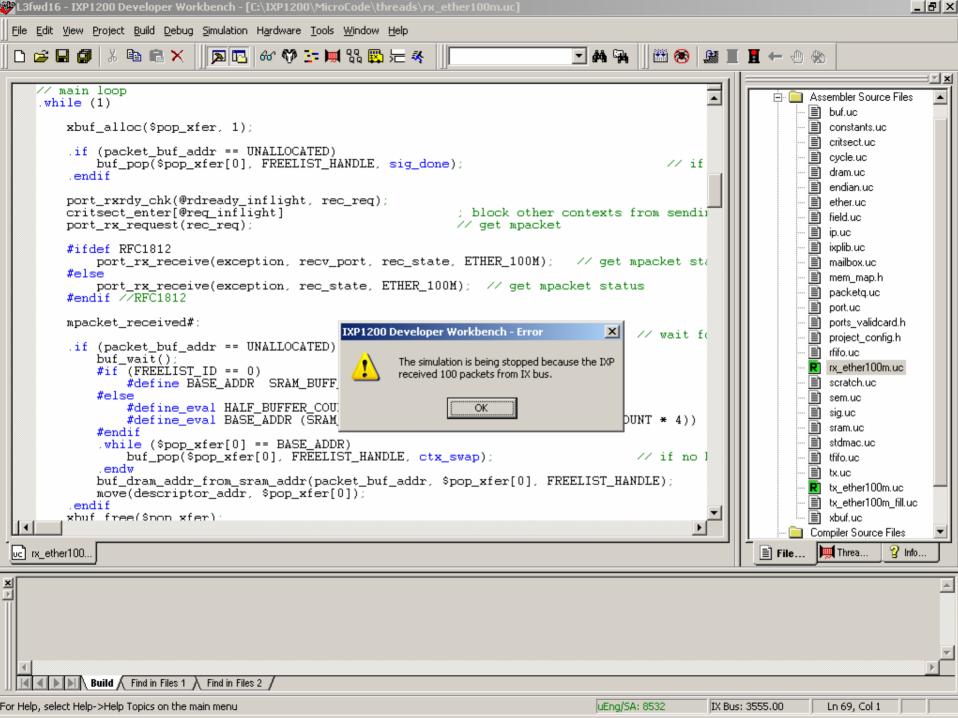

- We will use simulator for Lab 2

- Part I: run existing IP forwarding example, collect statistics

- Part II: make a minor modification for classification

- We have lab machines set up for you

- You can also install simulator on your own machine (big!)

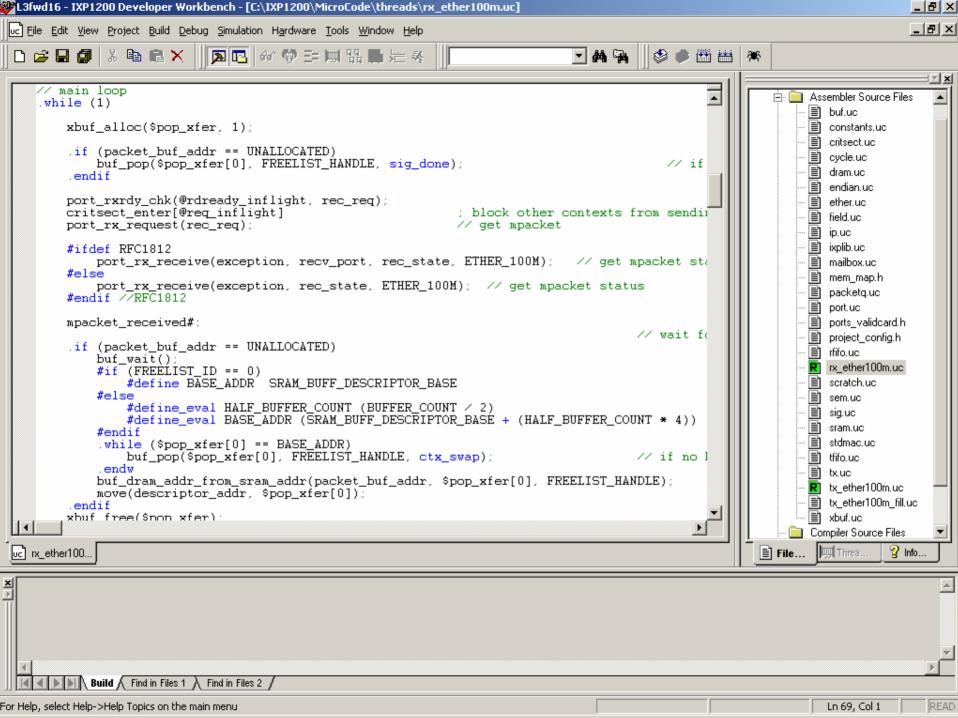

# **IP Forwarding Example**

- Full-blown RFC1812-compliant IP forwarding

- Lots of special cases

- Look for main program structure

- 4 uE for IP processing (0-3)

- 3 uE for output queuing (4-5)

- Run program and collect workload statistics

- Thread behavior

- Memory accesses

- Instruction coverage

- Etc.

## Lab 2

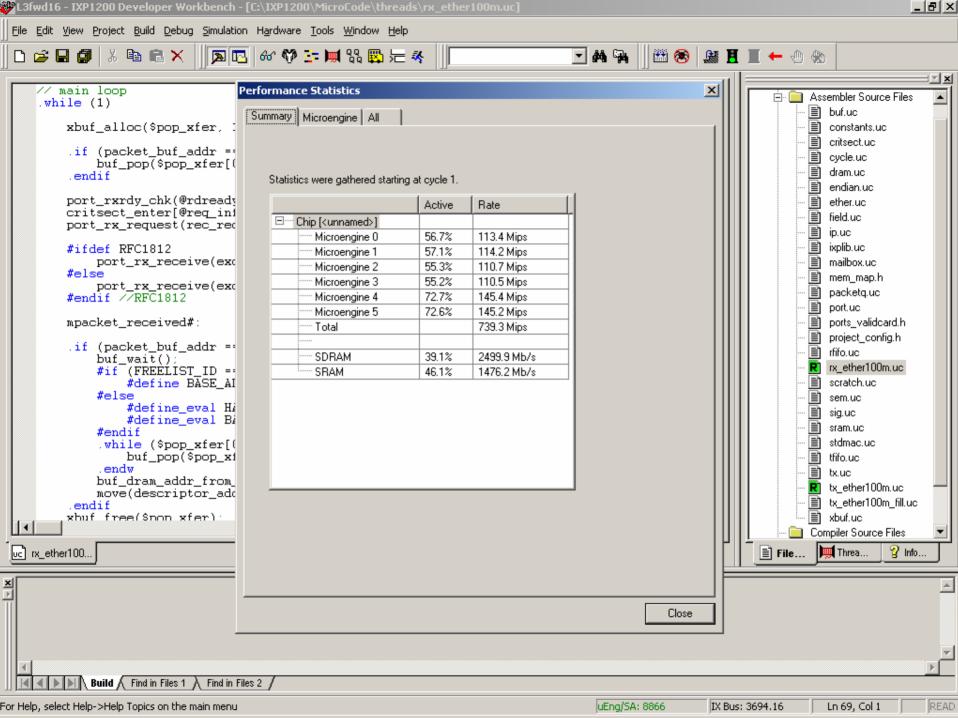

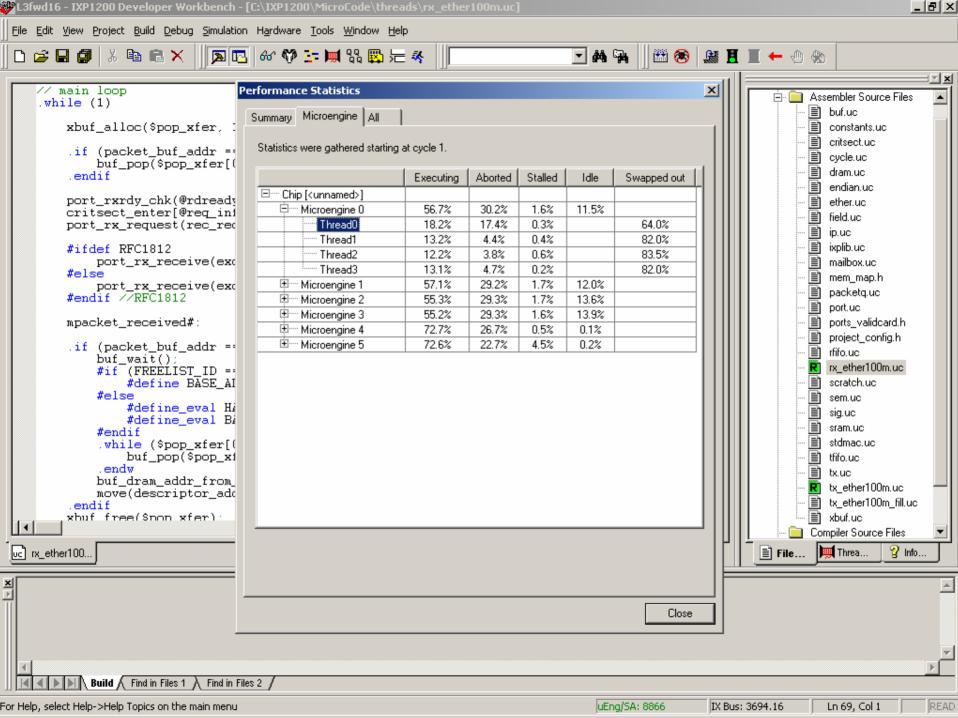

#### Part I: Collect statistics

- Microengine utilization for all microengines

- Detailed statistics of one thread from uE 0 and one from uE 5

- Processing power of microengines (in MIPS).

- Memory utilization and bandwidth.

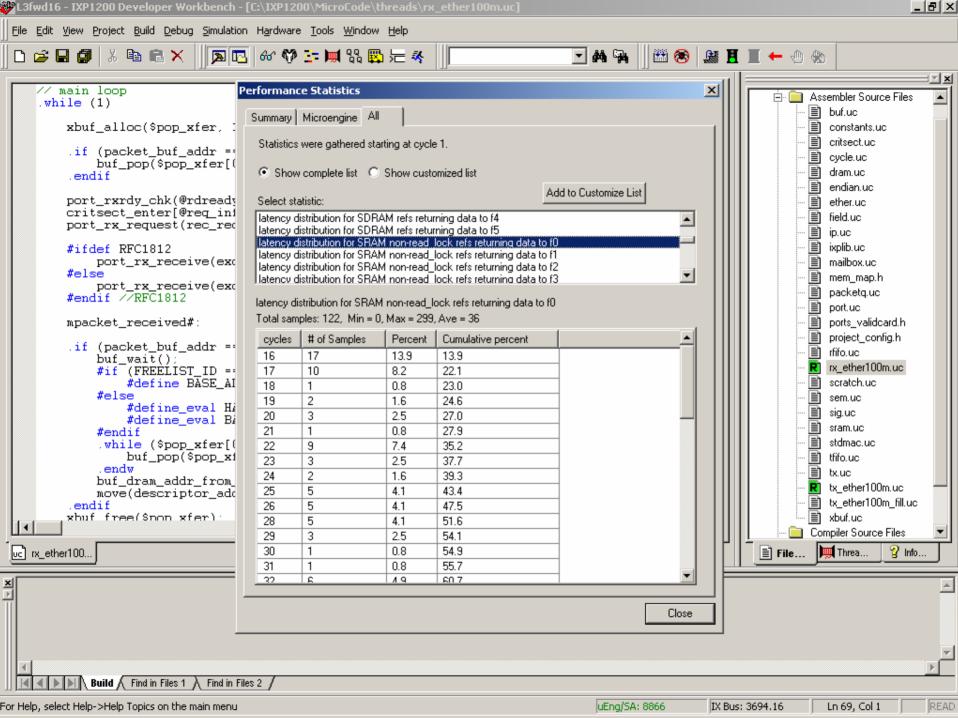

- Latency distribution for SDRAM refs for microengine 0 and SRAM non-read\_lock refs for microengine 0. Show a graph.

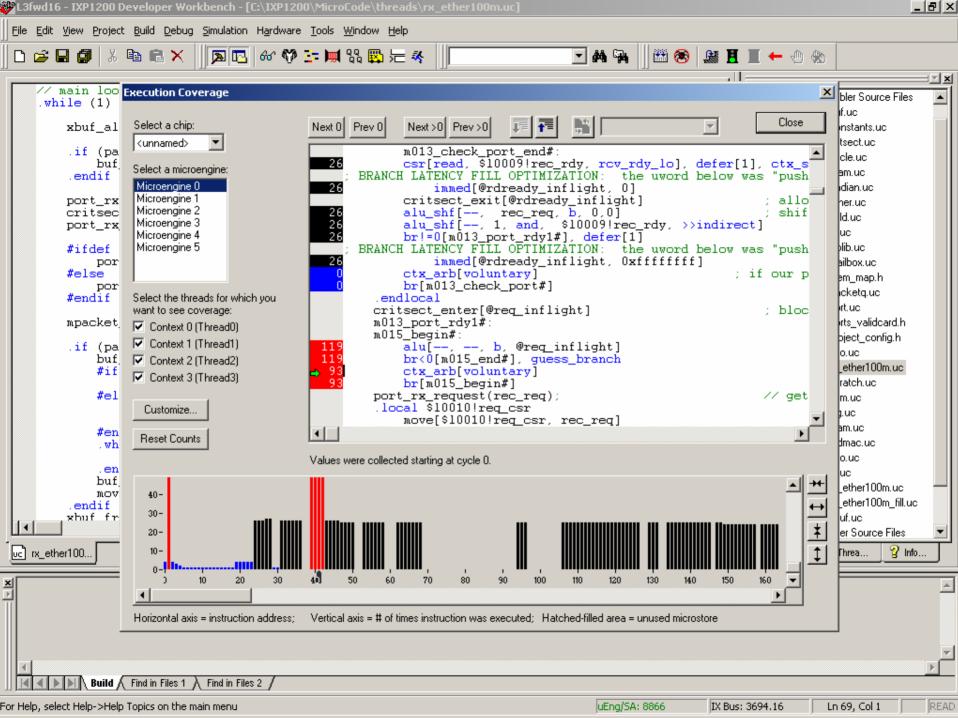

- Show a screenshot for the thread history that shows overlapping SRAM and SDRAM requests by the same microengine.

- Identify the overall delay for either request (in cycles). What factors contributed how much to the overall delay?

- DUE NEXT TUESDAY.

#### Lab 1 Results

- Grading: 20 points total

- Results: 10 points

- Code: 3 points

- TCP state machine + explaination: 2+1 points

- IP and TCP headers: 1+1 points

- Report (written content): 2 points

- Average: 16.6

- Max: 20

- Min: 14

### **Next Class**

- Microengine programming

- Assembler

- Instructions

- Register access

- Assembler directives

- Etc.

- Read Chapter 24

- Turn in Part I of Lab 2