# Intel<sup>®</sup> IXP1200 Network Processor Family

Hardware Reference Manual

December 2001

Part Number: 278303-009

### **Revision History**

| Revision Date | Revision | Description                                      |

|---------------|----------|--------------------------------------------------|

| 8/30/99       | 001      | Beta 1 release.                                  |

| 10/29/99      | 002      | Beta 3 release.                                  |

| 3/2/00        | 003      | Beta 4 release.                                  |

| 6/5/00        | 004      | Version 1.0 release.                             |

| 9/27/00       | 005      | Version 1.1 release.                             |

| 12/20/00      | 006      | Version 1.2 release.                             |

| 6/1/01        | 007      | Version 1.3 SDK release.                         |

| 8/10/01       | 800      | Version 2.0 SDK release. Miscellaneous changes.  |

| 12/07/01      | 009      | Version 2.01 SDK release. Miscellaneous changes. |

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IXP1200 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries \*Other names and brands may be claimed as the property of others.

| 1 | Introd                   | uction                                                 |                                                                                                                                                                                                                                                                | 15                                                                                     |

|---|--------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|   | 1.1<br>1.2<br>1.3        | Related                                                | his Document<br>d Documentation<br>ntions<br>Data Terminology<br>Definitions                                                                                                                                                                                   | 15<br>16<br>16                                                                         |

| 2 | Techn                    | ical Intro                                             | duction                                                                                                                                                                                                                                                        | 17                                                                                     |

|   | 2.1<br>2.2<br>2.3<br>2.4 | IXP120<br>Key Ard<br>Some A<br>2.4.1<br>2.4.2<br>2.4.3 | ew<br>00 Functional Units<br>chitectural Features<br>Architectural Concepts<br>References<br>Signals and Synchronization<br>Context Swapping and Threads                                                                                                       | 18<br>19<br>21<br>21<br>22<br>23                                                       |

|   |                          | 2.4.4<br>2.4.5<br>2.4.6                                | Some Examples<br>Local Data Storage and Block Transfers                                                                                                                                                                                                        | 25                                                                                     |

|   | 2.5<br>2.6<br>2.7        | Externa                                                | Concurrency<br>Packet Data Flow                                                                                                                                                                                                                                | 26<br>29<br>30<br>31<br>37<br>37<br>41<br>42<br>42<br>42<br>45<br>45<br>46<br>47<br>47 |

|   | 2.8                      | Softwar                                                | re Development Tools                                                                                                                                                                                                                                           |                                                                                        |

| 3 | Strong                   | gARM* Co                                               | ore                                                                                                                                                                                                                                                            | 51                                                                                     |

|   | 3.1<br>3.2               |                                                        | ew<br>Architecture<br>Coprocessors<br>Memory Management Unit (MMU)<br>3.2.2.1 MMU Faults and CPU Aborts<br>3.2.2.2 Data Aborts<br>3.2.2.3 Interaction of the MMU, Icache, Dcache, and Write Buffer<br>3.2.2.4 MMU Enable/Disable<br>Instruction Cache (Icache) | 51<br>52<br>52<br>52<br>52<br>52<br>53                                                 |

|        |         | 3.2.3.1 Icache Operation                                       |     |

|--------|---------|----------------------------------------------------------------|-----|

|        |         | 3.2.3.2 Icache Validity                                        |     |

|        | 0.0.4   | 3.2.3.3 Icache Enable/Disable and Reset                        |     |

|        | 3.2.4   | Data Caches (Dcaches)                                          |     |

|        |         | 3.2.4.1 Main Data Cache                                        |     |

|        |         | 3.2.4.2 Mini Cache<br>3.2.4.3 Dcaches Enable/Disable and Reset | 55  |

|        |         | 3.2.4.4 Deache Operation                                       |     |

|        |         | 3.2.4.5 Software Dcache Flush                                  | 57  |

|        | 3.2.5   | Write Buffer                                                   |     |

|        | 5.2.5   | 3.2.5.1 Write Buffer Operation                                 |     |

|        |         | 3.2.5.2 Enabling and Disabling the Write Buffer                | 58  |

|        | 3.2.6   | Read Buffer                                                    |     |

|        | 0.2.0   | 3.2.6.1 Read Buffer Operation                                  |     |

|        | 3.2.7   | ARM* Instruction Set and Timing                                |     |

|        | 3.2.7   | Exceptions                                                     |     |

|        | 3.2.0   | 3.2.8.1 Exception Priorities                                   |     |

|        |         | 3.2.8.2 Exception Vector Table                                 | 61  |

|        |         | 3.2.8.3 Hard Reset                                             | 61  |

|        |         | 3.2.8.4 Abort                                                  |     |

|        |         | 3.2.8.5 Undefined Instruction                                  |     |

|        | 3.2.9   | StrongARM* Core Debug Support                                  |     |

|        | 0.2.0   | 3.2.9.1 Instruction Breakpoint                                 |     |

|        |         | 3.2.9.2 Data Breakpoint                                        |     |

| 3.3    | Memor   | у Мар                                                          |     |

| 3.4    |         | d IRQ Interrupts                                               |     |

| 3.5    |         | l Peripheral Units                                             |     |

| 0.0    | 3.5.1   | UART                                                           |     |

|        | 0.0.1   | 3.5.1.1 Receive Procedure                                      |     |

|        |         | 3.5.1.2 Transmit Procedure                                     | 69  |

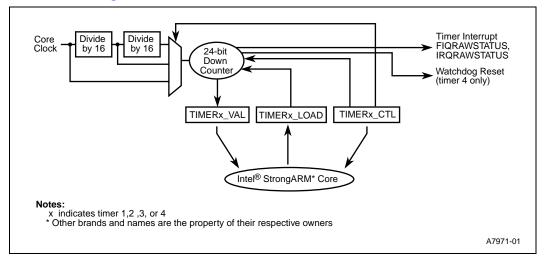

|        | 3.5.2   | Timers                                                         |     |

|        | 3.5.3   | Real-Time Clock (RTC)                                          |     |

|        | 5.5.5   | 3.5.3.1 RTC Setup Procedures                                   |     |

|        |         | 3.5.3.2 Using the RTC Alarm                                    |     |

|        |         | 3.5.3.3 Determining the Trim Values                            |     |

|        | 3.5.4   | General Purpose I/O (GPIO)                                     |     |

| 3.6    |         | equence                                                        |     |

|        |         |                                                                |     |

| Microe | ngines  |                                                                | .75 |

| 4.1    | Overvie | ew                                                             | 75  |

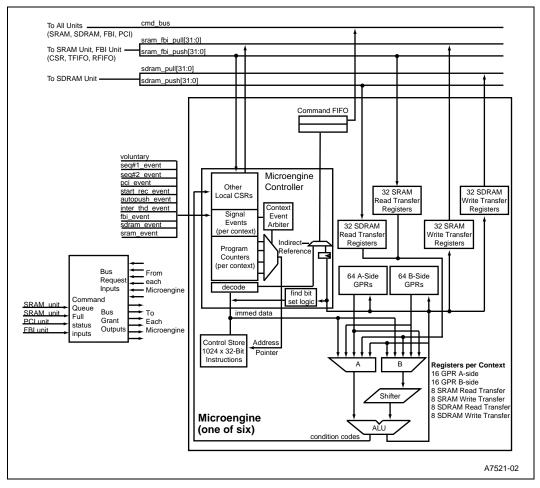

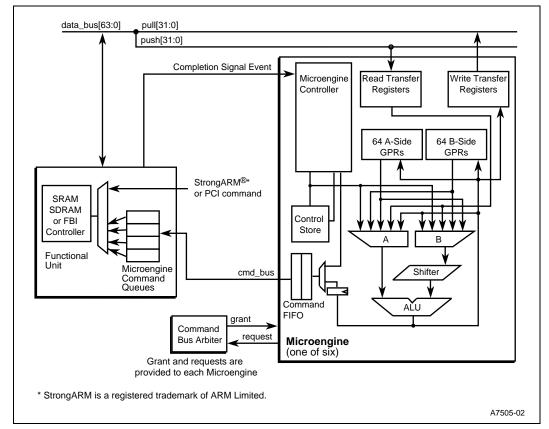

| 4.2    |         | ngine Block Diagram                                            |     |

|        | 4.2.1   | Multithread Support                                            |     |

|        | 4.2.2   | Control Store                                                  |     |

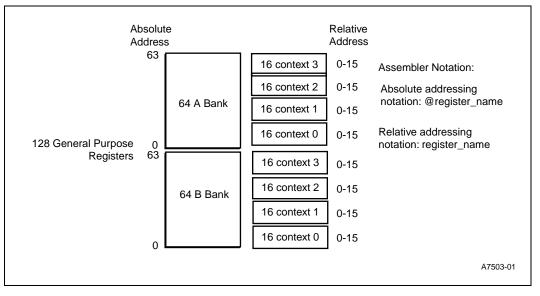

|        | 4.2.3   | 128 General-Purpose Registers (GPRs)                           |     |

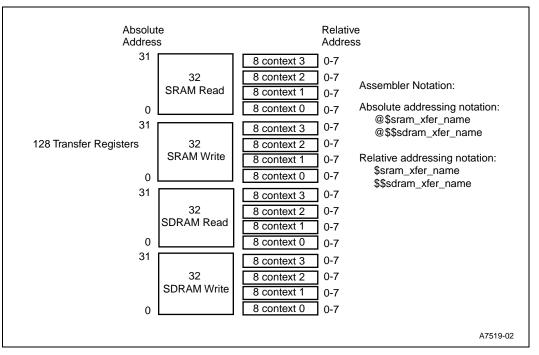

|        | 4.2.4   | 128 Transfer Registers                                         |     |

|        | 4.2.4   | ALU and Shifter                                                |     |

|        | 4.2.5   | Command Bus Arbiter                                            |     |

|        | 4.2.0   | Local CSRs                                                     |     |

| 4.3    |         |                                                                |     |

|        |         | ngine Instruction Set                                          |     |

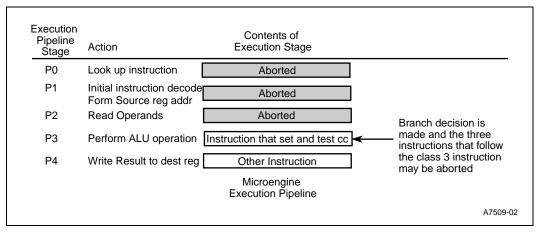

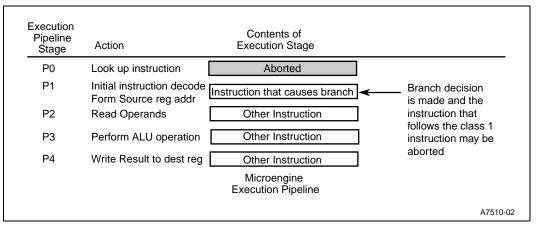

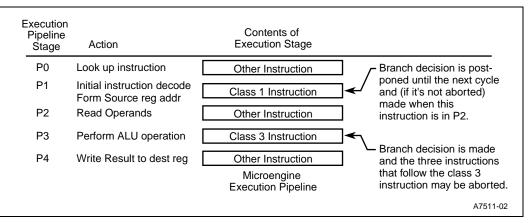

| 4.4    |         | ion Pipeline                                                   |     |

| 4.5    | Branch  | Decisions                                                      | .80 |

|      | 4.5.1   | Class 3 Instructions                                |     |

|------|---------|-----------------------------------------------------|-----|

|      | 4.5.2   | Class 2 Instructions                                |     |

|      | 4.5.3   | Class 1 Instructions                                | 83  |

|      | 4.5.4   | Postponed Branch Decision                           | 84  |

|      | 4.5.5   | Deferred Branch                                     | 85  |

|      | 4.5.6   | Setting Condition Codes Early                       | 86  |

|      | 4.5.7   | Guess Branch                                        |     |

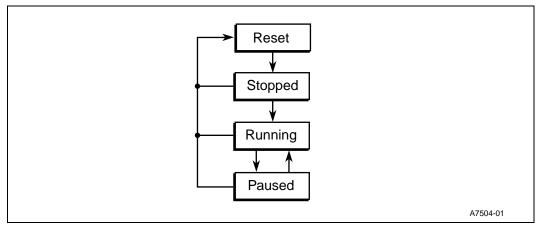

| 4.6  | Execut  | ion States                                          | 87  |

|      | 4.6.1   | Reset State                                         | 87  |

|      | 4.6.2   | Stopped State                                       | 87  |

|      | 4.6.3   | Running State                                       |     |

|      | 4.6.4   | Paused State                                        |     |

| 4.7  | Progra  | mming the Microengines                              |     |

|      | 4.7.1   | Starting Point of Program Execution                 |     |

| 4.8  | Microe  | ngine Registers                                     |     |

|      | 4.8.1   | General-Purpose Registers                           |     |

|      | 4.8.2   | Transfer Registers                                  |     |

|      |         | 4.8.2.1 Managing Solicited Accesses                 |     |

|      |         | 4.8.2.2 Managing Unsolicited Autopush Accesses      |     |

| 4.9  | ALU ar  | nd Shifter                                          | 94  |

|      | 4.9.1   | Condition Codes                                     | 95  |

|      | 4.9.2   | Multiply Support                                    | 96  |

| 4.10 | Chang   | ing Contexts                                        |     |

|      |         | Šignal Events                                       |     |

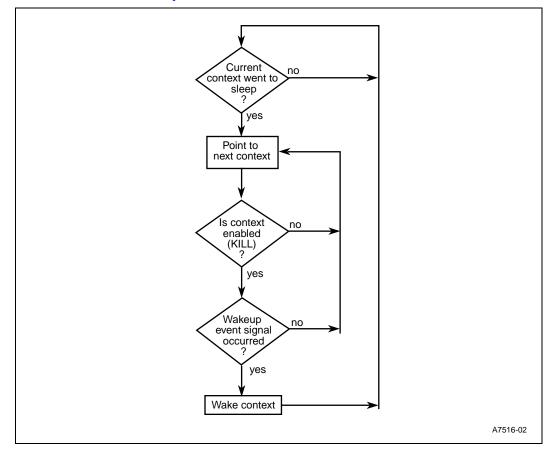

|      |         | Context Event Arbiter (Waking a Thread)             |     |

| 4.11 |         | cing to Other Functional Units                      |     |

|      | 4.11.1  |                                                     |     |

|      |         | 4.11.1.1Setting Up the Transfer Registers           |     |

|      |         | 4.11.1.2Issuing a Command                           |     |

|      |         | 4.11.1.3Command Serviced in Queue                   |     |

|      |         | 4.11.1.4 Moving Data to and from Transfer Registers |     |

|      |         | 4.11.1.5Signaling Completion                        |     |

|      |         | PCI DMA                                             |     |

|      |         | FAST_WR Instruction                                 |     |

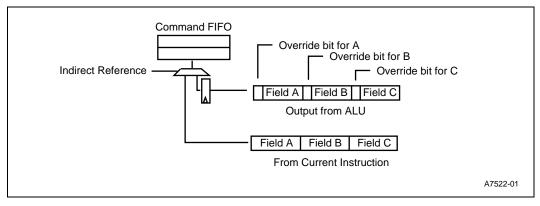

|      | 4.11.4  | Indirect References                                 | 108 |

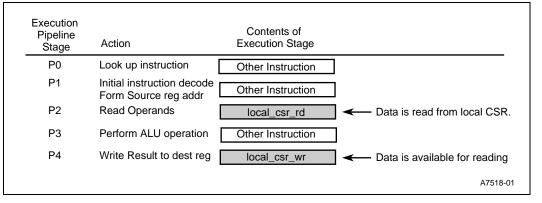

| 4.12 |         | CSRs                                                |     |

| 4.13 |         | t Set Instructions                                  |     |

| 4.14 |         | itates                                              |     |

| 4.15 | Inter-P | rocessor Communications                             |     |

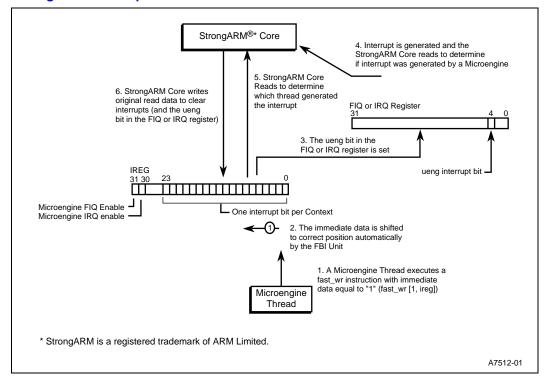

|      | 4.15.1  | Generating StrongARM* Core Interrupts               | 116 |

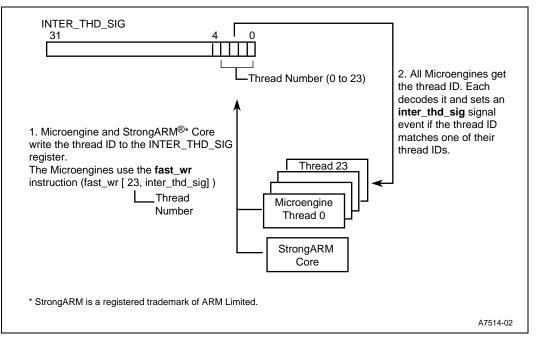

|      | 4.15.2  | Generating Inter-thread Signal Events               | 117 |

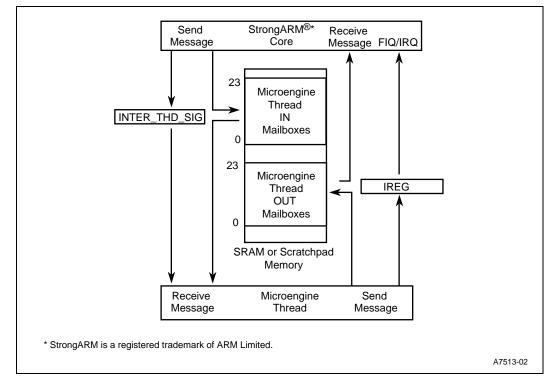

|      | 4.15.3  | Communication Example                               | 118 |

| 4.16 | Chaine  | d SDRAM References                                  | 119 |

| 4.17 | Debug   | ging Support                                        | 119 |

|      | 4.17.1  | Determining If a Microengine is Executing           | 119 |

|      | 4.17.2  | Stopping, Starting, and Hopping the Microengines    |     |

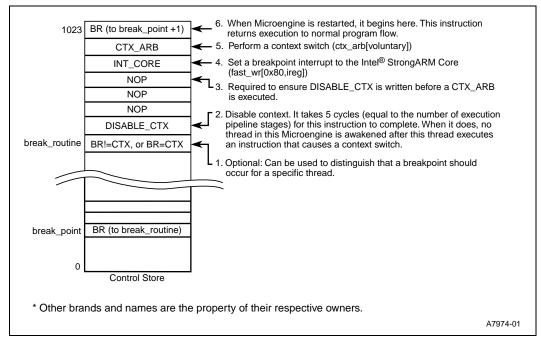

|      | 4.17.3  | Breakpoints                                         | 120 |

|      | 4.17.4  | Reading Microengine GPR and Read Transfer Registers | 122 |

|      | 4.17.5  | Creating a Journal                                  |     |

|      |         |                                                     |     |

5

# intel®

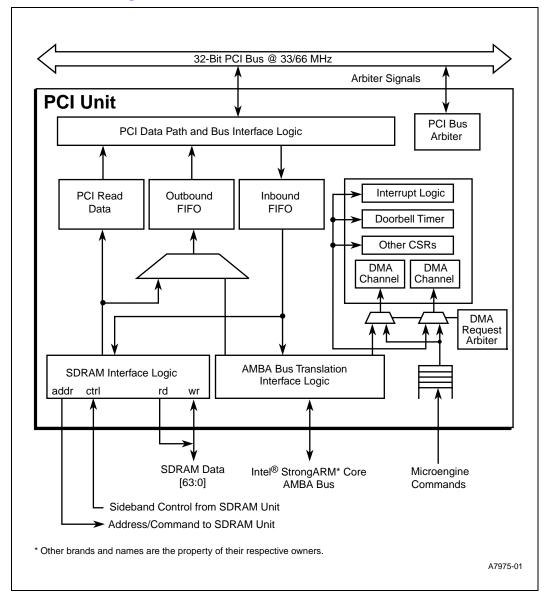

| PCI UI | nit     |                                                                    | 125 |

|--------|---------|--------------------------------------------------------------------|-----|

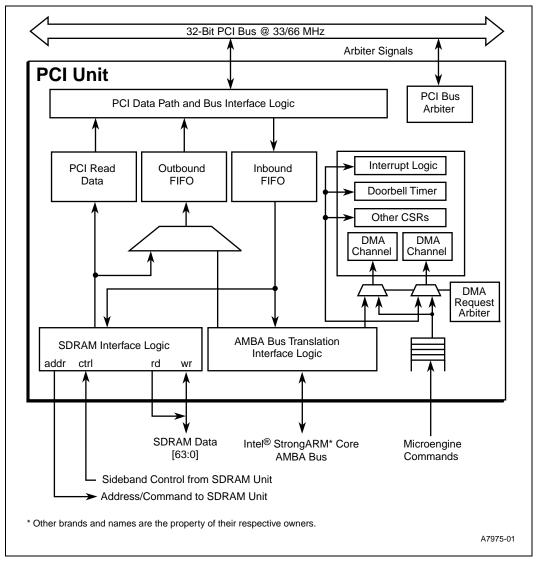

| 5.1    | Overvi  | ew                                                                 | 125 |

| 5.2    |         | are Description                                                    |     |

|        | 5.2.1   | PCI Bus Arbiter                                                    |     |

|        | 5.2.2   | DMA Channels                                                       |     |

|        | •       | 5.2.2.1 Allocation of the DMA Channels                             |     |

|        |         | 5.2.2.2 StrongARM* Core Initiated DMA Channel Operation            |     |

|        |         | 5.2.2.3 Microengine Initiated DMA Channel Operation                |     |

|        |         | 5.2.2.4 SDRAM-to-PCI Transfer                                      | 131 |

|        |         | 5.2.2.5 PCI-to-SDRAM Transfer                                      | 131 |

|        | 5.2.3   | I <sub>2</sub> O* Message Unit                                     | 132 |

|        |         | 5.2.3.1 I <sub>2</sub> O Inbound FIFO Operation                    |     |

|        |         | 5.2.3.2 $I_2^{-}O$ Outbound FIFO Operation                         |     |

|        | 5.2.4   | Mailbox and Doorbell Registers                                     |     |

|        | 5.2.5   | PCI Interrupt Pin                                                  |     |

| 5.3    | PCI Tra | ansactions                                                         | 141 |

|        | 5.3.1   | Generating the Address                                             | 141 |

|        |         | 5.3.1.1 Target Transactions - Internal Address Generation          |     |

|        |         | 5.3.1.2 Master Transactions - PCI Address Generation               |     |

|        |         | 5.3.1.3 Master Configuration Transactions - PCI Address Generation |     |

|        | 5.3.2   | Enabling PCI Bus Transactions                                      |     |

|        | 5.3.3   | PCI Target Transactions                                            |     |

|        |         | 5.3.3.1 Unsupported PCI Cycles As Target                           |     |

|        |         | 5.3.3.2 Memory Write to SDRAM (Target Write)                       | 144 |

|        |         | 5.3.3.3 Memory Read, Read Line, Read Multiple to SDRAM             |     |

|        |         | (Target Read)                                                      | 144 |

|        |         | 5.3.3.4 Type 0 Configuration Write                                 |     |

|        |         | 5.3.3.5 Type 0 Configuration Read<br>5.3.3.6 Write to CSR          |     |

|        |         | 5.3.3.7 Read to CSR                                                |     |

|        |         | 5.3.3.8 Write to I <sub>2</sub> O Address                          |     |

|        |         | 5.3.3.9 Read to $I_2O$ Address                                     |     |

|        | 5.3.4   | PCI Master Transactions                                            |     |

|        | 0.011   | 5.3.4.1 Unsupported PCI Cycles As Master                           |     |

|        |         | 5.3.4.2 Memory Write, Memory Write and Invalidate                  |     |

|        |         | 5.3.4.3 Memory Read, Memory Read Line, Memory Read Multiple        |     |

|        |         | 5.3.4.4 I/O Write                                                  |     |

|        |         | 5.3.4.5 I/O Read                                                   |     |

|        |         | 5.3.4.6 Configuration Write                                        | 150 |

|        |         | 5.3.4.7 Configuration Read                                         |     |

|        |         | 5.3.4.8 Special Cycle                                              |     |

|        |         | 5.3.4.9 IACK Read                                                  |     |

|        |         | 5.3.4.10PCI Request Operation<br>5.3.4.11Master Latency Timer      |     |

|        | FOF     |                                                                    |     |

|        | 5.3.5   | Errors As PCI Target<br>5.3.5.1 Address Parity Error               |     |

|        |         | 5.3.5.2 Write Data Parity Error                                    |     |

|        |         | 5.3.5.3 Read Data Parity Error                                     | 152 |

|        | 5.3.6   | Errors As PCI Master                                               |     |

|        | 5.5.0   | 5.3.6.1 Master Abort                                               |     |

|        |         | 5.3.6.2 Write Data Parity Error                                    |     |

|        |         | 5.3.6.3 Target Abort on Write                                      |     |

|        |         |                                                                    | .00 |

|       |                     | 5.3.6.4 Read Data Parity Error                                      |         |

|-------|---------------------|---------------------------------------------------------------------|---------|

|       |                     | 5.3.6.5 Target Abort on Read                                        | ••••    |

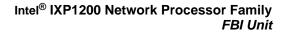

| FBI U | Jnit                |                                                                     |         |

| 6.1   |                     | rchitecture                                                         |         |

| 6.2   |                     | Pull Engine Interface                                               |         |

| 0.2   | 6.2.1               | Push and Pull Engines                                               |         |

|       | 6.2.1               | Microengine Initiated FBI References                                |         |

|       | 6.2.2               |                                                                     |         |

|       |                     | StrongARM* Core Initiated FBI References                            |         |

|       | 6.2.4               | FBI Signal Events (to Microengines)                                 |         |

|       | 6.2.5               | Command Ordering                                                    |         |

|       | 6.2.6               | FBI Command Bus Arbiter Signaling                                   |         |

|       | 6.2.7               | Scratchpad Test and Set/Clear Instructions                          |         |

|       | 6.2.8               | Scratchpad Increment Instruction                                    |         |

| ~ ~   | 6.2.9               | Hash Instruction                                                    |         |

| 6.3   |                     | chpad Memory                                                        |         |

|       | 6.3.1               | Read and Write Operations                                           |         |

|       | 6.3.2               | Bit Write Operations                                                |         |

|       | 6.3.3               | Auto Increment Operations                                           |         |

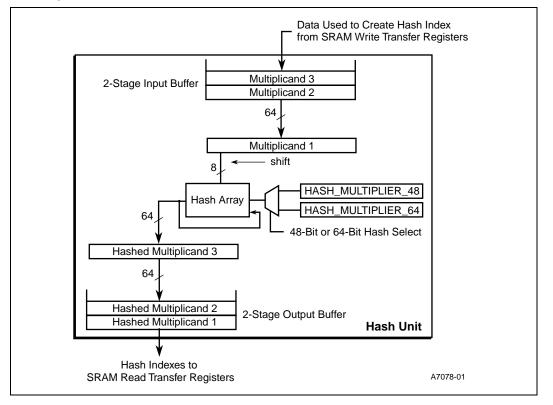

| 6.4   |                     | Unit                                                                |         |

|       | 6.4.1               | Hashing Operation                                                   |         |

|       | 6.4.2               | Hash Algorithm                                                      |         |

| 6.5   | FBI C               | SRs                                                                 |         |

|       | 6.5.1               | CSR Reads and Writes                                                |         |

|       | 6.5.2               | FAST_WR Support                                                     |         |

|       | 6.5.3               | FBI CSR Description Summary                                         |         |

|       |                     | 6.5.3.1 IX Bus Receive Registers                                    |         |

|       |                     | 6.5.3.2 IX Bus Transmit Registers                                   |         |

|       |                     | 6.5.3.3 IX Bus and Ready Bus Configuration Registers                |         |

|       |                     | 6.5.3.4 Ready Bus Control Registers                                 |         |

|       |                     | 6.5.3.5 Hash Unit Configurations Registers                          |         |

|       |                     | 6.5.3.6 FBI Interrupt/Signal Registers                              |         |

|       |                     | 6.5.3.7 Thread Status Registers                                     |         |

|       | <b>. .</b> <i>.</i> | 6.5.3.8 Miscellaneous Registers                                     |         |

|       | 6.5.4               | Cycle Count Register                                                |         |

|       | 6.5.5               | Self Destruct Register                                              |         |

|       | 6.5.6               | Thread Status Registers (THREAD_DONE)                               |         |

| 6.6   |                     | s Interface                                                         |         |

|       |                     | Configuring the IX Bus and Ready Bus                                |         |

|       | 6.6.2               | IX Bus and Ready Bus Modes                                          |         |

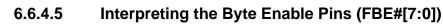

|       |                     | 6.6.2.1 64-bit Bidirectional and 32-bit Unidirectional IX Bus Modes |         |

|       |                     | 6.6.2.2 1-2 MAC Mode and 3+ MAC Mode                                |         |

|       |                     | 6.6.2.3 Shared IX Bus Mode                                          |         |

|       |                     | 6.6.2.4 Status Mode                                                 |         |

|       | 6.6.3               | Ready Bus                                                           |         |

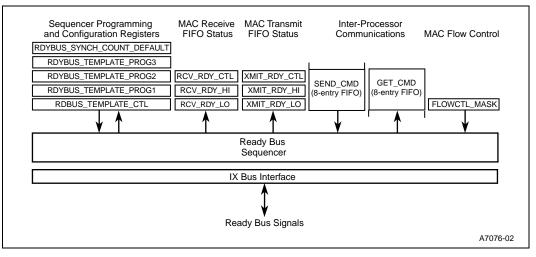

|       |                     | 6.6.3.1 Ready Bus Sequencer                                         |         |

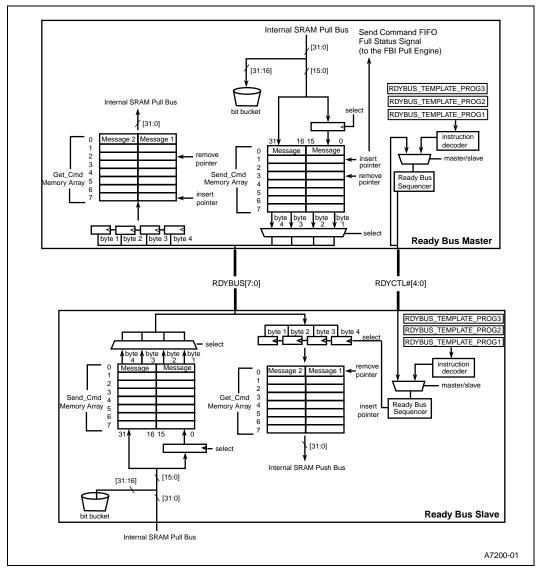

|       |                     | 6.6.3.2 Ready Bus Master and Slave Modes                            |         |

|       |                     | 6.6.3.3 Ready Bus Instructions                                      |         |

|       |                     | 6.6.3.4 Reading the MAC FIFO Ready Flags                            |         |

|       |                     | 6.6.3.5 Receive Ready Flags<br>6.6.3.6 Transmit Ready Flags         |         |

|       |                     |                                                                     |         |

|       |                     | 6.6.3.7 Autopush Operation                                          | • • • • |

|                 | .6.3.8 Interpreting The Receive Ready Flags                     |       |

|-----------------|-----------------------------------------------------------------|-------|

|                 | .6.3.10Ready Bus Communications                                 |       |

|                 | .6.3.11Example Ready Bus Sequencer Programs                     |       |

|                 | eceive State Machine and RFIFO - Receiving Data From IX Bus     |       |

|                 | .6.4.1 Issuing a Receive Request                                |       |

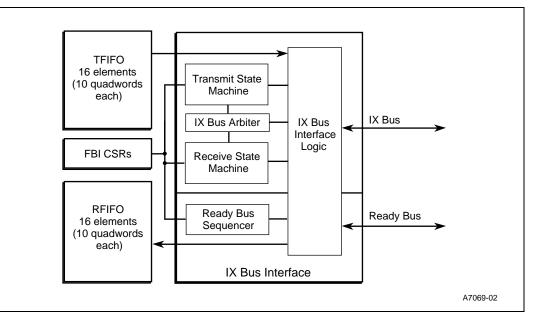

| 0.<br>6         | .6.4.2 Receive Request Format (RCV_REQ Register)                | 202   |

| 0.<br>6         | .6.4.3 Processing Receive Requests                              | 202   |

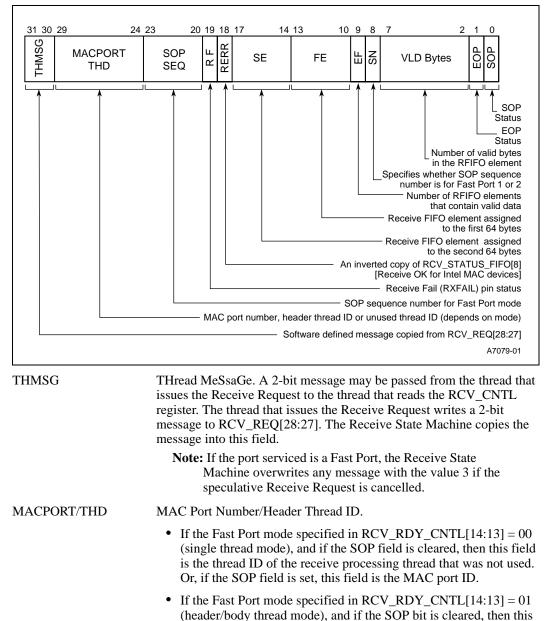

|                 | .6.4.4 Receive Data Control Information Format (RCV_CNTL        | .204  |

| 0.              | Register)                                                       | 206   |

| 6               | .6.4.5 Interpreting the Byte Enable Pins (FBE#[7:0])            |       |

|                 | .6.4.6 Reading the RFIFO                                        |       |

| 6.              | .6.4.7 Receive Scheduler Thread                                 | .213  |

|                 | ransmit State Machine and TFIFO - Transmitting Data on the      |       |

|                 | ( Bus                                                           | .215  |

|                 | .6.5.1 Initiating a Transmit Request (TFIFO Format)             |       |

|                 | .6.5.2 Transmitting TFIFO Data                                  |       |

|                 | ransmit Scheduler Thread                                        |       |

|                 | .6.6.1 Assigning a Transmit Thread - Examples                   |       |

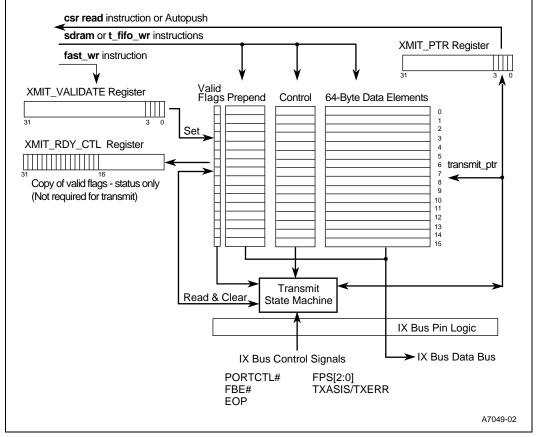

|                 | K Bus Arbiter                                                   |       |

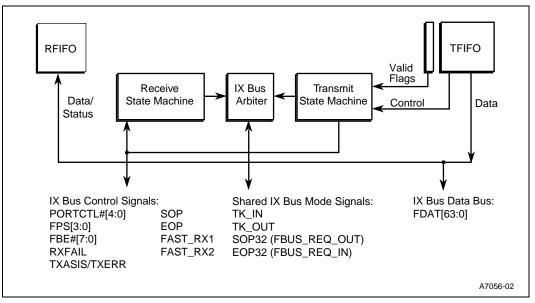

|                 | low Ports and Fast Ports                                        |       |

|                 | .6.8.1 Maintaining Packet Order                                 |       |

|                 | .6.8.2 Issuing Receive Requests                                 |       |

|                 | .6.8.3 Fast Port Modes                                          |       |

| 0.<br>6         | .6.8.4 Timing Considerations for Back-to-Back Reads             | 228   |

|                 | Specifications                                                  |       |

|                 | ancel                                                           |       |

|                 | eceive Fail                                                     |       |

|                 | eceive Frair                                                    |       |

| 0.7.3 N         |                                                                 | .231  |

|                 |                                                                 |       |

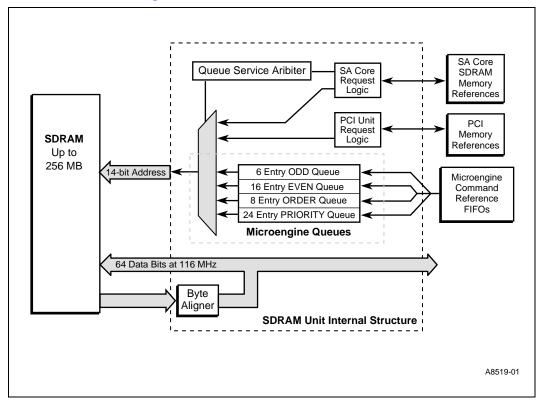

| 7.1 Overview    |                                                                 | . 233 |

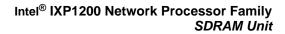

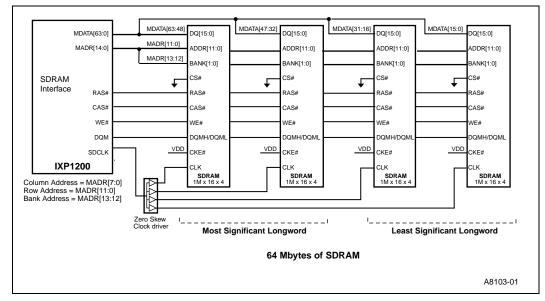

| 7.2 SDRAM B     | Bus Configurations                                              | .233  |

| 7.2.1 Ba        | ank, Row, and Column Pin Assignments                            | . 234 |

| 7.2.2 In        | nitializing the SDRAM Interface                                 | .235  |

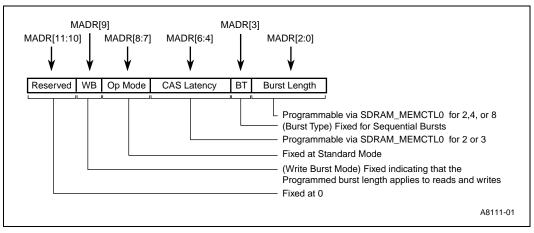

|                 | .2.2.1 Configuration Registers (SDRAM_MEMCTL0)                  |       |

|                 | DRAM Bus Commands                                               |       |

|                 | .2.3.1 No Operation (NOP)                                       |       |

|                 | .2.3.2 Load Mode Register                                       |       |

|                 | .2.3.3 Active                                                   |       |

|                 | .2.3.4 Read                                                     |       |

| 7.              | .2.3.5 Write                                                    | .239  |

| 7.              | .2.3.6 Burst Terminate                                          | 239   |

| 7.              | .2.3.7 Self Refresh                                             | . 239 |

| 7.              | .2.3.8 Precharge                                                | . 239 |

| 7.              | .2.3.9 Unsupported SDRAM Commands                               | . 240 |

| 7.3 Interfacing | g to the SDRAM Unit                                             | .240  |

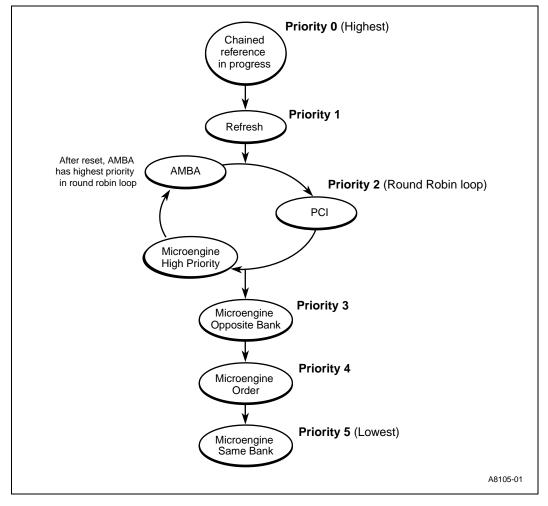

| 7.3.1 SI        | DRAM Command Service Priority Logic                             | .240  |

| 7.              | .3.1.1 Priority 0: Chained Referenced                           | .242  |

| 7.              | .3.1.2 Priority 1: Refresh Requests                             | .242  |

|                 | .3.1.3 Priority 2: Round Robin Requests                         | 212   |

|                 | .3.1.4 Priority 3 through 5: The Remaining Microengine Requests |       |

|      | 7.3.2          | Read-Modify-Write                                                                  | 243 |

|------|----------------|------------------------------------------------------------------------------------|-----|

|      | 7.3.3          | Chained References                                                                 | 243 |

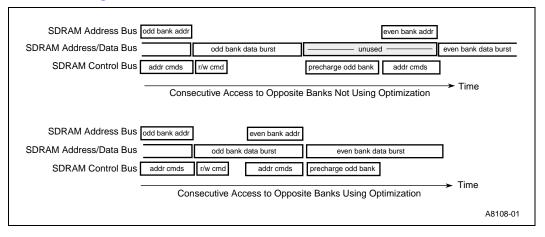

|      | 7.3.4          | Active Memory Optimization                                                         | 244 |

| 7.4  | Microer        | ngine SDRAM Transactions                                                           |     |

|      | 7.4.1          | Microengines Command Queues                                                        | 245 |

|      | 7.4.2          | SDRAM Byte Aligner                                                                 | 245 |

| 7.5  | PCI SD         | RAM Transactions                                                                   | 246 |

| 7.6  | Strong/        | ARM* Core SDRAM Transactions                                                       | 247 |

|      | 7.6.1          | StrongARM* Core and Microengine SDRAM Address Space                                | 247 |

|      |                | 7.6.1.1 SDRAM CSRs                                                                 |     |

|      |                | 7.6.1.2 SDRAM non-Prefetch Memory (256 Mbytes)                                     |     |

|      |                | 7.6.1.3 SDRAM Prefetch Memory (256 Mbytes)                                         |     |

|      |                | 7.6.1.4 Cache Flush Area (16 Kbytes)                                               |     |

| 7.7  | SDRAN          | I and the IX Bus Interface                                                         |     |

|      | 7.7.1          | SDRAM to TFIFO Operation                                                           |     |

|      | 7.7.2          | Receive FIFO to SDRAM Operation                                                    |     |

|      | 7.7.3          | SDRAM and IX Bus Data Path Operation                                               | 249 |

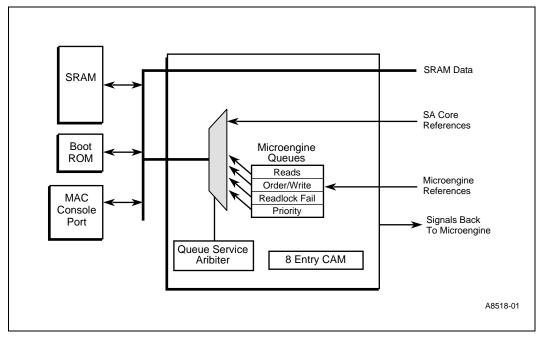

| SRAM | Unit           |                                                                                    | 251 |

| -    |                |                                                                                    | -   |

| 8.1  |                | ew                                                                                 |     |

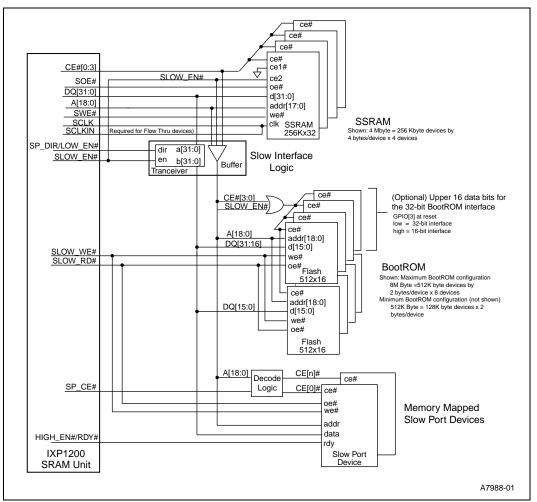

| 8.2  |                | Bus Configurations                                                                 |     |

| 8.3  |                | Address Space                                                                      |     |

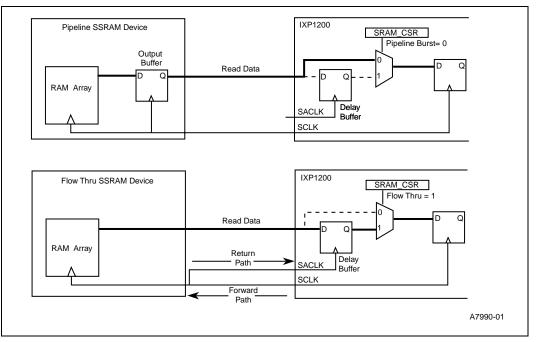

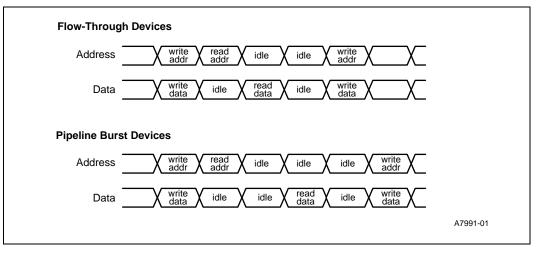

|      | 8.3.1          | Pipelined vs. Flow Thru SRAM Devices                                               |     |

| 8.4  |                | DM Address Space                                                                   |     |

| 8.5  |                | ort Address Space                                                                  |     |

| 8.6  |                | terface Logic                                                                      |     |

| 8.7  |                | CSRs                                                                               |     |

| 8.8  |                | ed SRAM Commands                                                                   |     |

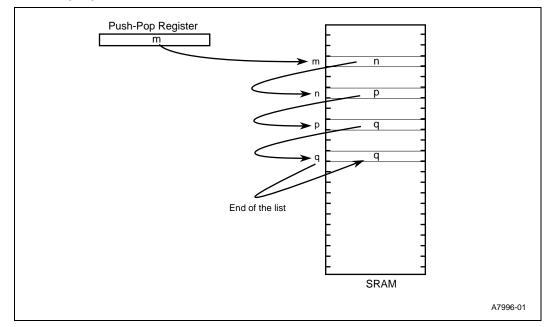

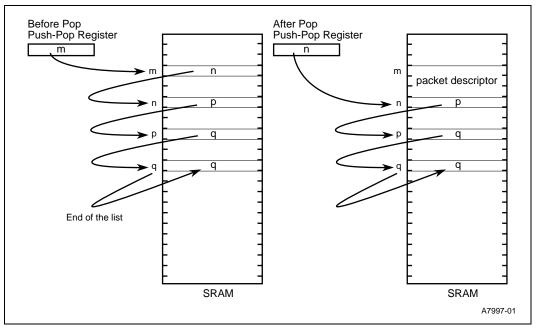

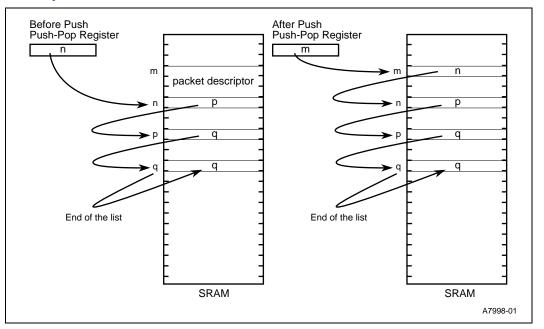

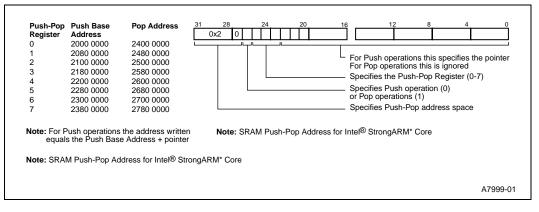

|      | 8.8.1          | Push Pop Registers                                                                 |     |

|      | 8.8.2          | SRAM Lock CAM                                                                      |     |

|      |                | 8.8.2.1 ReadLock and Microengines                                                  |     |

|      |                | 8.8.2.2 ReadLock and StrongARM* Core                                               |     |

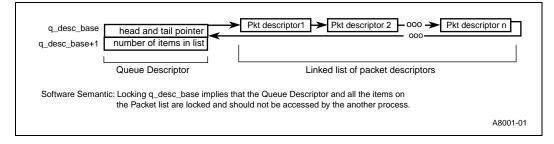

|      |                | 8.8.2.3 Maintaining Read_lock Order                                                | 264 |

|      |                | 8.8.2.4 Filling the Read_Lock Fail Queue<br>8.8.2.5 Application Example: Read_lock | 200 |

|      | 8.8.3          | Bit Test & Set / Bit Test & Clear                                                  |     |

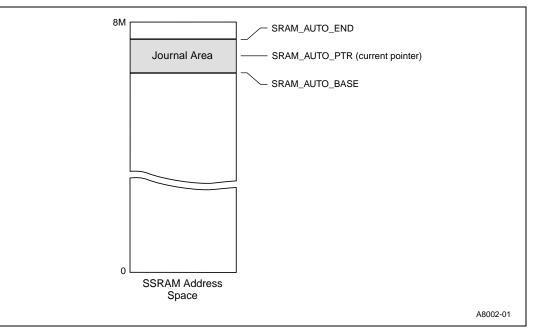

|      | 8.8.4          | SRAM Journaling                                                                    |     |

| 8.9  |                | sing to the SRAM Unit                                                              |     |

| 0.9  | 8.9.1          | SRAM Map                                                                           |     |

|      | 8.9.2          | Microengine SRAM Transactions                                                      |     |

|      | 8.9.2<br>8.9.3 | StrongARM* Core SRAM Transactions                                                  |     |

|      | 8.9.3<br>8.9.4 | SRAM Burst Count                                                                   |     |

|      | 8.9.4<br>8.9.5 | SRAM Burst Count                                                                   |     |

|      | 8.9.5<br>8.9.6 |                                                                                    |     |

|      | 0.9.0          | Read-Modify-Write                                                                  | 212 |

# **Figures**

| 2-1  | IXP1200 Block Diagram                                                   | .18  |

|------|-------------------------------------------------------------------------|------|

| 2-2  | Thread waiting for signal                                               | .22  |

| 2-3  | Thread synchronizing with signal                                        | . 22 |

| 2-4  | Context Swapping                                                        | .24  |

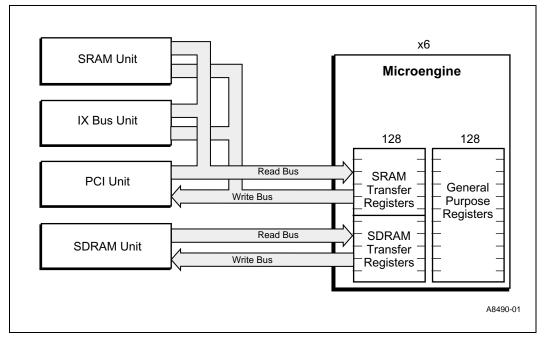

| 2-5  | Microengine Transfer Registers and internal data paths                  | .25  |

| 2-6  | Typical Packet Data Flow in the IXP1200 (Simplified)                    | . 27 |

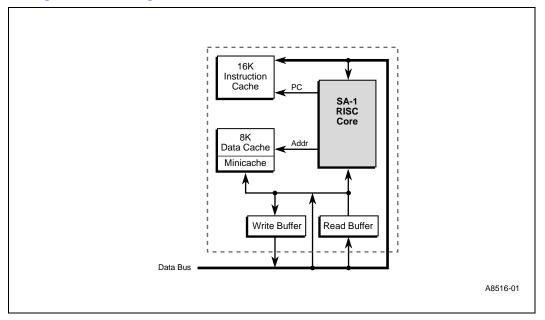

| 2-7  | StrongARM Block Diagram                                                 | .31  |

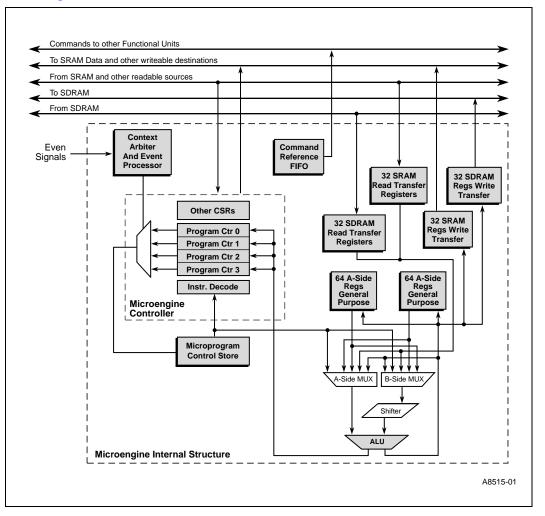

| 2-8  | Microengine internal structure                                          | . 33 |

| 2-9  | SRAM Unit external interfaces                                           | . 38 |

| 2-10 | SRAM Unit Block Diagram                                                 | . 38 |

| 2-11 | SDRAM Unit Block Diagram                                                | .41  |

| 2-12 | PCI Unit Block Diagram                                                  | .43  |

| 2-13 | IX Bus data flow                                                        | .45  |

| 2-14 | Simplified IX Bus Unit Block Diagram                                    | .46  |

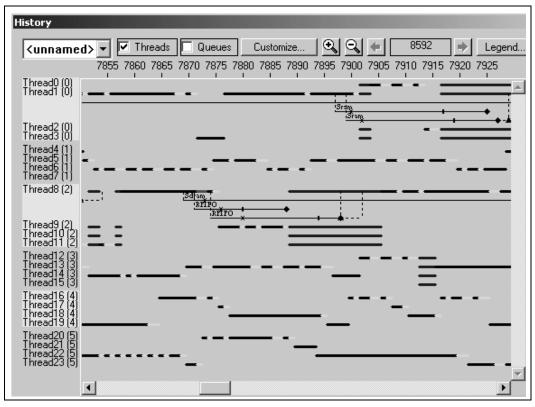

| 2-15 | Developer's Workbench - Thread History Display                          | . 50 |

| 3-1  | StrongARM* Core Memory Map                                              | .65  |

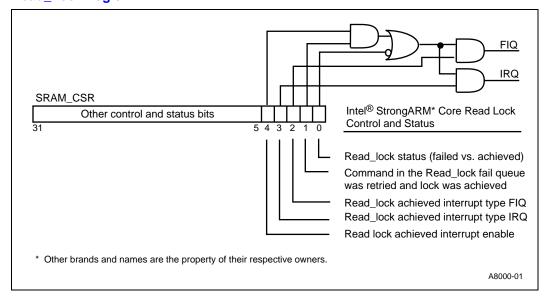

| 3-2  | FIQ and IRQ Interrupts                                                  | .67  |

| 3-3  | Timer Block Diagram                                                     | .70  |

| 4-1  | Microengine Block Diagram                                               |      |

| 4-2  | Class 3 Branch Decision                                                 | . 81 |

| 4-3  | Class 2 Branch Decision                                                 | . 82 |

| 4-4  | Class 1 Branch Decision                                                 | .83  |

| 4-5  | Postponed Branch Decision                                               |      |

| 4-6  | Execution States                                                        | . 87 |

| 4-7  | GPR Addressing                                                          | .90  |

| 4-8  | Transfer Register Addressing                                            |      |

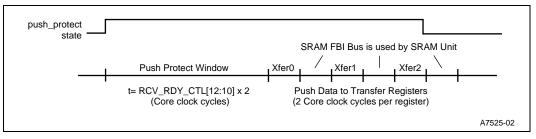

| 4-9  | Push Protect Timing                                                     |      |

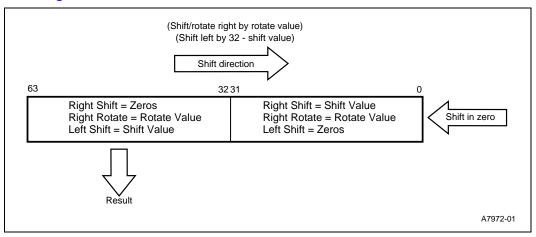

| 4-10 | Microengine Shift and Rotate Procedure                                  |      |

| 4-11 | Context Arbitration Policy                                              |      |

| 4-12 | Microengine References Using Transfer Registers                         | 103  |

| 4-13 | Command Bus Arbitration Policy                                          |      |

| 4-14 | Indirect References                                                     | 108  |

| 4-15 | Reading and Writing Local CSRs                                          | 112  |

| 4-16 | Load Bit Set and Find Bit Set Execution                                 | 114  |

| 4-17 | StrongARM* Interrupts                                                   | 116  |

| 4-18 | Inter-thread Signal Events                                              |      |

| 4-19 | StrongARM* Core and Microengine Communication                           |      |

| 5-1  | PCI Unit Block Diagram                                                  | 126  |

| 5-2  | PCI Bus Arbiter                                                         |      |

| 5-3  | DMA Descriptor Reads                                                    | 128  |

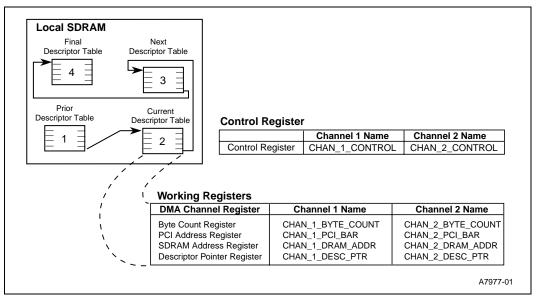

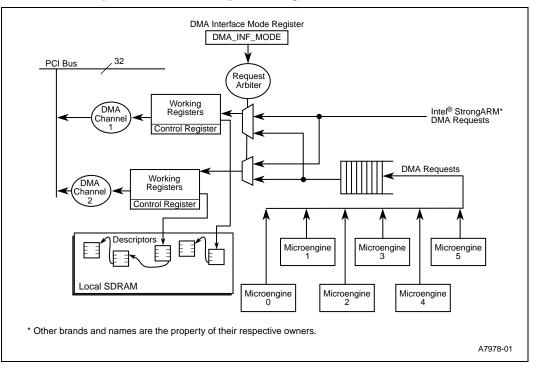

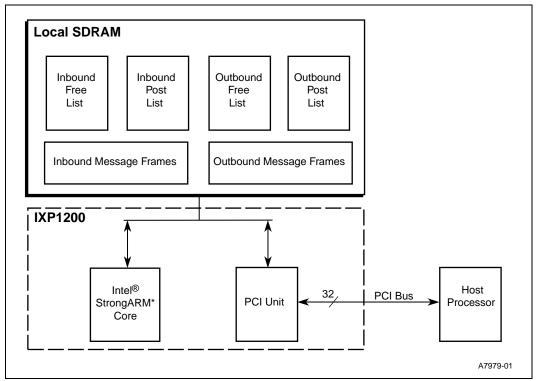

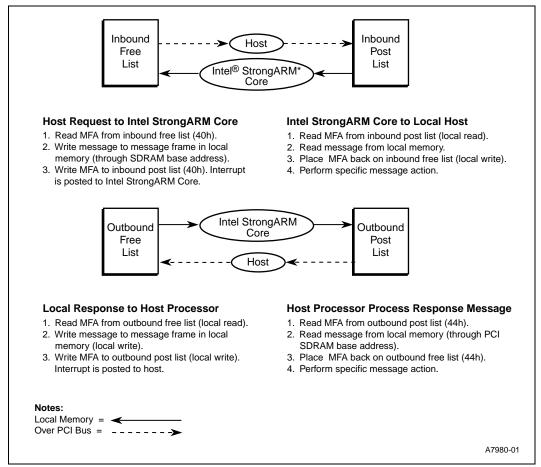

| 5-4  | DMA Channel Operations Initiated by Microengine                         |      |

| 5-5  | I <sub>2</sub> 0 Overview Diagram                                       |      |

| 5-6  | Circulation of MFAs                                                     |      |

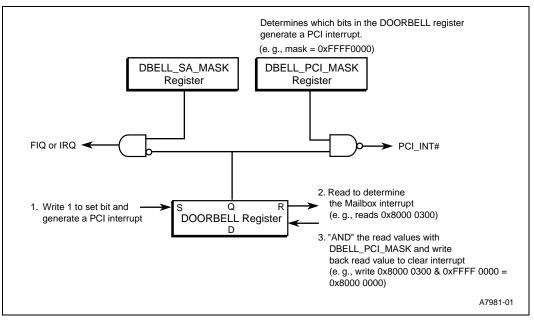

| 5-7  | How the StrongARM* Core Generates Doorbell Interrupts to a PCI Device   | 137  |

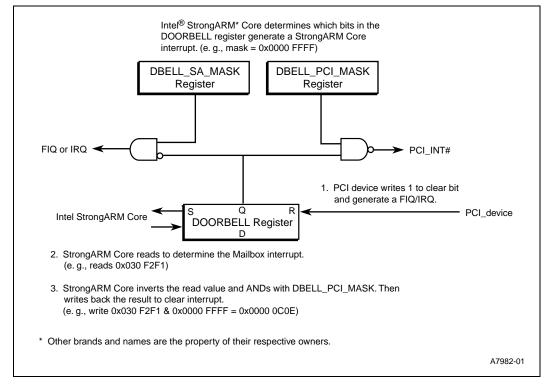

| 5-8  | How the PCI Device Generates Doorbell Interrupts to the StrongARM* Core |      |

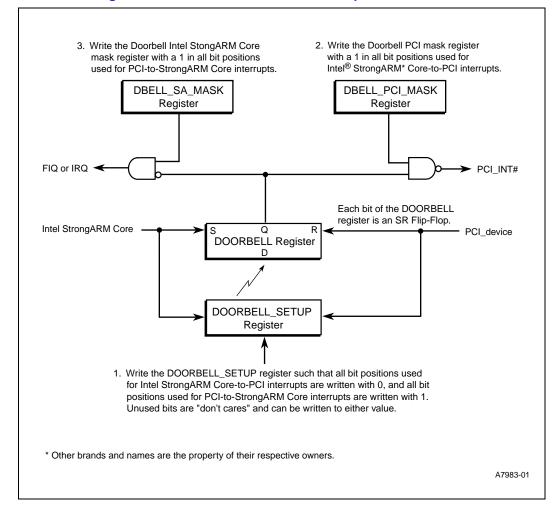

| 5-9  | How the StrongARM* Core Initializes Doorbell Interrupts                 |      |

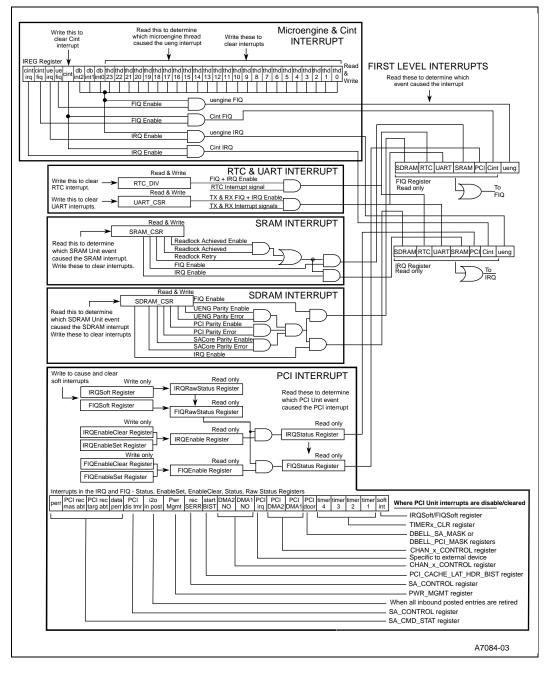

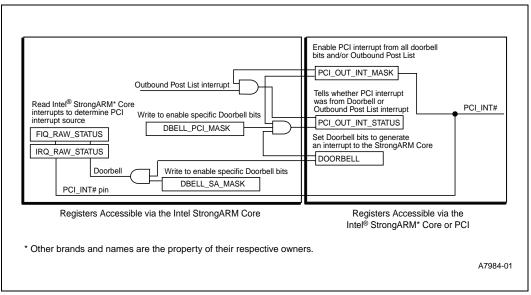

| 5-10 | PCI Interrupts                                                          | 140  |

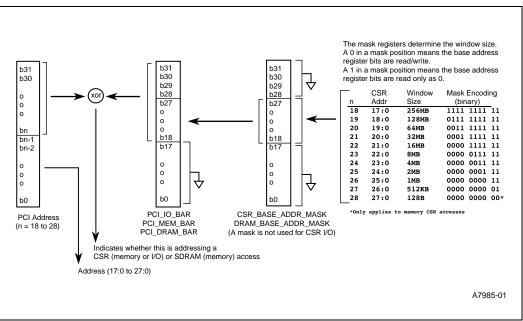

| 5-11 | Target Transactions - Internal Address Generation                       | 142  |

|      |                                                                         |      |

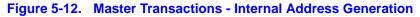

| 5-12 | Master Transactions - Internal Address Generation                    | 142 |

|------|----------------------------------------------------------------------|-----|

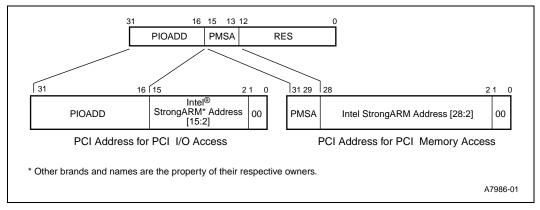

| 5-13 | Master Configuration Transactions                                    |     |

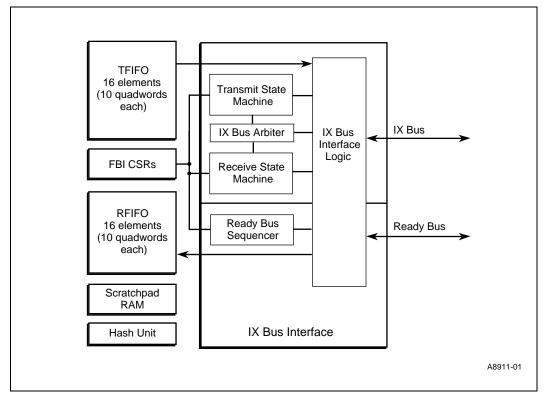

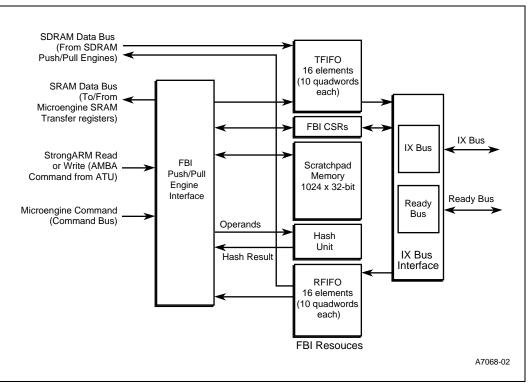

| 6-1  | FBI Unit Block Diagram                                               |     |

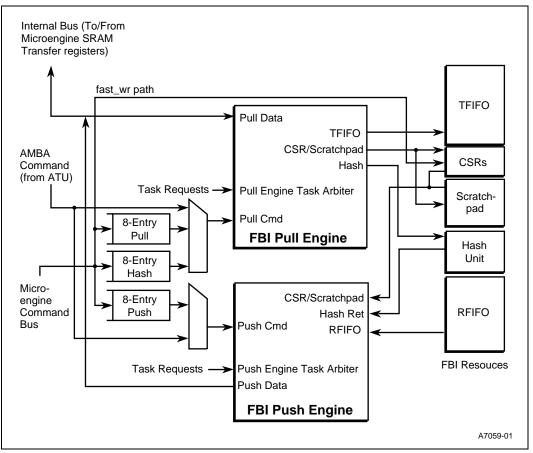

| 6-2  | Push/Pull Engine Interface Block Diagram                             |     |

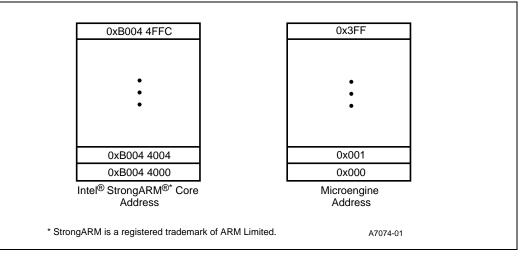

| 6-3  | Scratchpad Memory Mapping                                            |     |

| 6-4  | How SRAM Transfer Registers are Used                                 |     |

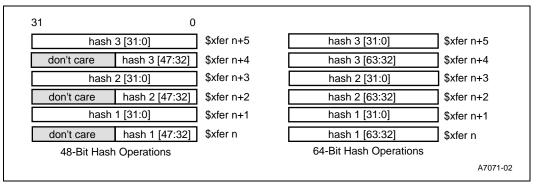

| 6-5  | Hash Operation Flow                                                  |     |

| 6-6  | IX Bus Interface                                                     |     |

| 6-7  | RCV_RDY_CTL Register                                                 | 175 |

| 6-8  | XMIT_RDY_CTL Register                                                | 175 |

| 6-9  | RDYBUS_TEMPLATE_CTL Register                                         |     |

| 6-10 | RDYBUS_SYNCH_COUNT_DEFAULT Register                                  | 176 |

| 6-11 | RDYBUS_TEMPLATE_PROGx Registers                                      | 177 |

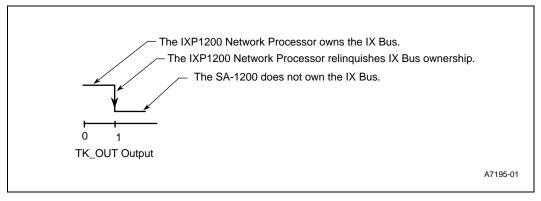

| 6-12 | TK_OUT Output                                                        | 178 |

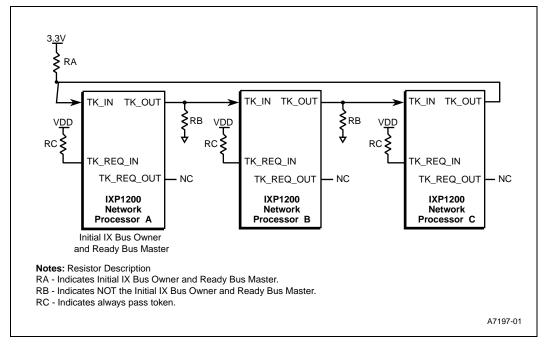

| 6-13 | Dual IXP1200 System Using Dynamic Token Passing                      | 179 |

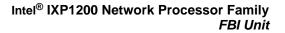

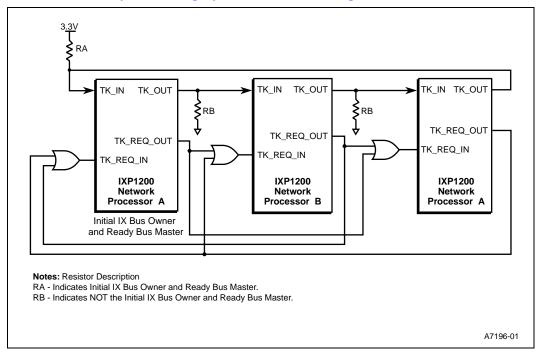

| 6-14 | Shared IXP1200 System Using Fixed Token Passing                      | 180 |

| 6-15 | Shared IXP1200 System Using Dynamic Token Passing                    |     |

| 6-16 | Receive State Machine Behavior when EOP Occurs on the Last IX Bus    |     |

|      | Data Cycle                                                           | 182 |

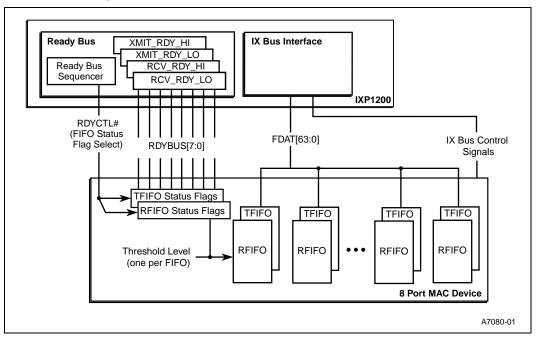

| 6-17 | Ready Bus Block Diagram                                              | 183 |

| 6-18 | Ready Bus Instruction Sequence                                       | 184 |

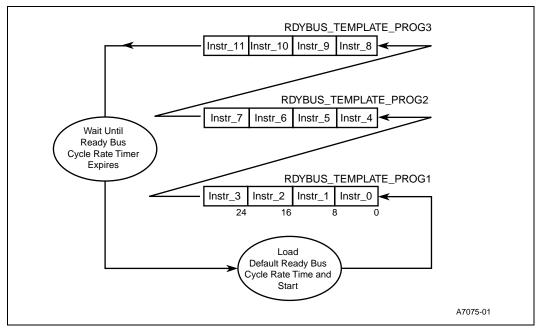

| 6-19 | MAC Device Sequencer Flow                                            | 190 |

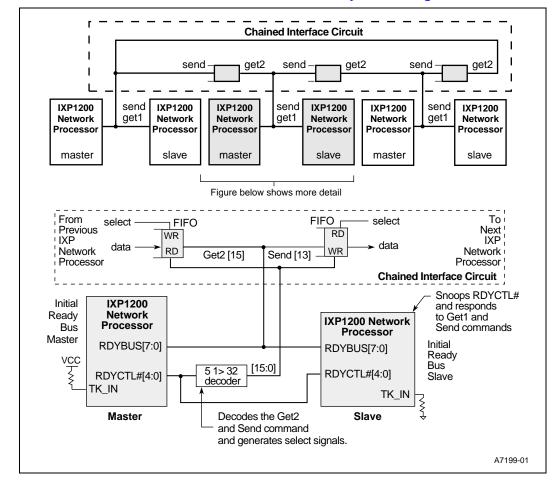

| 6-20 | Master-to-Slave and Master-to-Master Chained Ready Bus Configuration | 196 |

| 6-21 | Data Flow for Get and Send Instructions                              | 197 |

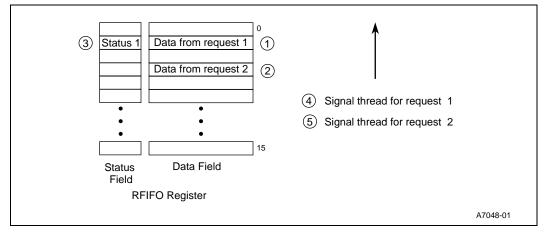

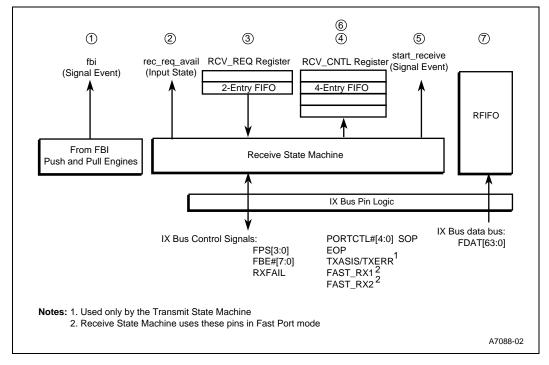

| 6-22 | Receive State Machine and RFIFO - Receiving Data From IX Bus         | 201 |

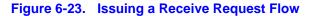

| 6-23 | Issuing a Receive Request Flow                                       | 202 |

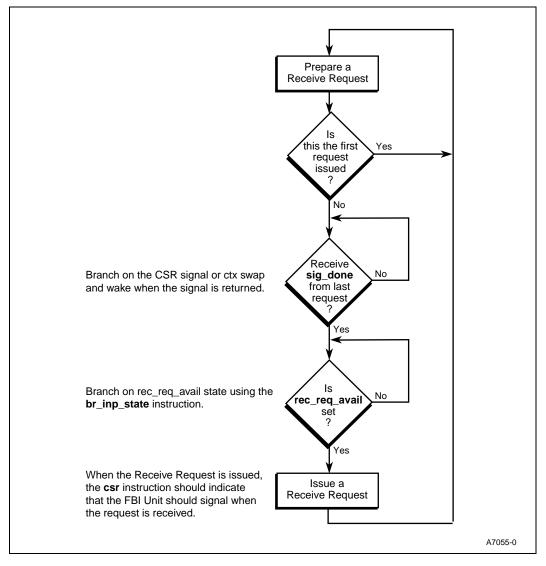

| 6-24 | RCV_REQ Register Format                                              | 203 |

| 6-25 | RCV_CNTL Register Format                                             | 206 |

| 6-26 | Quadword Addresses for RFIFO                                         |     |

| 6-27 | Format For 32-bit Unidirectional IX Bus Mode with 64-bit Status      | 212 |

| 6-28 | Format for All Other Modes                                           | 212 |

| 6-29 | Intel 21440 Multiport 10/100 Mbps Ethernet Controller Status Format  | 213 |

| 6-30 | Receive Scheduler Decision Time                                      | 214 |

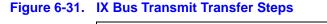

| 6-31 | IX Bus Transmit Transfer Steps                                       |     |

| 6-32 | TFIFO Format and Quadword Word Address                               | 217 |

| 6-33 | IX Bus Arbiter Flow                                                  | 220 |

| 6-34 | Slow Ports vs. Fast Ports                                            |     |

| 6-35 | Sequence Number Assignment for One Fast Port                         | 225 |

| 7-1  | SDRAM Interface External Connections                                 | 234 |

| 7-2  | SDRAM Addressing                                                     |     |

| 7-3  | Load Mode Register Command                                           | 238 |

| 7-4  | SDRAM Interfacing                                                    |     |

| 7-5  | Command Service Priority Logic Arbitration Policy                    | 241 |

| 7-6  | Bank Switching                                                       | 244 |

| 8-1  | SRAM External Connections                                            | 252 |

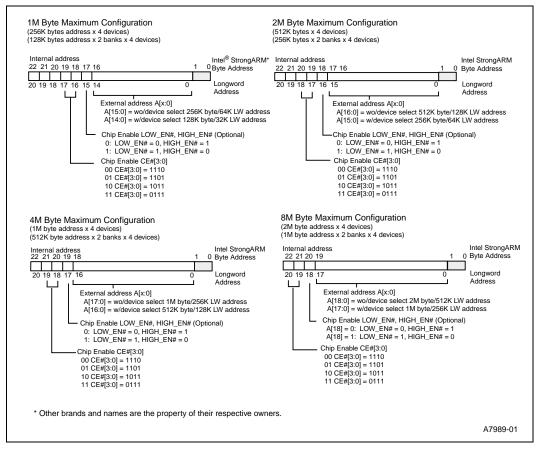

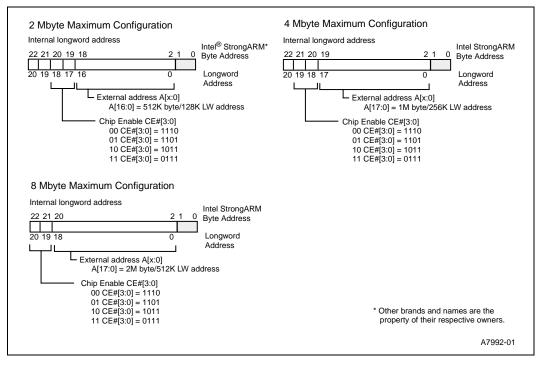

| 8-2  | Memory Configurations                                                |     |

| 8-3  | Pipelined vs. Flow Thru SSRAM Device                                 | 254 |

| 8-4  | Flow Thru Device                                                     |     |

| 8-5  | BootROM Addressing                                                   | 256 |

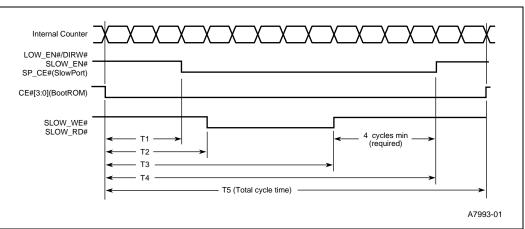

| 8-6  | BootROM Timing                                                       | 256 |

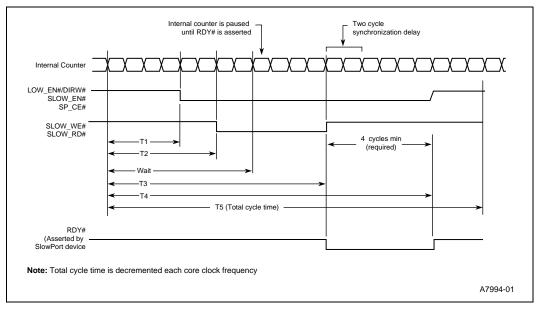

| 8-7  | SlowPort Timing               |  |

|------|-------------------------------|--|

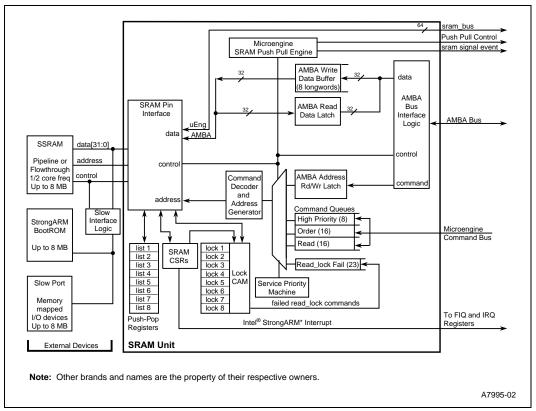

| 8-8  | SRAM Unit Block Diagram       |  |

| 8-9  | Push-Pop Operations           |  |

| 8-10 | Pop Operation                 |  |

| 8-11 | Push Operation                |  |

| 8-12 |                               |  |

| 8-13 | Read_Lock Logic               |  |

| 8-14 | Read_Lock Application         |  |

| 8-15 | SRAM Journaling Address Space |  |

|      |                               |  |

# Tables

| 1-1        | Data Terminology                                                | 16  |

|------------|-----------------------------------------------------------------|-----|

| 2-1        | Summary of StrongARM* Core Internal Connections                 | 32  |

| 2-2        | Summary of Microengine Internal Connections                     |     |

| 2-3        | Calculation of Internal and External Bandwidths                 |     |

| 2-4        | Summary of SRAM Unit Internal Connections                       | 40  |

| 2-5        | Summary of SDRAM Unit Internal Connections                      |     |

| 2-6        | Summary of PCI Unit internal connections                        |     |

| 2-7        | Summary of IX Bus Unit Internal Connections                     |     |

| 3-1        | Valid MMU, Dcache, and Write Buffer Combinations                |     |

| 3-2        | Effects of the Cacheable and Bufferable Bits on the Data Caches |     |

| 3-3        | StongARM Core instruction Timing                                |     |

| 3-4        | Exception Vectors                                               |     |

| 3-5        | UART Supported Data Formats                                     |     |

| 3-6        | RTC Registers                                                   |     |

| 3-7        | GPIO Pins and IX Bus Modes                                      |     |

| 4-1        | Summary of Microengine Instructions                             |     |

| 4-2        | Execution Pipeline                                              |     |

| 4-3        | Instructions Categorized by Class                               |     |

| 4-3<br>4-4 | Class 3 Instructions                                            |     |

| 4-4<br>4-5 | Class 2 Instructions                                            |     |

| 4-5<br>4-6 | Class 2 Instructions                                            |     |

| 4-0<br>4-7 |                                                                 |     |

|            | Transfer Register Usage (Solicited Access)                      |     |

| 4-8        | Transfer Register Usage (Unsolicited Access)                    |     |

| 4-9        | ALU Operations                                                  |     |

| 4-10       | ctx_swap Instructions                                           |     |

| 4-11       | Signal Event Request Methods                                    |     |

| 4-12       | Explicitly Requested Signal Events                              |     |

| 4-13       | Nonexplicit Signal Events                                       |     |

| 4-14       | Instructions Using Transfer Registers                           |     |

| 4-15       | Bus Utilization                                                 |     |

| 4-16       | Fast_wr 10-Bit Immediate Data                                   |     |

| 4-17       | Indirect Reference Instructions                                 |     |

| 4-18       | Local CSRs                                                      |     |

| 4-19       | Result Register Bits                                            |     |

| 4-20       | Journal Register Initialization Order                           |     |

| 5-1        | FIFO Pointers                                                   |     |

| 5-2        | Doorbell Interrupt Registers                                    |     |

| 5-3        | Doorbell Interrupt Functions                                    |     |

| 5-4        | Master Configuration Transactions                               | 143 |

| 6-1        | FBI Resources                                                   |     |

| 6-2        | FBI Push and Pull Task Priorities                               |     |

| 6-3        | Instructions Assigned to FBI Command Queues                     | 159 |

| 6-4        | 10-Bit Immediate Data                                           | 168 |

| 6-5        | Receive Request Registers                                       | 169 |

| 6-6        | Sequence Numbers Registers                                      |     |

| 6-7        | IX Bus Transmit Registers                                       |     |

| 6-8        | IX Bus and Ready Bus Configuration Registers                    |     |

| 6-9        | Ready Bus Control Registers                                     |     |

|            |                                                                 |     |

| 6-10 | Hash Unit Configurations Registers           |

|------|----------------------------------------------|

| 6-11 | FBI Interrupt/Signal Registers               |

| 6-12 | Thread Status Registers                      |

| 6-13 | Miscellaneous Registers                      |

| 6-14 | NOP Instruction Variations                   |

| 6-15 | rxrdy Instruction Variations                 |

| 6-16 | txrdy Instruction Variations                 |

| 6-17 | RxAutopush Instruction Variations            |

| 6-18 | TxAutopush Instruction Variations            |

| 6-19 | flwctl Instruction Variations                |

| 6-20 | Get1 Instruction Variations                  |

| 6-21 | Get2 Instruction Variations                  |

| 6-22 | send Instruction Variations                  |

| 6-23 | 64-bit Mode Endian Format                    |

| 6-24 | Byte Enable Signaling Based On Endian Format |

| 6-25 | 32-bit Mode Endian Format210                 |

| 6-26 | Byte Enable Signaling Based On Endian Format |

| 6-27 | Cancel States                                |

| 6-28 | Receive Fail States                          |

| 6-29 | Receive Error States                         |

| 7-1  | SDRAM Configurations                         |

| 7-2  | Programmable SDRAM Registers                 |

| 7-3  | Sequential Bursts                            |

| 7-4  | SDRAM Commands and Pin States238             |

| 7-5  | Command Queues                               |

| 7-6  | Data at Quadword Address N and N+1246        |

| 7-7  | Alignment Results                            |

| 7-8  | Memory Map for SDRAM Address Space           |

| 8-1  | Memory Map for SRAM Address Space            |

| 8-2  | SRAM Command Queue Sizes                     |

| 8-3  | Cacheable and Bufferable Address Spaces      |

| 8-4  | Burst Sizes                                  |

| 8-5  | SRAM Command Service Priority                |

# Introduction

## **1.1** About this Document

This document serves as the hardware reference manual for the Intel<sup>®</sup> IXP1200 Network Processor Family. This includes the IXP1200, IXP1240 and IXP1250. This book is intended for use by Developers and is organized as follows:

Section 2, Technical Introduction contains a hardware overview.

Section 3, StrongARM\* Core describes the operation of the embedded StrongARM\* core.

Section 4, Microengines describes the operation of the Microengines.

Section 5, PCI Unit describes the operation of the PCI Unit.

Section 6, FBI Unit describes the operation of the IX Bus Interface Unit.

Section 7, SDRAM Unit describes the operation of the SDRAM Unit.

Section 8, SRAM Unit describes the operation of the SRAM Unit.

### **1.2 Related Documentation**

Further information on the IXP1200 is available in the following documents:

*IXP1200 Network Processor Datasheet* - Contains summary information on the IXP1200 including a functional description, signal descriptions, electrical specifications, and mechanical specifications.

*IXP1240 Network Processor Datasheet* - Contains summary information on the IXP1240 including a functional description, signal descriptions, electrical specifications, and mechanical specifications.

*IXP1250 Network Processor Datasheet* - Contains summary information on the IXP1250 including a functional description, signal descriptions, electrical specifications, and mechanical specifications.

*IXP1200 Network Processor Family Microcode Programmer's Reference Manual* - Contains detailed programming information for designers.

*IXP1200 Network Processor Development Tools User's Guide* - Describes the IXP1200 Workbench and the development tools you can access through the use of the Workbench.

IXP1200 Network Processor Family Microcode Software Reference Manual - Contains detailed software technical information for designers.

*ARM\* Architecture Reference Manual.* Available from ARM. Contact: ARM Limited, 985 University Ave., Suite 5, Los Gatos, CA 95030. Phone: 408-399-5199. FAX: 408-399-8854. Email: info@arm.com. WWW: http://www.arm.com.

### 1.3 Conventions

The following conventions are used in this manual:

### 1.3.1 Data Terminology

#### Table 1-1.Data Terminology

| Term     | Words | Bytes | Bits |

|----------|-------|-------|------|

| Byte     | 1/2   | 1     | 8    |

| Word     | 1     | 2     | 16   |

| Longword | 2     | 4     | 32   |

| Quadword | 4     | 8     | 64   |

### 1.3.2 Definitions

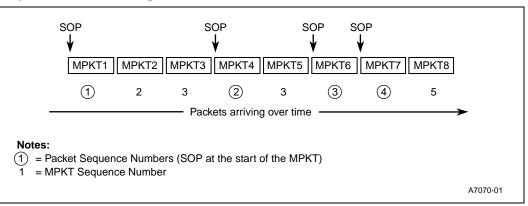

#### MPKT

The data read from a MAC device receive FIFO as the result of a single receive request to the receive state machine. Read in as 64 bytes.

#### Packet

The data framed between the assertion of an SOP signal and assertion of its associated EOP signal.

# **Technical Introduction**

# 2

This chapter is a relatively detailed introduction to the IXP1200 microarchitecture, and it's key features. It serves as a base from which the user can better understand the more detailed chapters that follow.

### 2.1 Overview

intel

The IXP1200 is an integrated Network Processor, comprised of a single StrongARM processor, six *Microengines*, standard memory interfaces, and high-speed bus interfaces. It is targeted at networking applications requiring a high degree of flexibility, programmability, scalability, performance, and low power consumption. The unique architecture of the IXP1200 affords the user a highly concurrent packet processing model, while keeping the programming model simple. This is accomplished by providing many features in hardware that simplify the programming model.

The IXP1200 allows the designer to implement in software, what was previously implemented in custom ASICs. This flexible, reprogrammable approach has many advantages, including faster development time, easier bug-fixes, the ability to add features to products after deployment in the field, and the ability to conform to standards that are not yet solidified.

The Microengines are custom processors implemented specifically for networking applications. They are especially well suited to high-speed data manipulation and movement. The Microengines being fully programmable processors, are able to examine packet contents at all levels of the networking stack. This makes them suitable not only for layer 2 and 3 switching/forwarding, but also for applications that require deeper inspection and manipulation of packet contents.

The IXP1200 has a number of noteworthy features that are described in more detail in Section 2.3, "Key Architectural Features:

- Multi-Processing allows multiple network packets to be processed in parallel.

- Distributed Data Storage architecture positions data close to where it's needed for faster access, in the Microengines.

- Hardware Multi-Threading allows each Microengine to process multiple packets with minimal context switching overhead.

- Active Memory Optimizations executes a series of memory requests in the most efficient manner, thereby increasing effective memory bandwidth.

- Multi-level Concurrency allows multiple packets to be processed simultaneously by overlapping the data accesses required to process one packet, with the compute cycles required to process another packet.

- · Block Data Movement efficient movement of large amounts of data.

- Scalability allows the architecture to scale with increasing processing demands.

## 2.2 IXP1200 Functional Units

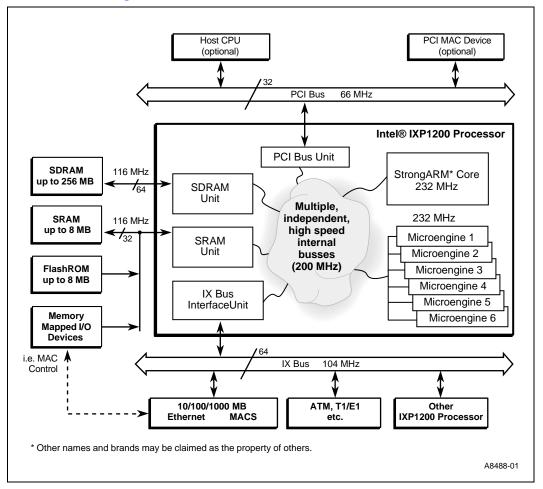

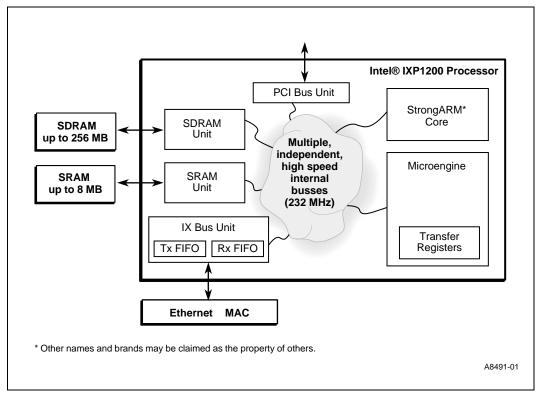

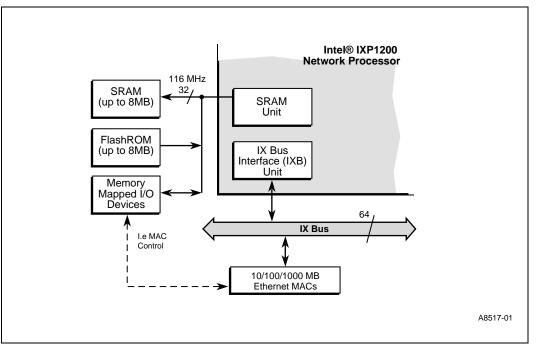

#### Figure 2-1. IXP1200 Block Diagram

Figure 2-1 is a simplified block diagram of the IXP1200 which shows the six main functional units. These functional units are described briefly below, and are described in more detail in the following sections. The internal busses are shown as a "cloud" here for the sake of simplicity. The many internal busses that connect the various functional units are described in more detail in Section 2.7, "Internal Architecture.

- StrongARM\* core A full 32-bit RISC processor core with integrated caches that can be used for management functions, running routing protocols, exception handling, and other tasks.

- Six Microengines These compact, efficient RISC engines can be used for any function requiring high-speed packet inspection, data manipulation, and data transfer. These are fully programmable 32-bit engines with a 5-stage execution pipeline and a large (256) register set. Hardware multithreading, and context-sensitive register windows enable very fast context switching.

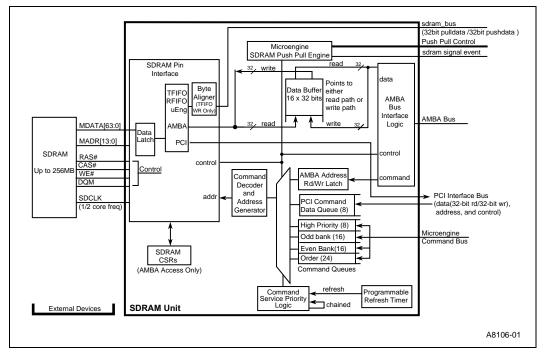

- SDRAM Unit A shared, intelligent memory interface that can be accessed by the StrongARM\* core, the Microengines, and devices on the PCI bus. A glue-less interface to

standard, low-cost SDRAMs. Capable of moving blocks of data between the SDRAM and the Microengines or the IX Bus Unit or devices on the PCI bus.

- SRAM Unit A shared, intelligent memory interface that is accessible by the StrongARM and the Microengines. A glue-less interface to standard pipelined and flowthrough SRAMs. Capable of moving blocks of data between the SRAM and the Microengines

- PCI Bus Interface Unit A standard interface that may be used to interface to other PCI devices, or another host processor.

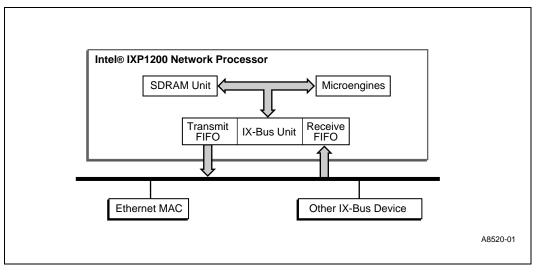

- IX Bus Unit An intelligent data movement engine controlled by the Microengines. Capable of transferring blocks of data between the IXP1200 and networking devices such as MACs and SARs. While the IX Bus Unit can perform many sophisticated data transfer operations internal to the IXP1200, the (external) IX Bus Interface itself is simple, and it is straightforward to design peripherals for it. The IX Bus is described in more detail in Section 2.7.6.

Other functions contained within the IXP1200 include:

- A hardware hashing unit (48 or 64 bit)

- An on-chip 4KByte Scratchpad RAM for storing globally accessible data, and passing messages between processors and between *threads*.

- On-chip Transmit and Receive FIFOs for buffering data on the IX Bus.

- Connecting the different functional units within the IXP1200 are a series of high speed busses that transfer data between the units. These are parallel data paths that operate independently of each other and increase the data throughput within the network processor.

- The IXP1200 also contains a UART for debug purposes; a number of counters that can be used for time-stamping, etc; and a number of features for inter-processor and inter-thread communication.

The IX Bus Interface is **the** high speed data flow interface to the IXP1200. Whereas the PCI interface is fast, and runs at up to 66 MHz, it is limited by the PCI bus protocol, and by the bus width. This does not preclude the PCI bus from being used as the main data path into and out of the IXP1200, but it should be remembered that there is no direct connection (internally) between the PCI Unit and the Microengines.

The IXP1200 has three types of memory resources available to the programmer: SRAM, SDRAM, and Scratchpad RAM. These memories vary in latency, size, and bandwidth. The advantage of having these three types of memories is that each of the memories operate in parallel, and the programmer may make use of each of these in areas suited to their characteristics.

For example, SDRAM memory is typically used for packet data storage and very large tables, whereas SRAM memory is used for table lookups where low latency is very important. Scratchpad RAM being internal to the IXP1200 is smaller, but with very low latency and is most often used for interprocess communication, and shared semaphores or counters.

### 2.3 Key Architectural Features

- **Multi-Processing** The six Microengines, plus the StrongARM make up the compute resources of the IXP1200. They share a common set of resources: SDRAM, SRAM, PCI, IX Bus, Scratchpad RAM, and a number of other functions (described later).

- **Distributed Data Storage Architecture** Each of the Microengines has its own local register file of 256 (32-bit) registers. 128 of these registers are *Transfer Registers*. The Microengines

have a load-store architecture. A Microengine cannot access data external to it. Instead, it must bring the data into its Transfer Registers, operate on it, and then write the data from the Transfer Registers out to its destination (i.e. SDRAM). Once the data is in its Transfer Registers, a Microengine has single-cycle access to it, thus greatly speeding up its processing capabilities. When data is not in its Transfer Registers, a Microengine can issue a Reference Command to fetch the required data, then "go to sleep" while waiting for the data to come back. This is where hardware multi-threading comes into play.

• Hardware Multi-Threading - Each of the Microengines actually has four Program Counters, and is designed to be able to support up to four Threads (also called Contexts). When one of the Threads is waiting for some data to be fetched, it can "go to sleep" and allow another Thread within the same Microengine to run. This allows four program threads to run on the same Microengine, thus utilizing the Microengine compute resources in a much more efficient fashion.

This leads to better silicon utilization, and lower power than an approach in which more Microengines are implemented, but without multi-threading. In a non-multi-threading design, Microengines end up spending a lot of time just waiting for the data to come back. Multi-threading in the IXP1200 is implemented in hardware, but controlled by software. Performing multi-threading in hardware makes zero overhead context switching possible, as described in Section 2.7.2, "Microengines.

- Active Memory Optimization Both the SDRAM and SRAM Units have a number of queues and optimization logic built in. This allows the six Microengines (actually the 24 Microengine threads) as well as the StrongARM to request read or write transfers from the memory units, and allows the memory units to intelligently determine the optimal order in which to carry out these requests. Though these Active Memory Optimizations are implemented in hardware, they are controlled by software on an instruction by instruction basis.

- **Concurrency** Due to the several independent data and control busses internal to the IXP1200, data can be moved simultaneously:

- between the SDRAM Unit and the Microengines or IX Bus Unit (in both directions: read and write, - simultaneously)

- between the SRAM Unit and the Microengines (in both directions: read and write, - simultaneously)

- between the SDRAM Unit and the PCI Unit

- between the IX Bus Unit and the Microengines

All these can occur simultaneously, and independently of each other. These are under software control, but implemented in hardware, so the programmer need not worry about the details. There are additional forms of concurrency in the IXP1200, which are described in more detail in Section 2.4.6.

- **Block Transfers** Due to the large register set on each of the Microengines, a single instruction can cause up to 64 bytes of data to flow from one functional unit to another, or up to 128 bytes of data to flow across the IX Bus. This makes better use of the Microengine compute resources, as well as reducing code size.

- Scalability The IXP1200 architecture implements scalability in a number of different dimensions. Firstly, the architecture is such, that future members of the IXP1200 family can add additional Microengines, while maintaining the same programming model. Secondly, future IXP network processors can increase the instruction store within the Microengines. Thirdly, multiple IXP1200s can be connected in a single design, allowing increased processing power or data bandwidth.

Connecting the six functional units are a number of very high-speed internal busses. These busses operate at the full core frequency (currently 232 MHz). The busses are detailed in the descriptions of the individual functional units in Section 2.7, "Internal Architecture, however, it should be noted here that there are separate Read and Write busses between some of the functional units allowing simultaneous transfers across these busses. Also, some of the functional units have separate, unshared busses connecting them (i.e. PCI Unit to SDRAM Unit). In addition to these internal busses which significantly improve the performance of the IXP1200, several of the functional units have their own DMA engines (called Push-Pull Engines). These Push-Pull Engines are transparent to the programmer, but serve as hardware DMA Controllers to move blocks of data between the functional units. The combination of multiple independent busses, the Microengines, and the Push-Pull Engines serve to move large amounts of data within the IXP1200 concurrently. Thus, internal data-path bottlenecks are removed. More detail on the functioning of the internal busses, as well as the Push-Pull Engines follows in a later section.

### 2.4 Some Architectural Concepts

The IXP1200 architecture introduces some new concepts, and also makes use of some existing concepts but uses them in novel ways. This section gives a broad overview of these concepts and how they work together to form the IXP1200 architecture. Understanding these concepts is key to understanding the IXP1200 architecture.

### 2.4.1 References

Standard microprocessors (such as the integrated StrongARM processor) access memory directly by issuing the memory address, and then waiting for the data to be returned. If the data is not returned immediately, wait states are generated and compute cycles are wasted.

In comparison, the Microengines utilize a form of addressing called *References*. To access data external to a Microengine, a Microengine executes a Reference Command, but does not have to wait for the data to come back. Instead it can do some other useful work by letting another program thread within the Microengine run.

While the Microengines have a set of local registers just like any other microprocessor, they do not have direct access to SDRAM, SRAM, and other resources that are not within the Microengine. A Microengine accesses its local registers in one clock cycle, however, to access resources that are not local to it, the Microengine issues Reference Commands (to bring data into the local registers).

Reference Commands are used to:

- · request a read or write from/to SDRAM

- request a read or write from/to SRAM

- request a read or write from/to on-chip Scratchpad RAM

- request a hashing operation to be performed on data in the transfer registers

- request data to be transferred over the IX Bus interface (to/from a device on the IX Bus)

- request data to be moved between SDRAM and the IX Bus Unit

- request data to be transferred between Microengine transfer registers and the IX Bus Unit

In general, anything that takes time to complete, is implemented through a Reference Command, and the Microengine need not wait for the transfer to complete.

### 2.4.2 Signals and Synchronization

Since a Microengine can issue a Reference Command but does not need to wait for the requested action to be completed, some means must be provided so that the Microengine may know when the requested task has been completed. To accomplish this, the different functional units (i.e. SRAM Unit, SDRAM Unit, etc.) have the ability to send signals back to the requesting Microengine indicating when the requested task has been completed.

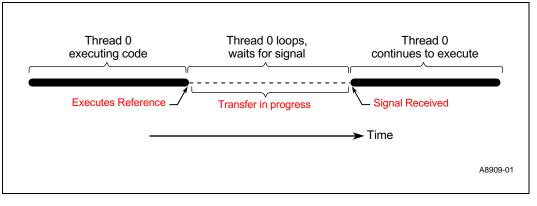

A Microengine can issue a Reference Command, and simply wait for the signal to be returned as shown in Figure 2-2.

#### Figure 2-2. Thread waiting for signal

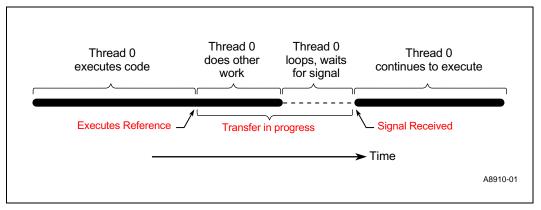

Or a Microengine can continue to execute instructions while the transfer is in progress and do some other useful work, and then later check to see if the signal has been received (shown in Figure 2-3).

#### Figure 2-3. Thread synchronizing with signal

Alternatively, the Microengine *Thread* can issue a Reference Command, and then *swap out* as described in the next section, and illustrated in Figure 2-4 "Context Swapping".

Signals are the primary method provided within the architecture to allow Microengine Threads to gain notification that events external to the Microengine have occurred. Signals are used not only to signify the completion of Reference Commands, but also for inter-processor and inter-thread communication. For example, threads may signal each other to indicate an event, or the StrongARM\* core may signal any of the Microengine threads.

Signals are not preemptive. They serve only to notify a thread of an event, or to enable a thread that is waiting for a signal.

### 2.4.3 Context Swapping and Threads

The Microengines utilize a feature called *Hardware Multithreading*. Each Microengine has four Program Counters, and supports four *Threads*. Each thread has its own Thread ID, and the IXP1200 hardware (i.e. the various functional units) are 'thread-aware'. When a Microengine Thread issues a Reference Command, the receiving functional unit (i.e. SDRAM Unit) recognizes which thread issued that command, and can send a completion signal specifically back to that thread. In this way, multiple threads within a Microengine can issue Reference Commands, and the completion signals are sent back to the specific threads that issued the commands in the first place. This is all done by the hardware, so the programmer need not worry about keeping track of Reference Commands, and the IXP1200 programming model remains simple, and easy to use.

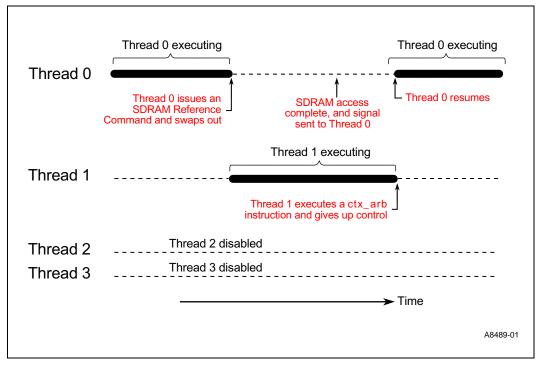

As mentioned above, a Microengine (actually, a Microengine thread) can issue a Reference Command, and then swap out, allowing another thread (within the same Microengine) to run. In this way, while one Microengine thread is waiting for data, or some operation to complete, another thread is allowed to run and complete some useful work (Figure 2-4). Since the functional units are thread aware, when a particular Reference Command is complete, the specific thread that issued the command is signalled, enabling it to 'wake up' and continue to run, since the data it was waiting for is now available

It should be noted that a thread does not simply "wake up" whenever it receives a signal. The Microengine architecture is not interrupt driven, and so signals *do not preempt* a thread that is already executing. Context switching occurs only when an executing thread *explicitly* gives up control. The ctx\_arb Microengine instruction allows the context arbiter to determine which thread runs next. In addition, the ctx\_arb option on Reference Commands issues the Reference Command and then allows context arbitration to take place. Context arbitration does not occur at any other time.

A thread that is swapped out and waiting for a signal is temporarily disabled (for arbitration) until the signal is received. The Microengine Context Arbiter is described in more detail in Microengine Section.

### 2.4.4 Some Examples

As an example, say Thread A (Microengine #1, Thread 2) is processing a packet header by doing a lookup in SRAM. Instead of waiting for the data to come back from SRAM, Thread A can continue to execute instructions, and begin to store the packet payload data to SDRAM. Later, when necessary, it can check to see if a signal has been received from the SRAM Unit so that it knows that the SRAM operation has been completed, and can then continue to process the header.

Alternatively, as an example that shows context swapping, say Thread A is doing a lookup in SRAM, and due to the nature of the algorithm, cannot continue processing till the data is available. In this case, Thread A would issue the SRAM Reference Command and swap out (all in one instruction). At this point, Thread B (Microengine #1, Thread 3) would execute its program, probably working on a different packet than Thread A. Later, when the SRAM Reference Command issued by Thread A completes, the SRAM Unit would send Thread A a signal, enabling it to 'wake up' and continue to execute its code where it left off. It should be noted that Thread A cannot begin executing code again until Thread B relinquishes control (swaps out explicitly).

Again, this is all accomplished in the hardware so that the programmer does not have to keep track of all the signals and Reference Commands that have been issued. The programmer treats each thread as a logically separate entity, simplifying the IXP1200 programming model. The result, however, is that the six Microengines, each with four logically separate threads, can be effectively executing 24 different programs. It is even possible (though not likely from a practical, implementation point of view) that each of the 24 threads can be working on a separate packet.

### 2.4.5 Local Data Storage and Block Transfers

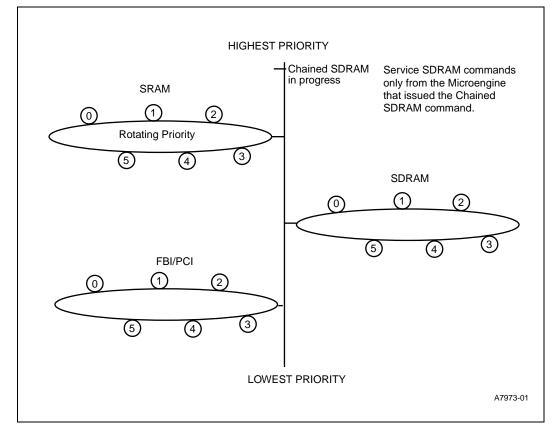

As shown in Figure 2-5 each of the Microengines contains 128 *Transfer Registers*. 64 of these are for transferring data between the Microengine and SDRAM (called SDRAM Transfer Registers), while the other 64 are for transferring data between the Microengine and the other functional units (called SRAM Transfer Registers). Though the SRAM Transfer Registers are named so, they transfer data between the Microengine and all the functional units (except SDRAM).