# Intel<sup>®</sup> IXP1200 Network Processor Family

**Development Tools User's Guide**

December, 2001

Order Number: 278302-009

# **Revision History**

| Revision Date | Revision | Description                                    |

|---------------|----------|------------------------------------------------|

| 7/30/99       | .5       | Beta 1 release.                                |

| 8/30/99       | 001      | Beta 2 release.                                |

| 11/5/99       | 002      | Beta 3 release.                                |

| 3/3/00        | 003      | Beta 4 release.                                |

| 6/2/00        | 004      | Version 1.0 release.                           |

| 10/2/00       | 005      | Version 1.1 release.                           |

| 12/20/00      | 006      | Version 1.2 release.                           |

| 5/21/01       | 007c     | Version 1.3 SDK release. (includes C Compiler) |

| 6/1/01        | 007      | Version 1.3 release.                           |

| 8/10/01       | 800      | Version 2.0 SDK                                |

| 12/5/01       | 009      | Version 2.01 SDK                               |

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The name of product may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it are furnished under license and may only be used or copied in accordance with the terms of the license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's Web site at http://www.intel.com.

Copyright © Intel Corporation, 2001

Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries

\*Other names and brands may be claimed as the property of others.

# int<sub>el</sub>。 *Contents*

| 1 | Ir            | itroduction                                       | 1-1  |

|---|---------------|---------------------------------------------------|------|

|   | 1.1           | About this Document                               | 1-1  |

|   | 1.2           | Related Documents                                 |      |

| 2 | D             | eveloper Workbench                                | 2-1  |

|   | 2.1           | overview                                          |      |

|   | 2.2           | Getting Help                                      |      |

|   | 2.3           | About the Graphical User Interface (GUI)          |      |

|   | 2.3.1         | About Windows, Toolbars, and Menus                |      |

|   | 2.3.2         | Hiding and Showing Windows and Toolbars           |      |

|   | 2.3.3         | Customizing Toolbars and Menus                    |      |

|   | 2.3.          | 0                                                 |      |

|   | 2.3.          |                                                   |      |

|   | 2.3.          |                                                   |      |

|   | 2.3.          |                                                   |      |

|   | 2.3.          |                                                   |      |

|   | 2.3.          | 5 5                                               |      |

|   |               | GUI Toolbar Configurations                        |      |

|   |               | About Projects                                    |      |

|   | 2.4.1         | Creating a New Project                            |      |

|   | 2.4.2         | Opening a Project                                 |      |

|   | 2.4.3         | Saving a Project                                  |      |

|   | 2.4.4         | Closing a Project                                 |      |

|   |               | Configuring the System                            |      |

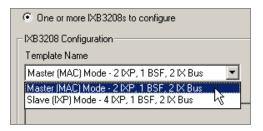

|   | 2.5.1         | Modifying the Chip Configuration                  |      |

|   |               | 1.1     Selecting Chip Type                       |      |

|   | ∠.5.<br>2.5.2 |                                                   |      |

|   | 2.5.2         |                                                   |      |

|   | 2.5.          |                                                   |      |

|   | 2.5.          |                                                   |      |

|   | 2.5.          |                                                   |      |

|   | 2.5.3         |                                                   |      |

|   | 2.5.          |                                                   |      |

|   | 2.5.          |                                                   |      |

|   | 2.5.4         |                                                   |      |

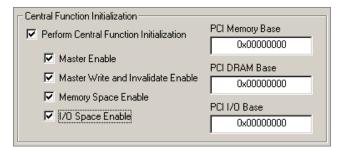

|   | 2.5.          | 4.1 About PCI Configuration                       | 2-19 |

|   | 2.5.          | 4.2 About PCI Configuration Space                 | 2-19 |

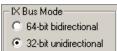

|   | 2.5.5         | Modifying the IX Bus Configuration 2              | 2-20 |

|   | 2.5.          | 5.1 Customizing Buses for Multichip Configuration | 2-20 |

|   | 2.6           | About the Project Workspace                       | 2-21 |

|   | 2.6.1         | About FileView                                    |      |

|   | 2.6.2         | About ThreadView2                                 |      |

|   | 2.6.          |                                                   |      |

|   | 2.6.          | 5                                                 |      |

|   | 2.6.3         | About InfoView                                    |      |

|   | 2.7           | Working with Files                                |      |

|   | 2.7.1         | Creating New Files                                | 2-23 |

| 2.7.2   | Opening Files                                    | 2-23 |

|---------|--------------------------------------------------|------|

| 2.7.3   | Closing Files                                    | 2-24 |

| 2.7.4   | Saving Files                                     | 2-24 |

| 2.7.5   | Saving Copies of Files                           | 2-25 |

| 2.7.6   | Saving All Files at Once                         | 2-25 |

|         | Working With File Windows                        |      |

|         | Printing Files                                   |      |

| 2.7.8.  |                                                  |      |

| 2.7.8.2 | 2 Previewing the Printed File                    |      |

| 2.7.8.3 |                                                  |      |

| 2.7.9   | Inserting Into and Removing Files from a Project | 2-27 |

| 2.7.9.1 | • • •                                            |      |

| 2.7.9.2 |                                                  |      |

| 2.7.10  | Editing Files.                                   | 2-27 |

| 2.7.11  | Bookmarks and Errors/Tags                        | 2-28 |

| 2.7.12  | About Find In Files                              | 2-28 |

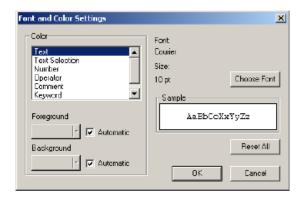

|         | About Fonts and Syntax Coloring                  |      |

|         | About Macros                                     |      |

|         | pout the Assembler                               |      |

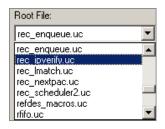

|         | About Root Files and Dependencies                |      |

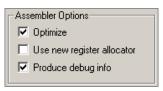

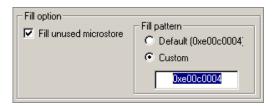

|         | Selecting Assembler Build Settings               |      |

| 2.8.2.  | • •                                              |      |

| 2.8.2.2 |                                                  |      |

| 2.8.2.3 |                                                  |      |

|         | Invoking the Assembler                           |      |

|         | About Assembly Errors                            |      |

|         | bout the Microengine C Compiler                  |      |

|         | Adding C Source Files to Your Project            |      |

|         | Selecting Compiler Build Settings                |      |

| 2.9.2.  |                                                  |      |

| 2.9.2.2 |                                                  |      |

| 2.9.2.3 |                                                  |      |

| 2.9.2.4 |                                                  |      |

| 2.9.2.5 |                                                  |      |

| 2.9.2.6 | 3 Selecting Compile Options                      | 2-38 |

| 2.9.2.7 | 7 Edit/Override                                  | 2-40 |

| 2.9.2.8 | 5 5                                              |      |

|         | Invoking the Compiler                            |      |

| 2.9.4   | Compilation Errors                               | 2-40 |

|         | pout the Linker                                  |      |

| 2.10.1  | Customizing a Build Configuration                | 2-41 |

| 2.10.2  | Changing Linker Settings                         | 2-42 |

| 2.11 De | ebugging                                         | 2-45 |

| 2.11.1  | Starting and Stopping the Debugger               | 2-46 |

| 2.11.2  | Changing Simulation Options                      | 2-46 |

| 2.11.2  |                                                  |      |

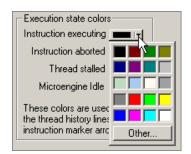

| 2.11.2  | 2.2 Changing the Colors for Execution State      | 2-47 |

| 2.11.2  |                                                  |      |

| 2.11.2  |                                                  |      |

| 2.11.2  |                                                  | 2-50 |

| 2.11.2  |                                                  |      |

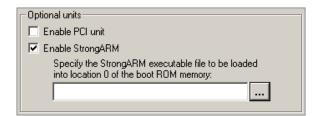

| 2.11.2  | 2.7 Enabling the PCI Interface                   | 2-50 |

| 2.11.2.8             | Enabling the PCI Transactor                                                  | 2-51 |

|----------------------|------------------------------------------------------------------------------|------|

| 2.11.2.9             | Enabling IX Bus Device Simulation                                            | 2-51 |

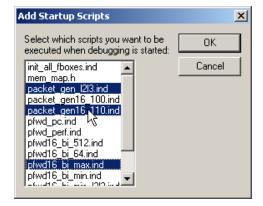

| 2.11.3 Exp           | orting the Startup Script                                                    | 2-51 |

| 2.11.4 Abo           | ut Hardware Options                                                          | 2-52 |

| 2.11.4.1             | Specifying Hardware Startup Options                                          | 2-52 |

| 2.11.4.2             | Specifying MAC Port Control                                                  |      |

| 2.11.5 Abo           | ut the Command Line Interface                                                |      |

|                      | ut Command Scripts                                                           |      |

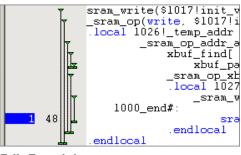

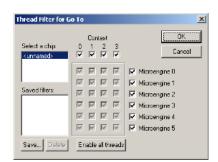

|                      | but Thread Windows                                                           |      |

|                      | Controlling Thread Window Activation                                         |      |

| 2.11.7.1<br>2.11.7.2 | About Thread Window Controls                                                 |      |

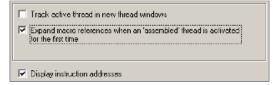

| 2.11.7.2             | Tracking the Active Thread                                                   |      |

| 2.11.7.3             |                                                                              |      |

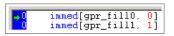

| 2.11.7.4             | Toggling Views (compiled threads only)                                       |      |

| 2.11.7.5             | Running to Cursor<br>Activating Thread Windows                               | 2-09 |

| 2.11.7.7             |                                                                              | 2-00 |

| 2.11.7.7             | Displaying, Expanding, and Collapsing Macros<br>(assembled threads only)2-61 |      |

| 2.11.7.8             |                                                                              | 0.60 |

| 2.11.7.8             | Displaying and Hiding Instruction Addresses<br>About Instruction Markers     |      |

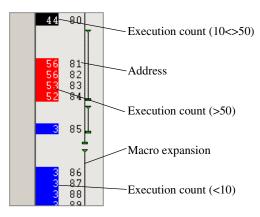

|                      | Viewing Instruction Execution in the Thread Window                           |      |

|                      | but Run Control—Simulation Mode                                              |      |

|                      |                                                                              |      |

| 2.11.8.1             | Single Stepping                                                              |      |

| 2.11.8.2             | Stepping Microengines                                                        |      |

| 2.11.8.3             | Stepping Over                                                                |      |

| 2.11.8.4             | Stepping Into (compiled threads only)                                        |      |

| 2.11.8.5             | Stepping Out (compiled threads only)                                         |      |

| 2.11.8.6             | Executing Multiple Cycles                                                    |      |

| 2.11.8.7<br>2.11.8.8 | Running to a Specific Cycle                                                  |      |

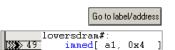

| 2.11.8.9             | Running to a Label or Microword Address                                      | 2-00 |

|                      | Running Indefinitely                                                         |      |

|                      | Stopping Execution<br>Resetting the Simulation                               |      |

|                      |                                                                              |      |

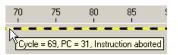

|                      | ut Run Control—Hardware Mode                                                 |      |

| 2.11.9.1             | About Hopping                                                                |      |

| 2.11.9.2             | Running Indefinitely                                                         |      |

| 2.11.9.3             | Stopping Execution                                                           |      |

| 2.11.9.4             | Resetting the Hardware                                                       |      |

|                      | ut Breakpoints                                                               |      |

|                      | Setting Breakpoints in Hardware Mode                                         |      |

|                      | About Breakpoint Markers                                                     |      |

|                      | Inserting and Removing Breakpoints                                           |      |

|                      | Enabling and Disabling Breakpoints                                           |      |

|                      | Changing Breakpoint Properties                                               |      |

|                      | playing Register Contents                                                    |      |

|                      | ut Data Watch                                                                |      |

| 2.11.12.1            | Data Watches in C Thread Windows                                             | 2-74 |

|                      | Entering a New Data Watch                                                    |      |

|                      | Watching Control and Status Registers and Pins                               |      |

|                      | Watching General Purpose and Transfer Registers                              |      |

|                      | Deleting a Data Watch                                                        |      |

|                      | Changing a Data Watch                                                        |      |

| 2.11.12.7            | Changing the Data Watch Radix                                                | 2-77 |

| 2.11.12.8            | Depositing Data                                                              | 2-77 |

| 2.11.12.9 Breaking on Data Changes                              |       |

|-----------------------------------------------------------------|-------|

| 2.11.13 About Memory Watch                                      |       |

| 2.11.13.1 Entering a New Memory Watch                           |       |

| 2.11.13.2 Adding a Memory Watch                                 |       |

| 2.11.13.3 Deleting a Memory Watch                               |       |

| 2.11.13.4 Changing a Memory Watch                               | 2-80  |

| 2.11.13.5 Changing the Memory Watch Address Radix               |       |

| 2.11.13.6 Changing the Memory Watch Value Radix                 |       |

| 2.11.13.7 Depositing Memory Data                                |       |

| 2.11.13.7 Depositing Memory Data                                |       |

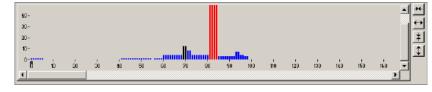

|                                                                 |       |

| 2.11.14.1 Changing Execution Count Ranges and Colors            |       |

| 2.11.14.2 Displaying and Hiding Instruction Addresses           |       |

| 2.11.14.3 About Instruction Markers                             |       |

| 2.11.14.4 Miscellaneous Controls                                |       |

| 2.11.14.5 Scaling the Bar Graph                                 |       |

| 2.11.14.6 Resetting Execution Counts                            |       |

| 2.11.15 About Performance Statistics                            |       |

| 2.11.15.1 Displaying Statistics                                 | 2-84  |

| 2.11.15.2 Resetting Statistics                                  | 2-85  |

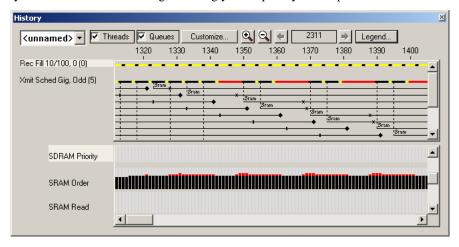

| 2.11.16 About Thread and Queue History                          |       |

| 2.11.16.1 Displaying the History Window                         |       |

| 2.11.16.2 Scaling the Display                                   |       |

| 2.11.16.3 Displaying Thread History Lines                       |       |

| 2.11.16.4 Displaying Code Labels                                |       |

| 2.11.16.5 About Reference History                               |       |

| 2.11.16.6 Displaying References                                 |       |

| 2.11.16.7 Changing Thread History Colors                        |       |

| 2.11.16.8 Displaying the History Legend                         |       |

| 2.11.16.9 Tracing Instruction Execution                         | 2-90  |

| 2.11.16.10 About Queue History                                  |       |

| 2.11.16.11 About History Collecting                             |       |

| 2.11.17 About Queue Status                                      |       |

|                                                                 |       |

| 2.11.17.1 About Queue Status History                            |       |

| 2.11.17.2 Setting Queue Breakpoints.                            |       |

| 2.11.18 About Thread Status                                     |       |

| 2.11.19 About IX Bus Device Simulation                          |       |

| 2.11.19.1 Configuring IX Bus Devices                            |       |

| 2.11.20 About Data Streams                                      |       |

| 2.11.20.1 Creating and Editing a Data Stream                    | 2-99  |

| 2.11.20.2 Deleting a Data Stream                                |       |

| 2.11.20.3 Importing a Data Stream                               |       |

| 2.11.20.4 Copying a Data Stream                                 |       |

| 2.11.20.5 Assigning an IX Bus Device Port                       |       |

| 2.11.21 Creating and Editing Different Data Streams Types       |       |

| 2.11.21.1 Creating and Editing an ATM Data Stream               |       |

| 2.11.21.2 Creating and Editing a Custom Ethernet IP Data Stream |       |

| 2.11.21.3 Creating and Editing an Ethernet IP Data Stream       |       |

| 2.11.21.4 Creating and Editing an Ethernet TCP/IP Data Stream   | 2-105 |

| 2.11.21.5 Creating and Editing a PPP TCP/IP Data Stream         |       |

| 2.11.21.6 Creating an IP Packet Pool                            | 2.107 |

| 2.11.21.7 Specifying a Custom Header                            |       |

| 2.11.21.7 Specifying a Custom fleader                           |       |

| 2.11.21.9 Specifying an IP Header                               |       |

|                                                                 |       |

| 2.11.21.10Specifying a TCP Header 2-1                           |     |

|-----------------------------------------------------------------|-----|

| 2.11.21.11 Specifying a PPP Header2-1                           |     |

| 2.11.21.12 Specifying a Data Payload2-1                         |     |

| 2.11.21.13Specifying Frame Size2-1                              |     |

| 2.11.21.14Assigning I/O to Device Ports2-1                      |     |

| 2.11.22 About Network Traffic Simulation DLLs2-1                |     |

| 2.11.23 About IX Bus Device Simulation Options2-1               |     |

| 2.11.23.1 About Miscellaneous Options2-1                        |     |

| 2.11.23.2 About Logging2-1                                      |     |

| 2.11.23.3 About Stop Control2-1                                 |     |

| 2.11.23.4 About the IX Bus Device Status Window2-1              |     |

| 2.11.24 About Debug Configuration2-1                            |     |

| 2.11.24.1 Setting Up Local Simulation with No Foreign Model     |     |

| 2.11.24.2 Setting Up Local Simulation with Local Foreign Model  |     |

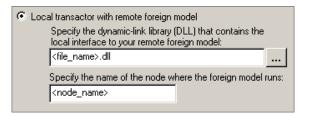

| 2.11.24.3 Setting Up Local Simulation with Remote Foreign Model |     |

| 2.11.24.4 Installing PortMapper2-1                              |     |

| 2.11.24.5 Setting up Hardware Debug2-1                          |     |

| 2.12 Running in Batch Mode2-1                                   |     |

| 2.13 An Exercise in Using the Workbench2-1                      | 23  |

| 3 Assembler                                                     | 3-1 |

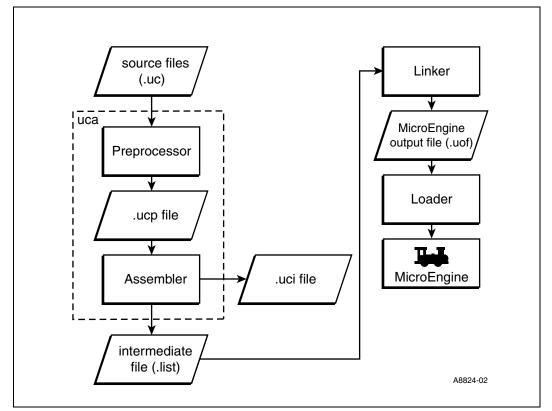

| 3.1 Assembly Process                                            |     |

|                                                                 |     |

| 3.1.1 Command Line Arguments                                    |     |

| 3.1.2 Assembler Steps                                           |     |

| 3.1.3 Case Sensitivity                                          |     |

| 3.1.4 Assembler Optimizations                                   |     |

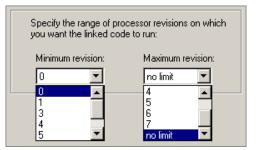

| 3.1.5 Processor Revision                                        | 3-4 |

| 4 Microengine C Compiler 4                                      |     |

| 4.1 The Command Line                                            | 4-1 |

| 4.2 Supported Compilations                                      | 4-1 |

| 4.3 Supported Option Switches                                   | 4-2 |

| 4.4 Compiler Steps                                              | 4-3 |

| 4.5 Case Sensitivity                                            | 4-3 |

| 5 Linker                                                        | = 1 |

|                                                                 |     |

| 5.1 About the Linker                                            |     |

| 5.1.1 Configuration and Data Accessed by the Linker             |     |

| 5.1.2 Shared Address Update (Flow)                              |     |

| 5.2 Microengine Image Linker (UCLD)                             |     |

| 5.3 Generating a Microengine Application                        |     |

| 5.4 Syntax Definitions                                          |     |

| 5.4.1 Image Name Definition                                     | 5-3 |

| 5.4.2 Import Variable Definition                                | 5-3 |

| 5.4.3 Microengine Assignment                                    | 5-4 |

| 5.4.4 Thread Type Definition                                    | 5-4 |

| 5.4.5 Code Entry Point Definition                               |     |

| 5.4.6 Export Function Definition                                |     |

| 5.5 Examples                                                    |     |

| 5.5.1 Uca Source File (*.uc) Example                            |     |

| 5.5.2 Uca Output File (*.list) Example                          |     |

| 5.6 Microcode Object File (UOF) Format                          |     |

|                                                                 | - • |

| 5.6.1  | FileChunkId Type: UOF_OBJS                        | 5-7  |

|--------|---------------------------------------------------|------|

| 5.6.2  | UOF Objld Types: UOF_STRT, UOF_GTID, and UOF_IMAG | 5-7  |

| 5.6.3  | FileChunkId Type: DBG_OBJS                        |      |

| 5.6.4  | DBG Chunkld Types: DBG_STRT, DBG_IMAG             |      |

| 6 T    | ransactor                                         | 6-1  |

|        |                                                   |      |

| 6.1    | Overview                                          |      |

| 6.2    | Invoking the Transactor                           |      |

| 6.3    | Command Interface                                 |      |

| 6.4    | IXP1200 Transactor Commands                       |      |

| 6.4.1  |                                                   |      |

| 6.4.2  | bank_analysis                                     |      |

| 6.4.3  | chip                                              |      |

| 6.4.4  | close                                             |      |

| 6.4.5  | config                                            |      |

| 6.4.6  | connect                                           |      |

| 6.4.7  | debug                                             |      |

| 6.4.8  | #define                                           |      |

| 6.4.9  | deposit                                           |      |

| 6.4.10 |                                                   |      |

| 6.4.11 |                                                   |      |

| 6.4.12 |                                                   |      |

| 6.4.13 | 3 examine                                         | 6-10 |

| 6.4.14 | 1 exit                                            | 6-11 |

| 6.4.15 | 5 fbox                                            | 6-11 |

| 6.4.16 | 6 go_clk_domain                                   | 6-12 |

| 6.4.17 | 7 go                                              | 6-12 |

| 6.4.18 | 3 goto                                            | 6-13 |

| 6.4.19 | 🤊 help                                            | 6-14 |

| 6.4.20 | ) #ifdef                                          | 6-15 |

| 6.4.21 | I #ifndef                                         | 6-15 |

| 6.4.22 | 2 init                                            | 6-15 |

| 6.4.23 | 3 load_bin_file                                   | 6-15 |

| 6.4.24 | 1 load_list_file                                  | 6-16 |

| 6.4.25 | 5 load uc                                         | 6-16 |

| 6.4.26 | 6 load uof file                                   | 6-16 |

| 6.4.27 | 7 log                                             | 6-17 |

| 6.4.28 | 3 mem init                                        |      |

| 6.4.29 | 9 path                                            | 6-17 |

|        | ) restore                                         |      |

|        | l return                                          |      |

| 6.4.32 | 2 save                                            |      |

|        | 3 set_clk_freq                                    |      |

|        | sim_reset                                         |      |

|        | 5 statistics                                      |      |

|        | 6 time                                            |      |

|        | 7 trace                                           |      |

|        | 3 ubreak                                          |      |

|        | 9 uca                                             |      |

|        | ) #undef                                          |      |

| 6.4.41 vers          | sion                                                                          | 6-21 |

|----------------------|-------------------------------------------------------------------------------|------|

|                      | ch                                                                            |      |

| 6.5 C Inte           | erpreter                                                                      | 6-22 |

|                      | cros                                                                          |      |

| 6.5.2 Pre            | defined C Functions                                                           | 6-24 |

| 6.5.2.1              | add_bus_client(bus_name, client_name)                                         | 6-24 |

| 6.5.2.2              | alloc_array(array_state_name, struct_name, array_length)                      |      |

| 6.5.2.3              | alloc_list(array_state_name, struct_name, list_length, flink_spec, blink_spec |      |

|                      |                                                                               | 6-25 |

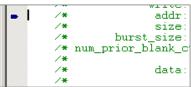

| 6.5.2.4              | amba_add_req(chip_name, write, addr, size, burst_size, num_prior_blank_c      |      |

|                      | data])                                                                        |      |

| 6.5.2.5              | cmd(quoted_cmd_string)                                                        | 6-26 |

| 6.5.2.6              | env_var(char *environment_variable)                                           |      |

| 6.5.2.7              | field(state_name, field_msb, field_lsb)                                       | 6-26 |

| 6.5.2.8              | field_insert(state_name, insertion_data, field_msb, field_lsb)                |      |

| 6.5.2.9              | fprintf(file_name, fmt,)                                                      |      |

| 6.5.2.10<br>6.5.2.11 | gui()<br>pcit_add_req( slave_nbr, cmd, address, byte, burst, delay, data)     |      |

| 6.5.2.11             | pcit_add_req( slave_nbr, cnid, address, byte, burst, delay, data)             | 6.26 |

| 6.5.2.12             | pcit_slave_addi( slave_nbr, slave, len)                                       |      |

| 6.5.2.13             | pcit_slave_read( slave_nbr, io_space, address)                                |      |

| 6.5.2.15             | printf(const char *format,)                                                   |      |

| 6.5.2.16             | rand(bound1, bound2)                                                          |      |

| 6.5.2.17             | rec error(fmt,).                                                              |      |

| 6.5.2.18             | seed()                                                                        |      |

| 6.5.2.19             | set_bus_validity_checks(bus, min_dead_cyc_wrn_thrsh, min_dead_cyc_err         |      |

|                      | max_dead_cyc_wrn_thrsh, max_dead_cyc_err_thrsh)                               | _    |

|                      |                                                                               | 6-27 |

| 6.5.2.20             | srand(number)                                                                 |      |

| 6.5.2.21             | state_type(var_name)                                                          |      |

| 6.5.2.22             | system(char *shell_cmd)                                                       |      |

| 6.5.2.23             | uaddr(control_store_state, label_name)                                        |      |

| 6.5.2.24             | uninitialized()                                                               |      |

| 6.5.2.25             | valid_elements(array_state_name)                                              |      |

|                      | gging                                                                         |      |

|                      | porting of Debugging Information                                              |      |

| 6.6.2 Cor            | nmon Execution Pipeline Stage Format                                          |      |

| 6.6.2.1              | Execution Pipeline Stage 4 - Write the Result                                 |      |

| 6.6.2.2              | Execution Pipeline Stage 3 - Perform ALU Shift, Decode Instruction            |      |

| 6.6.2.3              | Execution Pipeline Stage 2 - Look Up Operands                                 |      |

| 6.6.2.4              | Execution Pipeline Stage 1 - Decode Instruction                               |      |

| 6.6.2.5              | Execution Pipeline Stage 0 - Read Instruction                                 |      |

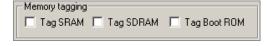

|                      | mory Tagging                                                                  |      |

|                      | tch                                                                           |      |

|                      | akpoints                                                                      |      |

|                      | e and Restore                                                                 |      |

| 6.6.7 Log            | ging A Simulation Session                                                     | 6-34 |

| 6.7 Trans            | actor Command Script Files                                                    | 6-34 |

| 6.7.1 Exa            | mple Command Script File                                                      | 6-35 |

|                      | ing the StrongARM Core                                                        |      |

|                      | ation Switches                                                                |      |

|                      | error count                                                                   |      |

|                      | .error_handle_mode                                                            |      |

|                      |                                                                               |      |

| 6.9.3 sim.core_clk_cycle                                              | 6-40 |

|-----------------------------------------------------------------------|------|

| 6.9.4 sim.core_clk_freq                                               | 6-40 |

| 6.9.5 sim.core clk period                                             | 6-40 |

| 6.9.6 sim.fbus_clk_cycle                                              |      |

| 6.9.7 sim.fbus clk freq                                               |      |

| 6.9.8 sim.fbus_clk_period                                             |      |

| 6.9.9 sim.goto_and_ubreak_key_on_p1                                   |      |

| 6.9.10 sim.halt                                                       |      |

| 6.9.11 sim.pci_clk_cycle                                              |      |

| 6.9.12 sim.pci_clk_freq                                               |      |

| 6.9.13 sim.pci_clk_period                                             |      |

| 6.9.14 sim.post_sim_exec_order                                        |      |

| 6.9.15 sim.prune_prefix_comments                                      |      |

| 6.9.16 sim.silent                                                     |      |

| 6.9.17 sim.time                                                       |      |

|                                                                       |      |

| 7 Foreign Model Simulation Extensions                                 |      |

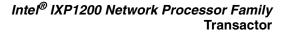

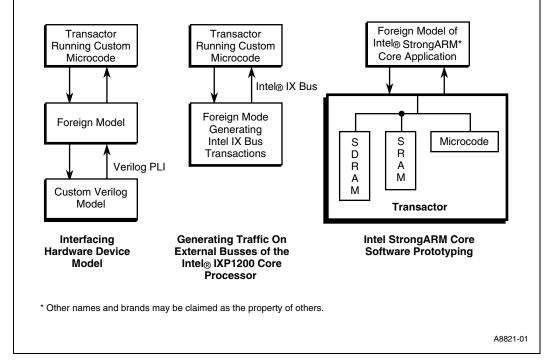

| 7.1 Overview                                                          |      |

| 7.2 Integrating Foreign Models with the Transactor                    |      |

| 7.2.1 Foreign Model Dynamic-Link Library (DLL)                        |      |

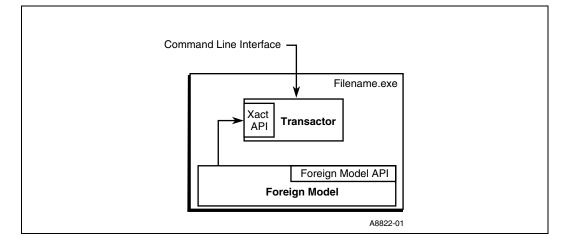

| 7.2.2 Integrated Executable (Integrated Transactor and Foreign Model) |      |

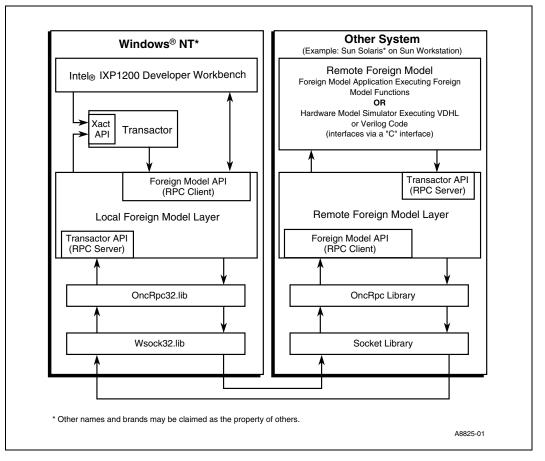

| 7.2.3 Remote Foreign Model Executable                                 |      |

| 7.3 Simulating StrongARM Core Applications                            |      |

| 7.3.1 Using the Hardware Abstraction Layer (HAL)                      |      |

| 7.3.2 Determining IOSTYLE                                             |      |

| 7.3.3 Coding Considerations                                           |      |

| 7.3.4 Accessing Foreign Model Functions from the C Interpreter        |      |

| 7.3.5 Building the Application                                        |      |

| 7.4 Simulating IX Bus Devices                                         |      |

| 7.5 Sample Code                                                       |      |

| 7.5.1 Creating A Foreign Model DLL Used with the Developer Workbench  |      |

| 7.5.1.1 DLL Sample Code                                               |      |

| 7.5.2 Creating A Remote Foreign Model - Local Foreign Model Layer     |      |

| 7.5.2.1 Sample Code                                                   |      |

| 7.5.3 Creating a Remote Foreign Model - Remote Foreign Model Layer    |      |

| 7.5.3.1 Sample Code                                                   | 7-14 |

| A Transactor States                                                   | A-1  |

| A.1 About States                                                      |      |

| A.1.1 State Definition Format                                         |      |

| A.1.2 Display Formats for Statistics States                           |      |

| A.1.2 Display Formats for Statistics States                           |      |

| A.2 Hardware States<br>A.2.1 Microengine GPR or Transfer Register     |      |

| A.2.2 Microengine Control Store                                       |      |

| A.2.2 Microengine Condition Codes                                     |      |

| A.2.4 Microengine Microstore Data Registers                           |      |

| A.2.5 Microengine Microstore Address Registers                        |      |

| A.2.6 Microengine Thread Program Counter Register                     |      |

| A.2.7 Enabled Thread Wake Up Signals                                  |      |

| A.2.7 Enabled Thread Wake Op Signals                                  |      |

| A.2.9 Transmit and Receive FIFOs                                      |      |

|                                                                       |      |

| A.2.10       FBI CSRs       A.13         A.2.11       FBI Scratchpad Memory       A.15         A.2.12       SRAM       A.16         A.2.13       SRAM Push/Pop Registers       A.17         A.2.14       SIRMM       A.18         A.3       Simulation States       A.19         A.3.1       Specify Mircengine(s) for GOTO       A-20         A.3.3       Report Core Clock Cycles       A-20         A.3.4       Core Clock Frequency       A-21         A.3.5       Core Clock Frequency       A-22         A.3.6       Report Fus Clock Cycles       A-22         A.3.7       FBus Clock Frequency       A-22         A.3.8       FBus Clock Cycles       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.11       PCI Clock Frequency       A-23         A.3.12       PCI Clock Cycles       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Hait Simulation       A-26         A.3.17       Suppress Debug Information       A-27         A.3.20                                                                                                                        |   |        |                                 |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|---------------------------------|-------|

| A.2.12       SRAM       A.16         A.2.13       SRAM Push/Pop Registers       A.17         A.2.14       SDFAM       A.18         A.3       Simulation States       A.19         A.3.1       Specify Microengine(s) for GOTO       A.20         A.3.2       Specify Microengine(s) for GOTO       A.20         A.3.3       Report Cree Clock Cycles       A.21         A.3.4       Core Clock Frequency       A.21         A.3.5       Core Clock Frequency       A.22         A.3.6       Report Flus Clock Cycles       A.22         A.3.7       Flus Clock Frequency       A.22         A.3.8       Flus Clock Frequency       A.22         A.3.9       Report PCI Clock Cycles       A.22         A.3.11       PCI Clock Frequency       A.23         A.3.12       Execution Order       A.23         A.3.13       Report Error Count       A.24         A.3.14       Error Handle Mode       A.25         A.3.15       Suppress Comments       A.26         A.3.17       Suppress Comments       A.26         A.3.21       Specify Debug Verbosity Level       A.24         A.3.23       Spperost Debug Information       A.27      A                                                                                                      |   |        |                                 |       |

| A.2.13       SRAM Push/Pop Registers       A.17         A.2.14       SDRAM       A.18         A.3       Simulation States       A.19         A.3.1       Specify Inread(s) for GOTO       A.19         A.3.2       Specify Inread(s) for GOTO       A.20         A.3.3       Report Core Clock Cycles       A.20         A.3.4       Core Clock Period       A.21         A.3.5       Core Clock Cycles       A.21         A.3.6       Report FBus Clock Cycles       A.21         A.3.7       FBus Clock Period       A.22         A.3.8       FBus Clock Period       A.22         A.3.10       PCI Clock Frequency       A.22         A.3.10       PCI Clock Frequency       A.23         A.3.112       Execution Order       A.23         A.3.12       Execution Order       A.24         A.3.13       Report Flow Count       A.24         A.3.14       Execution Order       A.24         A.3.15       Stop Simulation on P1 or P3       A.25         A.3.16       Halt Simulation       A.26         A.3.17       Suppress Comments       A.26         A.3.21       Specify Debug Verbosity Level       A.28         A.3.22<                                                                                                              |   |        |                                 |       |

| A.2.14       SDRAM       A-19         A.3       Simulation States       A-19         A.3.1       Specify Microengine(s) for GOTO       A-20         A.3.3       Report Thread(s) for GOTO       A-20         A.3.4       Core Clock Frequency       A-21         A.3.5       Core Clock Frequency       A-21         A.3.6       Report FBus Clock Cycles       A-21         A.3.7       FBus Clock Frequency       A-22         A.3.8       FBus Clock Period       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report FBus Clock Cycles       A-22         A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Period       A-24         A.3.12       Execution Order       A-24         A.3.13       Report FCI Clock Period       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Statistion on P1 or P3       A-25         A.3.16       Halt Simulation on P1 or P3       A-26         A.3.17       Suppress Debug Information       A-27         A.3.18       Supress Debug Information       A-27         A.3.20       Sinpulstion Time       A-28                                                                                                       |   | A.2.12 | SRAM                            | .A-16 |

| A.3       Simulation States.       A-19         A.3.1       Specify Microengine(s) for GOTO       A-20         A.3.3       Report Core Clock Cycles       A-20         A.3.4       Core Clock Frequency       A-21         A.3.5       Core Clock Period       A-21         A.3.6       Report FBus Clock Cycles       A-221         A.3.6       Report FBus Clock Cycles       A-22         A.3.9       Report FBus Clock Vycles       A-22         A.3.10       PCI Clock Cycles       A-22         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Eror Count.       A-24         A.3.13       Report Eror Count.       A-24         A.3.14       Eror Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Hait Simulation       A-26         A.3.17       Suppress Debug Information       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Debug Verbosity Level       A-30         A.3.22       Specify Debug Verbosity Level       A-32         A.4       Statistics States                                                                                       |   | A.2.13 | SRAM Push/Pop Registers         | .A-17 |

| A.3.1       Specify Microengine(s) for GOTO       A-19         A.3.2       Specify Thread(s) for GOTO       A-20         A.3.3       Report Core Clock Cycles       A-20         A.3.4       Core Clock Frequency       A-21         A.3.5       Core Clock Period       A-21         A.3.6       Report FBus Clock Cycles       A-21         A.3.7       FBus Clock Frequency       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report FBus Clock Cycles       A-22         A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Period       A-24         A.3.13       Report PCI Clock Cycles       A-24         A.3.14       Ercor Count       A-24         A.3.15       Descution order       A-24         A.3.16       Halt Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.20       Specify Reported Execution Stages       A-29         A.3.21       Suppress Debug Information       A-27         A.3.23       Suppress orbug Information       A-27         A.3.24       Specify Reported Execution Stag                                                                           |   | A.2.14 | SDRAM                           | .A-18 |

| A.3.2       Specify Thread(s) for GOTO       A-20         A.3.3       Report Core Clock Cycles       A-20         A.3.4       Core Clock Period       A-21         A.3.5       Core Clock Period       A-21         A.3.6       Report Flaus Clock Cycles       A-21         A.3.7       FBus Clock Period       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.10       PCI Clock Period       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Depotyded Execution Stages       A-29         A.3.22       Chip Version       A-30         A.4.2       SDRAM Read Latency       A-33         A.4.1       Compute Cycles       A-32                                                                                                                 | А | .3 Si  | mulation States                 | .A-19 |

| A.3.2       Specify Thread(s) for GOTO       A-20         A.3.3       Report Core Clock Cycles       A-20         A.3.4       Core Clock Period       A-21         A.3.5       Core Clock Period       A-21         A.3.6       Report Flaus Clock Cycles       A-21         A.3.7       FBus Clock Period       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.10       PCI Clock Period       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Depotyded Execution Stages       A-29         A.3.22       Chip Version       A-30         A.4.2       SDRAM Read Latency       A-33         A.4.1       Compute Cycles       A-32                                                                                                                 |   | A.3.1  | Specify Microengine(s) for GOTO | .A-19 |

| A.3.3       Report Core Clock Cycles       A-20         A.3.4       Core Clock Period       A-21         A.3.5       Core Clock Period       A-21         A.3.6       Report FBus Clock Cycles       A-21         A.3.7       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Execution Order       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       sportes Debug Information       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Debug Verbosity Level       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles <t< td=""><td></td><td>A.3.2</td><td>Specify Thread(s) for GOTO</td><td>.A-20</td></t<> |   | A.3.2  | Specify Thread(s) for GOTO      | .A-20 |

| A.3.4       Core Clock Frequency       A-21         A.3.5       Core Clock Period       A-21         A.3.6       Report FBus Clock Cycles       A-21         A.3.7       FBus Clock Frequency       A-22         A.3.8       FBus Clock Cycles       A-22         A.3.9       Report FDI Clock Cycles       A-22         A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Frequency       A-23         A.3.12       Execution Order       A-24         A.3.13       Report FDr Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Suppress Comments       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Ebus Verbosity Level       A-28         A.3.21       Specify Debug Verbosity Level       A-28         A.3.21       Specify Debug Verbosity Level       A-28         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4.1       Compute Cycles                                                                                 |   | A.3.3  |                                 |       |

| A.3.5       Core Clock Period       A-21         A.3.6       Report FBus Clock Cycles       A-21         A.3.7       FBus Clock Prequency       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.10       PCI Clock Period       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Hait Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33 <td></td> <td>A.3.4</td> <td></td> <td></td>                                          |   | A.3.4  |                                 |       |

| A.3.6       Report FBus Clock Cycles       A-21         A.3.7       FBus Clock Frequency       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Comments       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.4       SThread PC During Idle Cycle       A-34         A.4.5       SDRAM Read Latency                                                                                      |   | A.3.5  |                                 |       |

| A.3.7       FBus Clock Frequency       A-22         A.3.8       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-22         A.3.11       PCI Clock Frequency       A-23         A.3.12       Execution Order       A-24         A.3.13       PCI Clock Period       A-23         A.3.14       Error Count       A-24         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Comments       A-26         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Lock Latency       A-34         A.4.4       Thread Latency       A-35         A.4.4       SDRAM Read Lock Latency       A-36                                                                                            |   |        |                                 |       |

| A.3.8       FBus Clock Period       A-22         A.3.9       Report PCI Clock Cycles       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Suppress Debug Information       A-27         A.3.20       Specify Reported Execution Stages       A-29         A.3.21       Specify Reported Execution Stages       A-32         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-34         A.4.3       SRAM Read Lock Latency       A-34         A.4.4       Thread Latency       A-35         A.4.5       Thread Latency       A-36         A.4.4       SDRAM Read Lock Latency       A-36                                                                                         |   |        |                                 |       |

| A.3.9       Report PCI Clock Cycles       A-22         A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Frequency       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-36         A.4.4       SRAM Read Latency       A-36         A.4.5       Thread PC During Idle Cycle                                                                                      |   |        |                                 |       |

| A.3.10       PCI Clock Frequency       A-23         A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time.       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SPAM Read Lock Latency       A-34         A.4.5       Thread Latency Start and Stop Addresses       A-35         A.4.6       Thread Latency Start and Stop Addresses       A-36         A.4.7       SDRAM Bandwidth <td< td=""><td></td><td></td><td></td><td></td></td<>                                    |   |        |                                 |       |

| A.3.11       PCI Clock Period       A-23         A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-35         A.4.8       Time Slice       A-36         A.4.9       SDRAM Bandwidth       A-3                                                                                    |   |        |                                 |       |

| A.3.12       Execution Order       A-24         A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Hatt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Debug Verbosity Level       A-28         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency       A-36         A.4.8       Time Slice Thread Idle       A-36         A.4.9       Time Slice Thread Idle       A-36 <td></td> <td></td> <td></td> <td></td>                                               |   |        |                                 |       |

| A.3.13       Report Error Count       A-24         A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-26         A.3.16       Hatt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.4       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency       A-36         A.4.8       Time Slice       A-36         A.4.9       Time Slice Thread Idle       A-36                                                                                              |   |        |                                 |       |

| A.3.14       Error Handle Mode       A-25         A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.4       SRAM Read Latency       A-34         A.4.5       Thread Latency       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency       A-35         A.4.8       Time Slice       A-36         A.4.9       Time Slice       A-36         A.4.1       SDRAM Bandwidth       A-37         A.4.                                                                                                              |   |        |                                 |       |

| A.3.15       Stop Simulation on P1 or P3       A-25         A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Latency       A-33         A.4.5       Thread PC During Idle Cycle       A-34         A.4.5       Thread PC During Idle Cycle       A-35         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-36         A.4.9       Time Slice Thread Idle       A-36         A.4.1       SDRAM Bandwidth       A-37         A.4.1       SDRAM Order Queue Fullness       A-38         A.4.1       SDRAM Order Queue Fullness                                                                                   |   |        |                                 |       |

| A.3.16       Halt Simulation       A-26         A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Lock Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-36         A.4.9       Time Slice       A-36         A.4.10       SDRAM Bandwidth       A-37         A.4.11       SDRAM Odd Bank Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14       SDRAM Order Q                                                                           |   |        |                                 |       |

| A.3.17       Suppress Comments       A-26         A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.4       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-35         A.4.8       Time Slice Thread Idle       A-36         A.4.9       Time Slice Thread Idle       A-37         A.4.1       SDRAM Even Bank Queue Fullness       A-37         A.4.1       SDRAM Odd Bank Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14 <td></td> <td></td> <td></td> <td></td>                             |   |        |                                 |       |

| A.3.18       Suppress Debug Information       A-27         A.3.19       Report Simulation Time       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread PC During Idle Cycle       A-35         A.4.7       Thread Latency       A-35         A.4.8       Time Slice       A-36         A.4.9       Time Slice       A-36         A.4.9       Time Slice Thread Idle       A-37         A.4.11       SDRAM Bandwidth       A-37         A.4.12       SDRAM Order Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14       SDRAM Priority Queue Fullness       A-39         A.4.15       SRAM Bandwidth                                                                                   |   |        |                                 |       |

| A.3.19       Report Simulation Time.       A-27         A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version.       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings.       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles.       A-33         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-34         A.4.4       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency Start and Stop Addresses       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-36         A.4.8       Time Slice       A-36         A.4.9       Time Slice       A-36         A.4.10       SDRAM Bandwidth       A-37         A.4.11       SDRAM Bandwidth       A-37         A.4.12       SDRAM Order Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14       SDRAM Order Queue Fullness       A-39         A.4.15                                                                                  |   |        |                                 |       |

| A.3.20       Specify Debug Verbosity Level       A-28         A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-35         A.4.8       Time Slice       A-36         A.4.9       Time Slice Thread Idle       A-36         A.4.10       SDRAM Bandwidth       A-37         A.4.12       SDRAM Odd Bank Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14       SDRAM Priority Queue Fullness       A-39         A.4.15       SRAM Priority Queue Fullness       A-39         A.4.16       SRAM Order Queue Fullness       A-40         A.4.16                                                                             |   |        |                                 |       |

| A.3.21       Specify Reported Execution Stages       A-29         A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Lock Latency       A-34         A.4.5       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency       A-35         A.4.8       Time Slice       A-36         A.4.9       Time Slice       A-36         A.4.9       Time Slice Thread Idle       A-36         A.4.1       SDRAM Bandwidth       A-37         A.4.1       SDRAM Order Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14       SDRAM Order Queue Fullness       A-30         A.4.15       SRAM Bandwidth       A-39         A.4.16       SRAM Priority Queue Fullness       A-40         A.4.16       SRAM Priority Queue Fullness       A-40                                                                                          |   |        |                                 |       |

| A.3.22       Chip Version       A-30         A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Latency       A-33         A.4.5       Thread Latency       A-34         A.4.6       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-36         A.4.8       Time Slice       A-36         A.4.9       Time Slice Inread Idle       A-36         A.4.10       SDRAM Bandwidth       A-37         A.4.11       SDRAM Odd Bank Queue Fullness       A-38         A.4.12       SDRAM Order Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-39         A.4.14       SDRAM Priority Queue Fullness       A-40         A.4.15       SRAM Bandwidth       A-39         A.4.16       SRAM Priority Queue Fullness       A-40         A.4.15       SRAM Priority Queue Fullness<                                                                           |   |        |                                 |       |

| A.3.23       Suppressing Outstanding Signal Errors or Warnings       A-31         A.4       Statistics States       A-32         A.4.1       Compute Cycles       A-32         A.4.2       SDRAM Read Latency       A-33         A.4.3       SRAM Read Latency       A-33         A.4.4       SRAM Read Latency       A-33         A.4.5       Thread Latency       A-34         A.4.6       Thread PC During Idle Cycle       A-34         A.4.6       Thread Latency Start and Stop Addresses       A-35         A.4.7       Thread Latency Start and Stop Addresses       A-36         A.4.9       Time Slice       A-36         A.4.10       SDRAM Bandwidth       A-37         A.4.11       SDRAM Order Neueue Fullness       A-38         A.4.12       SDRAM Order Queue Fullness       A-38         A.4.13       SDRAM Order Queue Fullness       A-38         A.4.14       SDRAM Order Queue Fullness       A-39         A.4.15       SRAM Bandwidth       A-39         A.4.16       SRAM Priority Queue Fullness       A-40         A.4.13       SDRAM Order Queue Fullness       A-40         A.4.14       SRAM Read Lock Queue Fullness       A-40         A.4.16 <td></td> <td></td> <td></td> <td></td>                             |   |        |                                 |       |