## ECE 354 – Computer Systems Lab II

**Microcontroller** Architecture

## **Introduction Lab**

- Difference between IDE and ICD?

- Steps to change code?

- Demo board

- MPLAB software

## **Lab Hours**

- The Marston 228 Lab is open:

- Mondays 2:30 7:00

(TAs: Avi (2:30 4:00), Barron (4:00 7:00))

- Tuesdays 4:00 7:00 (TA: Avi)

- Wednesdays 2:30 7:00

(TAs: Avi (2:30 4:00), Barron (4:00 7:00))

- Thursdays 4:00 7:00 (TA: Matt)

- Fridays 1:00 4:00 (TA: Matt)

## Outline

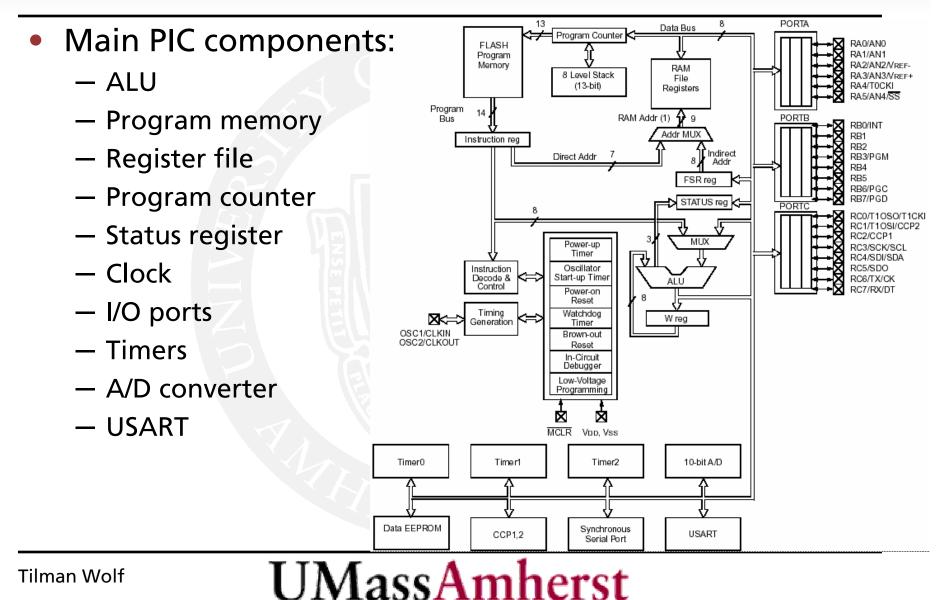

- Microcontroller Architecture (PIC16F877)

- Basic Architecture

- Memories

- Registers

- Instructions

- Serial Communication

- UART

- Tx and Rx

- Lab 1

- Assembly Tutorial

### **UMassAmherst**

## **Computer Architecture**

- What is the minimum a computer needs?

- Memory (instruction, data, or combined)

- Processor/ALU

- I/O

- What are the basic processing steps?

- Instruction fetch

- Instruction decode

- Memory read

- ALU operation

- Write-back

- Details depend on particular architecture

## **PIC16F877** Architecture

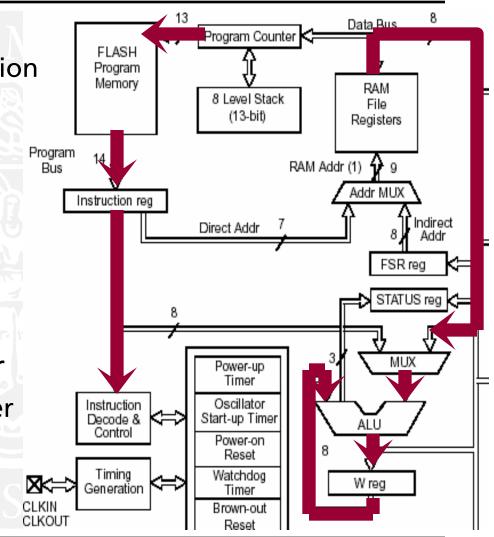

# **Processing on PIC**

- Basic Steps:

- Determine current instruction based on program counter

- Load instruction into instruction register

- Decode instruction

- Read register

- Perform ALU operation

- Write back result

- Additional data paths for

- Change in program counter

- Immediate values

- I/O operation

Tilman Wolf

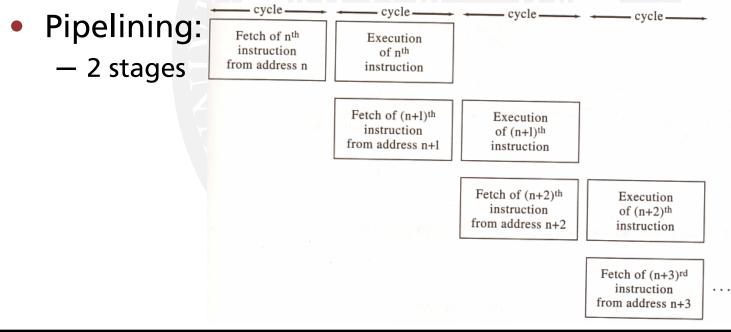

# Pipelining

- Harvard architecture

- Separate program and data memory

- Observation

- Program memory is idle while data memory is in use

- Accesses could be interleaved

**UMassAmherst**

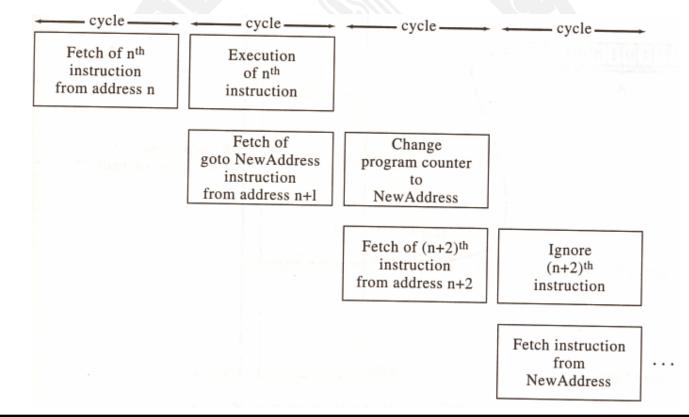

## **Pipeline Stalls**

- Causes for pipeline stalls

- Control dependencies

- Data dependencies

**UMassAmherst**

## **Instruction Memory**

- How many bits do we need to address memory?

- E.g., how many bits do we need to address 4kbit of memory?

- Well, it depends...

- What is the smallest unit that we need to address?

- E.g., 8-bit addressable: 4kb/8b = 512 words, requires  $log_2(512)$  bits

- Instruction memory on PIC16F877

- 8K instructions

- Instruction size: 14 bits

- How many address bits do we need?

## **Instruction Memory**

Hex Program Memory map address memory 000 goto Mainline Special instructions 001 002 003 - 0x000 start of program is 004 goto IntService 005 single goto instruction 0x004 goto to interrupt Tables service routine Memory map is created EndofTables Mainline by IDE software when Mainline program project is built and its subroutines IntService Interrupt service routine and its subroutines EndofCode

(a) Program memory map

# **Call Instructions**

13

PCLATH 0

program

counter

4 3

eleven bits

PCLATH.3 = 0

PCLATH.3 = 1

instructio

Program

memory

2K

parts (11-bit

address range)

> 4K parts (12-bit

address

range

address

000

7FF

800

- PIC designers needed to save bits wherever possible

- Lots of "hacks" necessary to exploit full functionality

- Example: call instruction

- Basically changes program counter

- There are also other effect that we'll discuss later

- Program counter is 13 bits

- Call function can only provide 11 bits (why?)

- Two additional bits are stored in special register

- Calls within current 2K instruction block are "cheaper"

- Why?

### Reset

- What happens on RESET?

- Two possible causes for RESET

- Power applied to 16F877

- MCLR (master clear) asserted active low

- PC automatically cleared to 0x000

- Reset vector stored at 0x000

- Program counter jumps to actual program start

- Program may start at 0x005 or higher address

# **Register File**

- Registers are data memory

- Most registers are generalpurpose

- Some are special-purpose

- Each register holds 8-bit value

- Registers are separated into banks

- 128 registers per bank

- PIC16F877 has 4 banks

- Why use banks?

| Indirect addr. <sup>(*)</sup> | 00h | Indirect addr. <sup>(*)</sup> | 80h        | Indirect addr. <sup>(*)</sup> | 100h         | Indirect addr. <sup>(*)</sup> | 180h    |

|-------------------------------|-----|-------------------------------|------------|-------------------------------|--------------|-------------------------------|---------|

| TMR0                          | 01h | OPTION_REG                    | 81h        | TMR0                          | 101h         | OPTION_REG                    | 181h    |

| PCL                           | 02h | PCL                           | 82h        | PCL                           | 102h         | PCL                           | 182h    |

| STATUS                        | 03h | STATUS                        | 83h        | STATUS                        | 103h         | STATUS                        | 183h    |

| FSR                           | 04h | FSR                           | 84h        | FSR                           | 104h         | FSR                           | 184h    |

| PORTA                         | 05h | TRISA                         | 85h        |                               | 105h         |                               | 185h    |

| PORTB                         | 06h | TRISB                         | 86h        | PORTB                         | 106h         | TRISB                         | 186h    |

| PORTC                         | 07h | TRISC                         | 87h        |                               | 107h         |                               | 187h    |

| PORTD (1)                     | 08h | TRISD (1)                     | 88h        |                               | 108h         |                               | 188h    |

| PORTE (1)                     | 09h | TRISE <sup>(1)</sup>          | 89h        |                               | 109h         |                               | 189h    |

| PCLATH                        | 0Ah | PCLATH                        | 8Ah        | PCLATH                        | 10Ah         | PCLATH                        | 18Ah    |

| INTCON                        | 0Bh | INTCON                        | 8Bh        | INTCON                        | 10Bh         | INTCON                        | 18Bh    |

| PIR1                          | 0Ch | PIE1                          | 8Ch        | EEDATA                        | 10Ch         | EECON1                        | 18Ch    |

| PIR2                          | 0Dh | PIE2                          | 8Dh        | EEADR                         | 10Dh         | EECON2                        | 18Dh    |

| TMR1L                         | 0Eh | PCON                          | 8Eh        | EEDATH                        | 10Eh         | Reserved <sup>(2)</sup>       | 18Eh    |

| TMR1H                         | 0Fh |                               | 8Fh        | EEADRH                        | 10Fh         | Reserved <sup>(2)</sup>       | 18Fh    |

| T1CON                         | 10h |                               | 90h        |                               | 110h         |                               | 190h    |

| TMR2                          | 11h | SSPCON2                       | 91h        |                               | 111h         |                               | 191h    |

| T2CON                         | 12h | PR2                           | 92h        |                               | 112h         |                               | 192h    |

| SSPBUF                        | 13h | SSPADD                        | 93h        |                               | 113h         |                               | 193h    |

| SSPCON                        | 14h | SSPSTAT                       | 94h        |                               | 114h         |                               | 194h    |

| CCPR1L                        | 15h |                               | 95h        |                               | 115h         |                               | 195h    |

| CCPR1H                        | 16h |                               | 96h        |                               | 116h         |                               | 196h    |

| CCP1CON                       | 17h |                               | 97h        | General                       | 117h         | General                       | 197h    |

| RCSTA                         | 18h | TXSTA                         | 98h        | Purpose<br>Register           | 118h         | Purpose<br>Register           | 198h    |

| TXREG                         | 19h | SPBRG                         | 99h        | 16 Bytes                      |              | 16 Bytes                      | 199h    |

| RCREG                         | 1Ah |                               | 9Ah        | 11Ah<br>11Bh<br>11Ch          | 11Ah         |                               | 19Ah    |

| CCPR2L                        | 1Bh |                               | 9Bh        |                               | 11Bh         |                               | 19Bh    |

| CCPR2H                        | 1Ch |                               | 9Ch        |                               | 11Ch         |                               | 19Ch    |

| CCP2CON                       | 1Dh |                               | 9Dh        |                               | 11Dh         |                               | 19Dh    |

| ADRESH                        | 1Eh | ADRESL                        | 9Eh        |                               | 11Eh         |                               | 19Eh    |

| ADCON0                        | 1Fh | ADCON1                        | 9Fh        |                               | 11Fh         |                               | 19Fh    |

|                               | 20h |                               | A0h        |                               | 120h         |                               | 1A0h    |

|                               |     |                               | 71011      |                               |              |                               | 17 1911 |

|                               |     |                               |            |                               |              |                               |         |

| General<br>Purpose            |     | General<br>Purpose            |            | General<br>Purpose            |              | General<br>Purpose            |         |

| Register                      |     | Register                      |            | Register                      |              | Register                      |         |

| 96 Bytes                      |     | 80 Bytes                      |            | 80 Bytes                      | 4.051        | 80 Bytes                      | 1EFh    |

| 50 Dytes                      |     |                               | EFh<br>F0h |                               | 16Fh<br>170h |                               | 1E0h    |

|                               |     | accesses                      | FUN        | accesses                      | 1700         | accesses<br>70h - 7Fh         | 1 01    |

|                               | 7Fh | 70h-7Fh                       | FFh        | 70h-7Fh                       | 17Fh         | 700-760                       | 1FFh    |

| Bank 0                        |     | Bank 1                        |            | Bank 2                        |              | Bank 3                        |         |

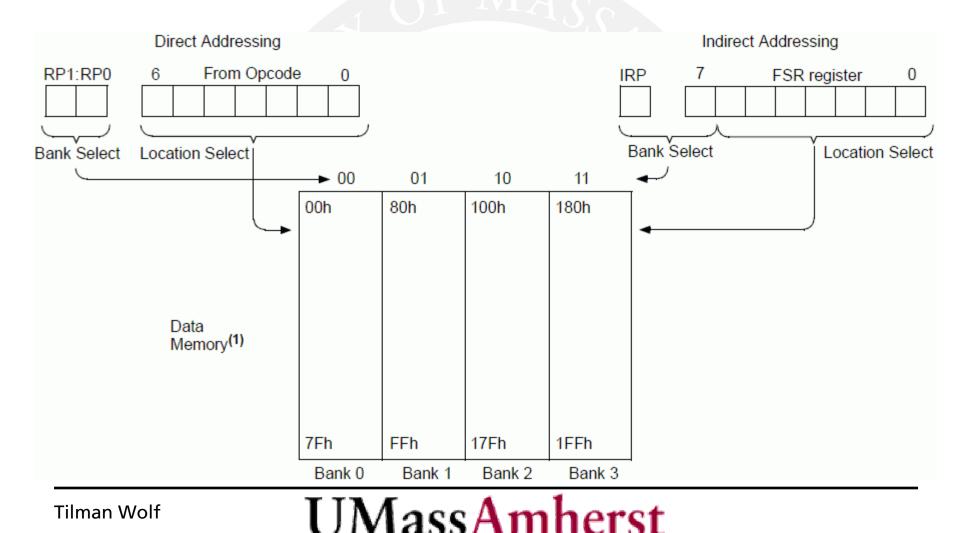

## **Register File Addressing**

#### "Bank Select" bits choose bank (2 bits)

# **CPU Registers**

- Special registers

- Working register

- STATUS register

- FSR (File Select Register)

- INDF register

- Program counter (12 bits)

- PCLATH (Program Counter Latch) (4 bits)

- PCL (8 bits)

- Eight-level stack

- We'll discuss details in other lectures

- For Lab 1: Working register and STATUS register

## **STATUS Register**

- Status bits

- Bit 0: Carry

- Bit 1: Digit carry

- Bit 2: Zero result

- Bits 3 & 4: Use at power-up and sleep

- Bit 5 & 6: bank select

- Bit 7: bank select for indirect addressing

- R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x PD IRP RP0 то Ζ С RP1 DC R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' n= Value at POR reset bit 7: IRP: Register Bank Select bit (used for indirect addressing) 1 = Bank 2, 3 (100h - 1FFh) 0 = Bank 0, 1 (00h - FFh) bit 6-5: RP1:RP0: Register Bank Select bits (used for direct addressing) 11 = Bank 3 (180h - 1FFh) 10 = Bank 2 (100h - 17Fh) 01 = Bank 1 (80h - FFh) 00 = Bank 0 (00h - 7Fh) Each bank is 128 bytes bit 4: TO: Time-out bit 1 = After power-up, CLRWDT instruction, or SLEEP instruction 0 = A WDT time-out occurred bit 3: PD: Power-down bit 1 = After power-up or by the CLRWDT instruction 0 = By execution of the SLEEP instruction bit 2: Z: Zero bit 1 = The result of an arithmetic or logic operation is zero 0 = The result of an arithmetic or logic operation is not zero DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) bit 1: (for borrow the polarity is reversed) 1 = A carry-out from the 4th low order bit of the result occurred 0 = No carry-out from the 4th low order bit of the result C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) bit 0: 1 = A carry-out from the most significant bit of the result occurred 0 = No carry-out from the most significant bit of the result occurred Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

Tilman Wolf

## Instructions

- Instruction format:

- OPCODE determines instrucion

- Registers, bits, literals depend on OPCODE

#### • OPCODE fields:

| Field | Description                                                                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                          |

| W     | Working register (accumulator)                                                                                                                                                |

| b     | Bit address within an 8-bit file register                                                                                                                                     |

| k     | Literal field, constant data or label                                                                                                                                         |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with x = 0. It<br>is the recommended form of use for compati-<br>bility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                  |

| PC    | Program Counter                                                                                                                                                               |

| то    | Time-out bit                                                                                                                                                                  |

| PD    | Power-down bit                                                                                                                                                                |

Byte-oriented file register operations 13 8 76 OPCODE f (FILE #) c – d = 0 for destination W d = 1 for destination f f = 7-bit file register address Bit-oriented file register operations 13 76 10 9 0 OPCODE b (BIT #) f (FILE #) b = 3-bit bit address f = 7-bit file register address Literal and control operations General 13 8 7 0 OPCODE k (literal) k = 8-bit immediate value CALL and GOTO instructions only 11 10 0 13 OPCODE k (literal) k = 11-bit immediate value

Tilman Wolf

## **Instruction Set**

- 35 instructions

- OPCODE

- Letters indicate format

- F, W

- Z indicates conditional execution

- More details

- Datasheet pp.

139-144

- Peatman pp. 25,

27-28

|                                         | Mnemo<br>Operar                       |                           | Description                  | Cycles |     |                 | е    |      | Status<br>Affected | Notes |  |  |

|-----------------------------------------|---------------------------------------|---------------------------|------------------------------|--------|-----|-----------------|------|------|--------------------|-------|--|--|

|                                         | Operat                                | •                         |                              |        | MSb |                 |      | LSb  | Allected           |       |  |  |

|                                         |                                       | BYTE-ORIENTED FILE REGIST |                              |        |     | STER OPERATIONS |      |      |                    |       |  |  |

|                                         | ADDWF                                 | f, d                      | Add W and f                  | 1      | 00  | 0111            | dfff | ffff | C,DC,Z             | 1,2   |  |  |

|                                         | ANDWF                                 | f, d                      | AND W with f                 | 1      | 00  | 0101            | dfff | ffff | Z                  | 1,2   |  |  |

|                                         | CLRF                                  | f                         | Clear f                      | 1      | 00  | 0001            | lfff | ffff | Z                  | 2     |  |  |

|                                         | CLRW                                  | -                         | Clear W                      | 1      | 00  | 0001            | 0xxx | xxxx | Z                  |       |  |  |

|                                         | COMF                                  | f, d                      | Complement f                 | 1      | 00  | 1001            | dfff | ffff | Z                  | 1,2   |  |  |

|                                         | DECF                                  | f, d                      | Decrement f                  | 1      | 00  | 0011            | dfff | ffff | Z                  | 1,2   |  |  |

|                                         | DECFSZ                                | f, d                      | Decrement f, Skip if 0       | 1(2)   | 00  | 1011            | dfff | ffff |                    | 1,2,3 |  |  |

|                                         | INCE                                  | f, d                      | Increment f                  | 1      | 00  | 1010            | dfff | ffff | Z                  | 1,2   |  |  |

|                                         | INCFSZ                                | f, d                      | Increment f, Skip if 0       | 1(2)   | 00  | 1111            | dfff | ffff |                    | 1,2,3 |  |  |

|                                         | IORWF                                 | f, d                      | Inclusive OR W with f        | 1      | 00  | 0100            | dfff | ffff | Z                  | 1,2   |  |  |

|                                         | MOVE                                  | f, d                      | Move f                       | 1      | 00  | 1000            |      | ffff | Z                  | 1,2   |  |  |

|                                         | MOVWF                                 | f                         | Move W to f                  | 1      | 00  | 0000            | lfff | ffff |                    |       |  |  |

|                                         | NOP                                   | -                         | No Operation                 | 1      | 00  | 0000            | 0xx0 | 0000 |                    |       |  |  |

| 7                                       | RLF                                   | f, d                      | Rotate Left f through Carry  | 1      | 00  | 1101            | dfff |      | С                  | 1,2   |  |  |

|                                         | RRF                                   | f, d                      | Rotate Right f through Carry | 1      | 00  | 1100            |      | ffff | С                  | 1,2   |  |  |

|                                         | SUBWF                                 | f, d                      | Subtract W from f            | 1      | 00  | 0010            | dfff | ffff | C,DC,Z             | 1,2   |  |  |

|                                         | SWAPF                                 | f, d                      | Swap nibbles in f            | 1      | 00  | 1110            |      | ffff |                    | 1,2   |  |  |

| 2                                       | XORWF                                 | f, d                      | Exclusive OR W with f        | 1      | 00  | 0110            | dfff | ffff | Z                  | 1,2   |  |  |

|                                         | BIT-ORIENTED FILE REGISTER OPERATIONS |                           |                              |        |     |                 |      |      |                    |       |  |  |

| BCF f, b Bit Clearf 1 01 00bb bfff ffff |                                       |                           |                              |        |     |                 |      | 1,2  |                    |       |  |  |

|                                         | BSF                                   | f, b                      | Bit Set f                    | 1      | 01  | 01bb            | bfff | ffff |                    | 1,2   |  |  |

|                                         | BTFSC                                 | f, b                      | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb            | bfff | ffff |                    | 3     |  |  |

|                                         | BTFSS                                 | f, b                      | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb            | bfff | ffff |                    | 3     |  |  |

|                                         | LITERAL AND CONTROL OPERATIONS        |                           |                              |        |     |                 |      |      |                    |       |  |  |

|                                         | ADDLW                                 | k                         | Add literal and W            | 1      | 11  | 111x            | kkkk | kkkk | C,DC,Z             |       |  |  |

|                                         | ANDLW                                 | k                         | AND literal with W           | 1      | 11  | 1001            |      | kkkk | Z                  |       |  |  |

|                                         | CALL                                  | k                         | Call subroutine              | 2      | 10  | okkk            |      | kkkk | -                  |       |  |  |

|                                         | CLRWDT                                | -                         | Clear Watchdog Timer         | 1      | 00  | 0000            | 0110 | 0100 | TO,PD              |       |  |  |

|                                         | GOTO                                  | k                         | Go to address                | 2      | 10  | 1kkk            |      | kkkk | ,                  |       |  |  |

|                                         | IORLW                                 | k                         | Inclusive OR literal with W  | 1      | 11  | 1000            |      | kkkk | Z                  |       |  |  |

|                                         | MOVLW                                 | k                         | Move literal to W            | 1      | 11  | 00xx            |      | kkkk |                    |       |  |  |

| J                                       | RETFIE                                | -                         | Return from interrupt        | 2      | 0.0 | 0000            | 0000 | 1001 |                    |       |  |  |

|                                         | RETLW                                 | k                         | Return with literal in W     | 2      | 11  | 01XX            |      | kkkk |                    |       |  |  |

|                                         | RETURN                                | -                         | Return from Subroutine       | 2      | 00  | 0000            | 0000 | 1000 |                    |       |  |  |

|                                         | SLEEP                                 | -                         | Go into standby mode         | 1      | 00  | 0000            | 0110 | 0011 | TO.PD              |       |  |  |

|                                         | SUBLW                                 | k                         | Subtract W from literal      | 1      | 11  | 110x            |      | kkkk | C,DC,Z             |       |  |  |

|                                         | XORLW                                 | k                         | Exclusive OR literal with W  | 1      | 11  | 1010            |      | kkkk | Z                  |       |  |  |

#### **UMassAmherst**

## Assembler

- Creating instructions "by hand" is difficult

- Binary code specifies op-code and values of operands

"11 1110 1000 0111" adds 135 to working register

- Accombler translates "readable" code into bina

- Assembler translates "readable" code into binary

- "ADDLW 135" means "add literal 135 to working register"

- Assembler converts this to "11 1110 1000 0111"

- Other convenient features

- Labels for branches and jumps (e.g., "bug" and "start")

- Register addresses can be named (e.g., "c1 equ 0x0c")

# Lab 1

- Connect PIC to terminal

- PIC in stand-alone mode using USART interface

- Mostly software development

- Required functionality:

- Three bits of port A connected to switches

- Value of port A is shown on LEDs on port B

- PIC sends "Number?" to terminal

- User presses key, value is sent to PIC and echoed

- If user presses '0'-'7', PIC compares value to port A and sends response to terminal: "equal" or "not equal"

- Send response every time switch values change

- Repeat with user input

## **UART/USART**

- "<u>Universal Synchronous/A</u>synchronous <u>Receiver/Transmitter</u>"

- Serial data communication between PIC and Terminal

- Two cables (receive and transmit)

- Each 1-byte character is transmitted separately

Start, 8 data bits, 1 parity bit, Stop

- We use asynchronous mode

- Sender uses local clock

- Baud rate specifies speed of transmission

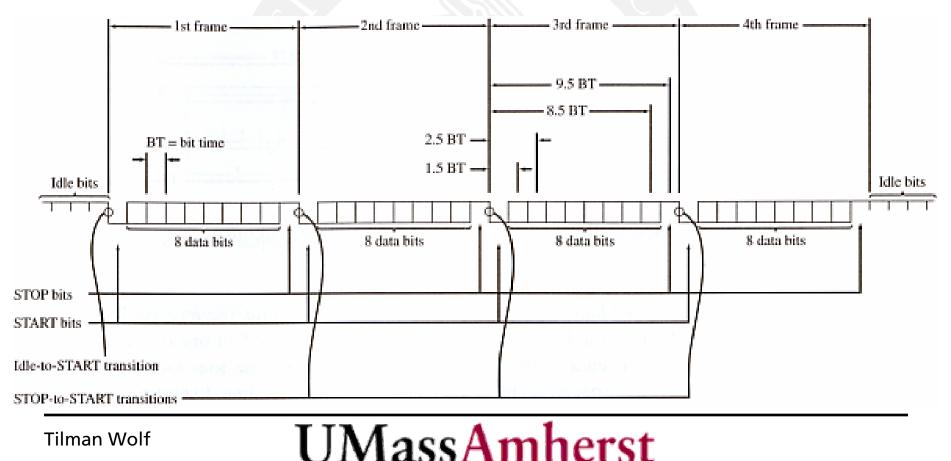

## **Synchronization**

- Clocks on sender and receiver are never exactly in sync

- Requires synchronization of receiver

- High-low transition signals frame boundary

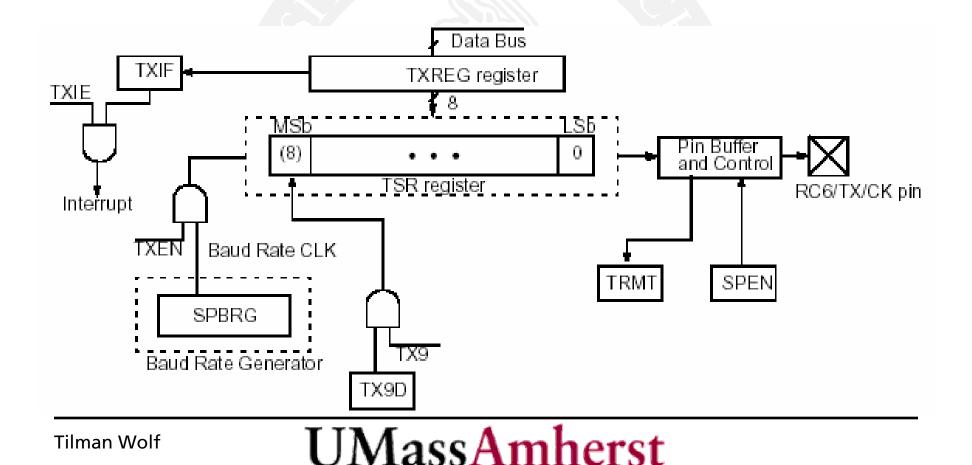

# **UART on PIC16F877**

- Several registers involved

- Control/status registers:

- TXSTA (transmit status and control register)

- RCSTA (receive status and control register)

- Configurations: enable bit, 8/9 bit, buffer full, etc.

| Baud rate generator:                                                     | BAUD<br>RATE<br>(K) | Fosc = 20 MHz |            |                             |  |

|--------------------------------------------------------------------------|---------------------|---------------|------------|-----------------------------|--|

| <ul> <li>SPBGR</li> <li>Data sheet table 10-3 shows value for</li> </ul> |                     | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| different clock and baud rates                                           | 0.3                 | -             | -          | -                           |  |

| Data registers:                                                          | 1.2                 | 1.221         | 1.75       | 255                         |  |

| Data registers:                                                          | 2.4                 | 2.404         | 0.17       | 129                         |  |

| — TXREG and RCREG                                                        | 9.6                 | 9.766         | 1.73       | 31                          |  |

| Ty and By completion:                                                    | 19.2                | 19.531        | 1.72       | 15                          |  |

| • Tx and Rx completion:                                                  | 28.8                | 31.250        | 8.51       | 9                           |  |

| — PIR1<4> and PIR1<5>                                                    | 33.6                | 34.722        | 3.34       | 8                           |  |

| set when TXREG clears and RCREG is filled                                | 57.6                | 62.500        | 8.51       | 4                           |  |

|                                                                          | HIGH                | 1.221         | -          | 255                         |  |

| Optional: enable bit in PIE1 for interrupt                               | LOW                 | 312.500       | -          | 0                           |  |

Tilman Wolf

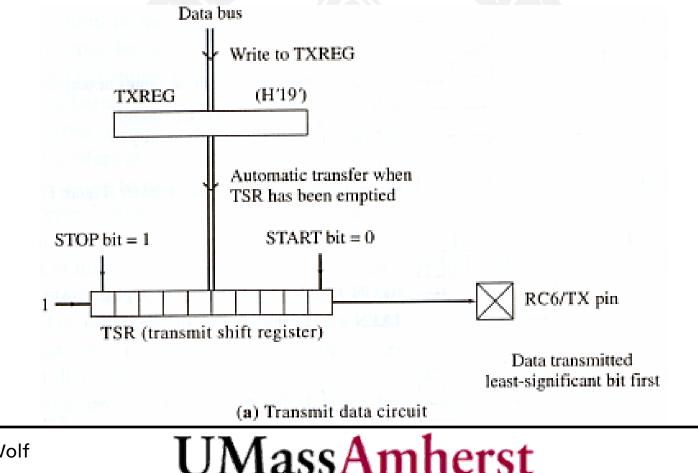

## **UART Transmission**

- TXREG is accessed from program

- Need to check if empty before writing next value (TXSTA)

## **UART Transmission**

- Actually, it's more complicating

- Ensure all related registers are configured correctly

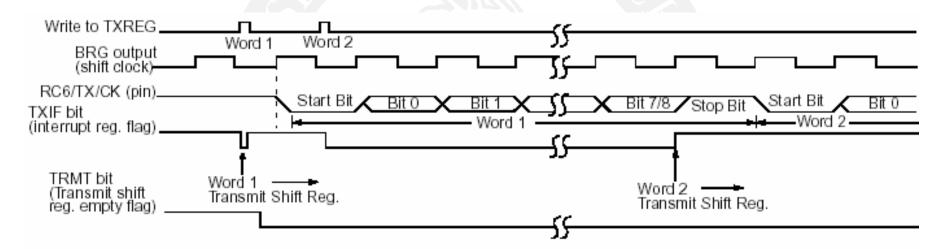

## **UART Tx Signals**

#### Example for two transmissions

**UMassAmherst**

Note: This timing diagram shows two consecutive transmissions.

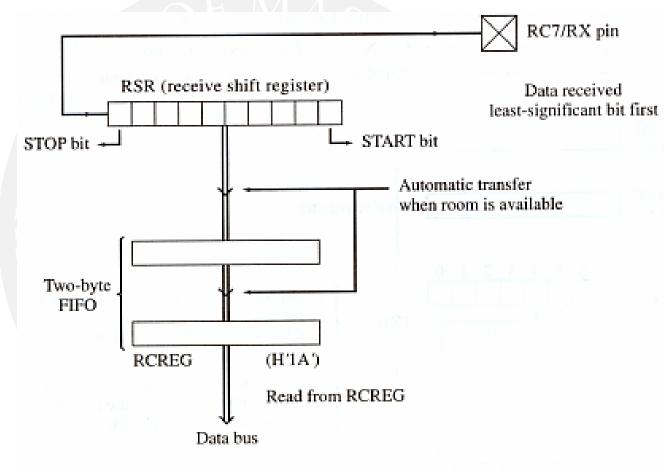

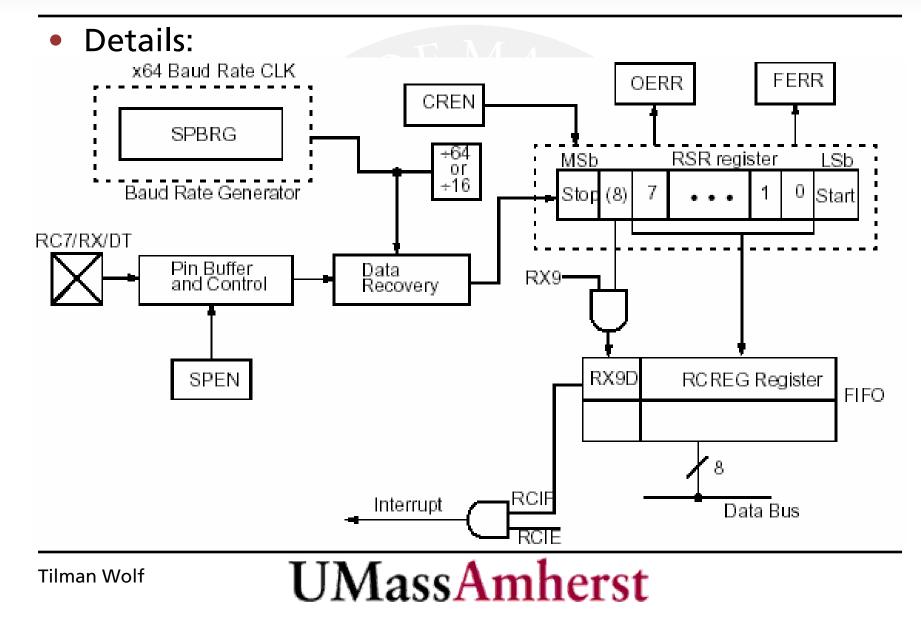

## **UART Receiving**

• 2-byte FIFO

(b) Receive data circuit

**UMassAmherst**

## **UART Receiving**

#### **Hardware Setup**

Requires 20PIC ± 22 μF 22 µF 1 MAX232 driver 18 - PIC: 0/+5V 11 — RS-232 13 interface: 17 Serial connector to PC ±10V  $22 \mu F^{1}$ 22 µF DB-9S 19 (female) See Peatman Ch. 11 15 6 RC6/TX 2 3 16 RC7/RX 4 RS-232 interface chip 5 Motorola MC145407 Ť (20-pin DIP) 6 7 8

**UMassAmherst**

9

# Lab 1

#### BEFORE YOU START: READ!

- Lab Assignment

- Data sheet pp. 29 33 (port I/O)

- Data sheet pp. 95 104 (UART)

- Peatman, chapter 11 (UART)

- MAX232 data sheet

- Quiz will have a few simple questions regarding lab

- Think about how you want to split work

- Think about steps to take to get it working

- Start working early!

- Lab schedule starts today