# RECONFIGURABLE DATA ACQUISITION SYSTEM FOR WEATHER RADAR APPLICATIONS <sup>1</sup>

A Thesis Presented

by

RISHI KHASGIWALE

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

December 2004

Electrical and Computer Engineering

<sup>&</sup>lt;sup>1</sup>This work is supported primarily by the Engineering Research Centers Program of the National Science Foundation under NSF award number 0313747. Any opinions, findings, conclusions, or recommendations expressed in this material are those of the authors and do not necessarily reflect those of the National Science Foundation.

© Copyright by Rishi Khasgiwale 2004 All Rights Reserved

# RECONFIGURABLE DATA ACQUISITION SYSTEM FOR WEATHER RADAR APPLICATIONS

| A Thesis Presented |

|--------------------|

| by                 |

| RISHI KHASCIWAI F  |

| Approved as to style and content b | 7:                           |      |

|------------------------------------|------------------------------|------|

|                                    |                              |      |

| Russell G. Tessier, Chair          |                              |      |

|                                    |                              |      |

| Stephen J. Frasier, Member         |                              |      |

|                                    |                              |      |

| Wayne P. Burleson, Member          |                              |      |

|                                    |                              |      |

|                                    | Seshu B. Desu, Department Ch | nair |

Electrical and Computer Engineering

## ABSTRACT

# RECONFIGURABLE DATA ACQUISITION SYSTEM FOR WEATHER RADAR APPLICATIONS

#### DECEMBER 2004

#### RISHI KHASGIWALE

B.E., MAULANA AZAD COLLEGE OF TECHNOLOGY, REGIONAL ENGINEERING COLLEGE (REC), BHOPAL, INDIA

M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Russell G. Tessier

Tornado, hazardous weather and flood detection radar systems demand high-throughput sustainable, high-speed data acquisition and processing systems. These systems need to be capable of implementing powerful signal processing algorithms in real-time on the raw data collected by these radars. Support for high-speed network facilities for real-time data dissemination to the end-user is expected for timely and accurate detection of imminent weather disasters. Designing a data acquisition and processing system to meet these requirements has been made feasible due to the recent developments in fields of networking and reconfigurable computing. This work describes a single circuit card, real-time acquisition and processing system with capabilities of real-time data distribution. Remote-host based control and remote-reconfigurability of the system further assist in meeting the guidelines of such

iv

applications. The goal of this research work is to provide the Distributed Collaborative Adaptive Sensing (DCAS) radars being developed by the Engineering Research Center (ERC) for Collaborative Adaptive Sensing of the Atmosphere (CASA) at the University of Massachusetts-Amherst with a powerful data acquisition and processing system.

## TABLE OF CONTENTS

|               |                          | Page                                                                                                                                                    |

|---------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{A}$  | BST                      | RACTiv                                                                                                                                                  |

| $\mathbf{LI}$ | ST (                     | OF TABLES x                                                                                                                                             |

| LI            | ST (                     | OF FIGURESxi                                                                                                                                            |

| Cl            | HAP                      | $^{\prime}\mathrm{TER}$                                                                                                                                 |

| 1.            | INT                      | TRODUCTION 1                                                                                                                                            |

| 2.            | BA                       | CKGROUND 4                                                                                                                                              |

|               | 2.1<br>2.2               | Radar System Overview                                                                                                                                   |

| 3.            | $\mathbf{R}\mathbf{A}$   | DAR SYSTEM SPECIFICATIONS 7                                                                                                                             |

|               | 3.1<br>3.2<br>3.3<br>3.4 | Radar System7Radar Terminology Definitions7Radar Specifications8Data Acquisiton System Features8                                                        |

| 4.            | DA'                      | TA ACQUISITION SYSTEM ARCHITECTURE 12                                                                                                                   |

|               | 4.1<br>4.2<br>4.3        | Radar Interface and Analog Section12FPGA1 and FPGA214Microcontroller15                                                                                  |

| <b>5.</b>     | SYS                      | STEM OPERATION                                                                                                                                          |

|               | 5.1                      | ARM Microcontroller                                                                                                                                     |

|               |                          | 5.1.1 Introduction       17         5.1.2 Ethernet Media Access Controller (EMAC)       19         5.1.3 Universal Serial Bus (USB) Controller       19 |

|                          |                                                                                                | 5.1.3.1 $5.1.3.2$                                                                                                                                                                                                                       |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | 5.1.4<br>5.1.5                                                                                 | Universa                                                                                                                                                                                                                                | al Synchronous Asynchronous Receiver Transceiver                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          | 5.1.6                                                                                          |                                                                                                                                                                                                                                         |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          |                                                                                                | 5.1.6.1<br>5.1.6.2<br>5.1.6.3                                                                                                                                                                                                           | External Bus Interface (EBI)                                        | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          | 5.1.7                                                                                          | Microco                                                                                                                                                                                                                                 | ntroller Operation                                                  | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          |                                                                                                | 5.1.7.1                                                                                                                                                                                                                                 | Operating System                                                    | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.2                      | Field l                                                                                        | Programn                                                                                                                                                                                                                                | nable Gate Arrays (FPGAs)                                           | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          | 5.2.1<br>5.2.2                                                                                 |                                                                                                                                                                                                                                         |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          |                                                                                                | 5.2.2.1<br>5.2.2.2                                                                                                                                                                                                                      | <u> </u>                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.3<br>5.4               |                                                                                                |                                                                                                                                                                                                                                         |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          |                                                                                                |                                                                                                                                                                                                                                         |                                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.1<br>6.2<br>6.3<br>6.4 | Power<br>Isolati                                                                               | Supply fi<br>on Shield                                                                                                                                                                                                                  | ltering for Analog section                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

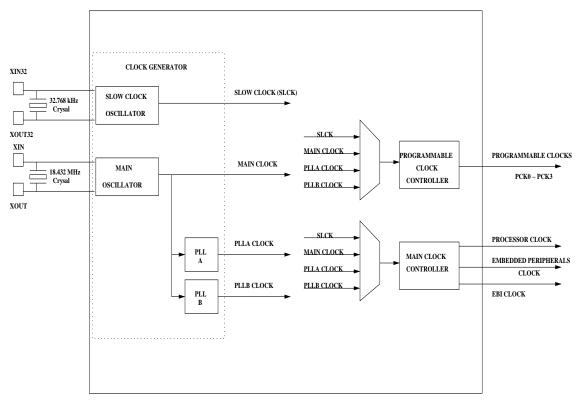

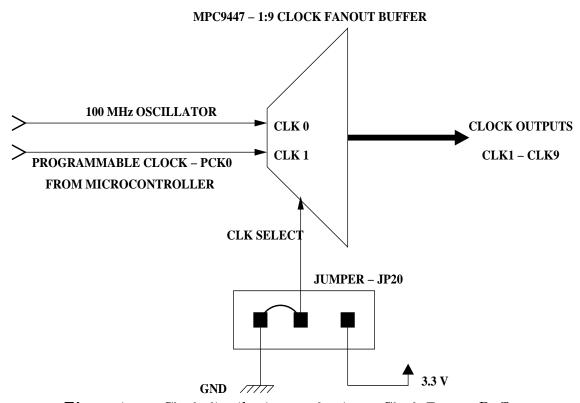

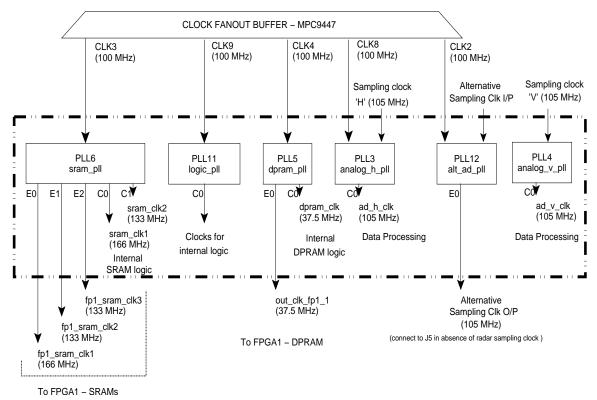

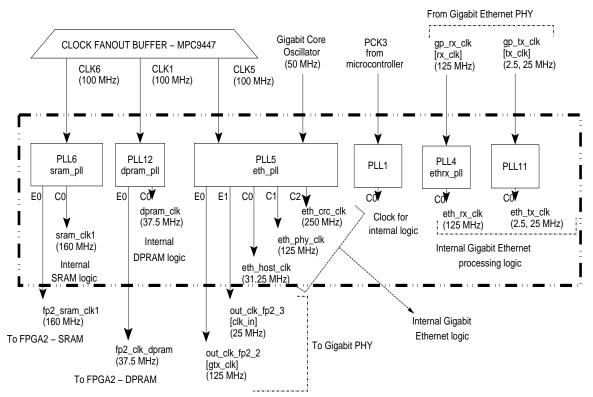

| CLO                      | OCK I                                                                                          | DISTRIE                                                                                                                                                                                                                                 | BUTION MECHANISM                                                    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7.1<br>7.2<br>7.3<br>7.4 | Clock<br>Sampl                                                                                 | distributi<br>ing Clock                                                                                                                                                                                                                 | on mechanism for FPGAs and their peripherals distribution mechanism | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SYS                      | STEM                                                                                           | вооти                                                                                                                                                                                                                                   | JP STRATEGY                                                         | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8.1<br>8.2               |                                                                                                |                                                                                                                                                                                                                                         |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                          | 5.3<br>5.4<br>POY<br>6.1<br>6.2<br>6.3<br>6.4<br>CLO<br>7.1<br>7.2<br>7.3<br>7.4<br>SYS<br>8.1 | 5.1.5 5.1.6 5.1.6 5.1.7 5.2 Field 1 5.2.1 5.2.2 5.3 Extern 5.4 System  POWER 3 MECH 6.1 Power 6.2 Power 6.3 Isolati 6.4 Extern CLOCK I 7.1 Microe 7.2 Clock 7.3 Sampl 7.4 Gigab  SYSTEM 8.1 Microe 8.1 Microe 8.1 Microe 8.1 Microe 8.1 | 5.1.3.2  5.1.4 Debug U 5.1.5 Universa                               | 5.1.4 Debug Unit (DBGU) 5.1.5 Universal Synchronous Asynchronous Receiver Transceiver (USART) 5.1.6 Memory Map  5.1.6.1 Internal Memory Mapping 5.1.6.2 External Bus Interface (EBI) 5.1.6.3 Memory Allocation for Peripherals  5.1.7 Microcontroller Operation 5.1.7.1 Operating System  5.2 Field Programmable Gate Arrays (FPGAs)  5.2.1 FPGA1 Architecture 5.2.2 FPGA2 Architecture 5.2.2.1 Gigabit Ethernet Core 5.2.2.2 IDE Controller  5.3 External On-board Memory Resources 5.4 System Operation  POWER SUPPLY FILTERING AND DISTRIBUTION MECHANISM  6.1 Power Supply filtering for Digital section 6.2 Power Supply filtering for Analog section 6.3 Isolation Shields 6.4 External Power Supply Lugs  CLOCK DISTRIBUTION MECHANISM  7.1 Microcontroller clock distribution mechanism 7.2 Clock distribution mechanism for FPGAs and their peripherals 7.3 Sampling Clock distribution mechanism 7.4 Gigabit Ethernet core clock distribution mechanism 7.5 Gigabit Ethernet core clock distribution mechanism 7.6 Gigabit Ethernet core clock distribution mechanism |

|    |              | 8.2.1<br>8.2.2<br>8.2.3    | Configuration via JTAG port  Dynamic Reconfiguration  Remote-User based, Dynamic Reconfiguration                                                  | 47             |

|----|--------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 9. | SIM          | ULAT                       | ION SETUP                                                                                                                                         | 49             |

|    | 9.1<br>9.2   |                            | tion Flow                                                                                                                                         |                |

|    |              | 9.2.1                      | Tools Used                                                                                                                                        | 53             |

| 10 | .co          | NFIGU                      | RATION STRAPS AND JUMPER SETTINGS                                                                                                                 | . 54           |

| 11 | .TES         | TING                       | AND DEBUGGING THE HARDWARE SYSTEM                                                                                                                 | . 59           |

|    | 11.1         | Debug                      | ging features                                                                                                                                     | 59             |

|    |              |                            | External Power supply mechanism                                                                                                                   |                |

|    | 11.3         | Prelim                     | ging tools                                                                                                                                        | 60             |

|    |              |                            | Loading the Boot code                                                                                                                             |                |

|    | 11.6<br>11.7 | Testing<br>Testing         | g the FPGAs and PLD connectivity g the Microcontroller - FPGA interface g the Analog section and FPGA1 g the Gigabit Ethernet interface and FPGA2 | 66<br>66       |

| 12 | .RES         | SULTS                      |                                                                                                                                                   | 69             |

|    |              |                            | distribution design                                                                                                                               |                |

|    |              | 12.2.2<br>12.2.3<br>12.2.4 | Loading microcontroller boot code via debug serial port                                                                                           | 70<br>70<br>70 |

|    |              |                            | - FPGA1 - FPGA2 JTAG chain                                                                                                                        |                |

| 12       | .5 Results for FPGA2 and Gigabit Ethe | $ernet interface \dots$ | 1        |

|----------|---------------------------------------|-------------------------|----------|

| 13.S     | JMMARY                                |                         | 3        |

| 13<br>13 | .1 Conclusion                         |                         | '3<br>'4 |

| APP      | ENDICES                               |                         |          |

|          | CHEMATICSOARD PICTURE                 |                         |          |

| BIBI     | IOGRAPHY                              | 10                      | 3        |

## LIST OF TABLES

| Table |                                                    | Page |  |

|-------|----------------------------------------------------|------|--|

| 5.1   | Altera Stratix EP1S40                              | 6    |  |

| 9.1   | Design Tools                                       | 3    |  |

| 10.1  | Speed-strap settings for Auto-Negotiation disabled | 6    |  |

| 10.2  | Speed-strap settings for Auto-Negotiation enabled  | 6    |  |

## LIST OF FIGURES

| Figu | Figure Pag                                                          |  |

|------|---------------------------------------------------------------------|--|

| 2.1  | Data Acquisition board integrated with a radar unit - Block diagram |  |

| 3.1  | Block Diagram of Data Acquisition System                            |  |

| 4.1  | Block Diagram of Data Acquisition System                            |  |

| 5.1  | ARM Microcontroller Architecture                                    |  |

| 5.2  | External Memory Areas                                               |  |

| 5.3  | Internal Memory Map                                                 |  |

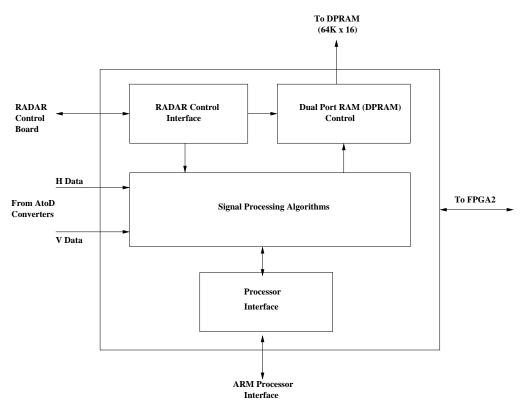

| 5.4  | FPGA1 Architecture                                                  |  |

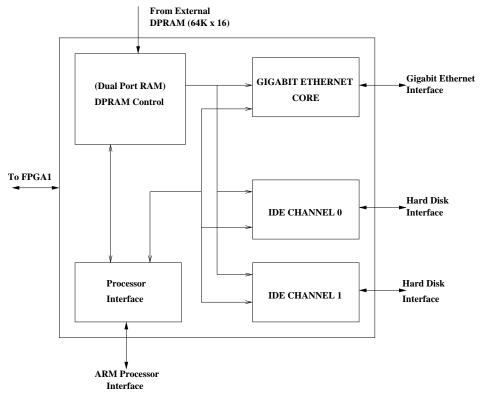

| 5.5  | FPGA2 Architecture                                                  |  |

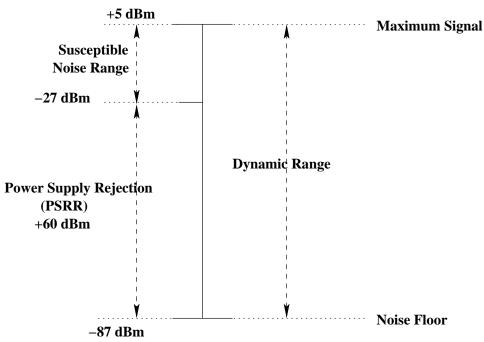

| 6.1  | A to D Converter Specifications                                     |  |

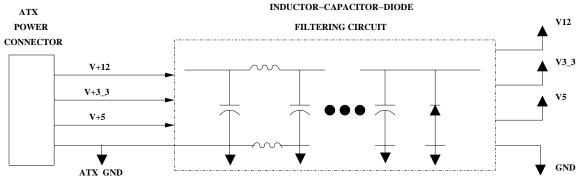

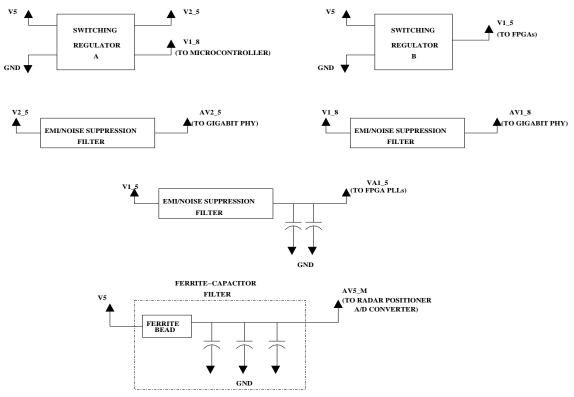

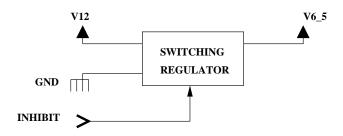

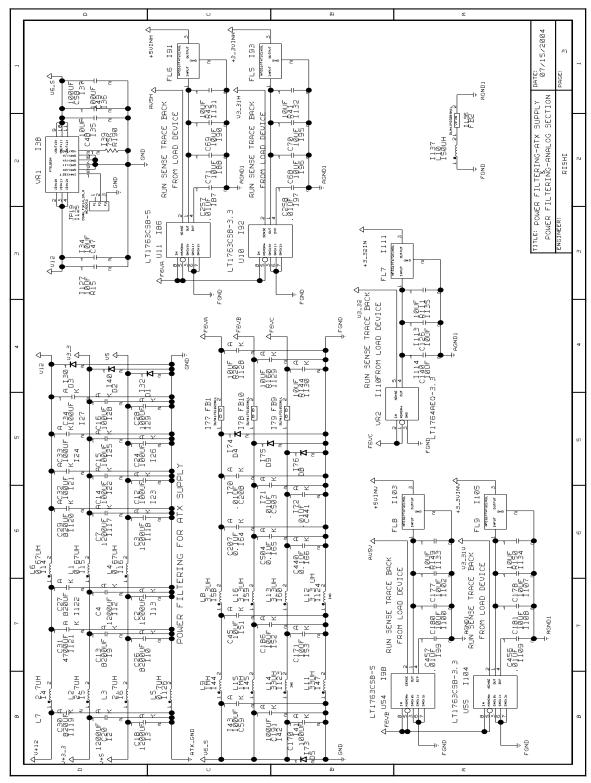

| 6.2  | ATX Power filtering                                                 |  |

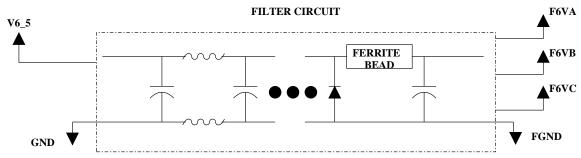

| 6.3  | Power filtering for Digital section                                 |  |

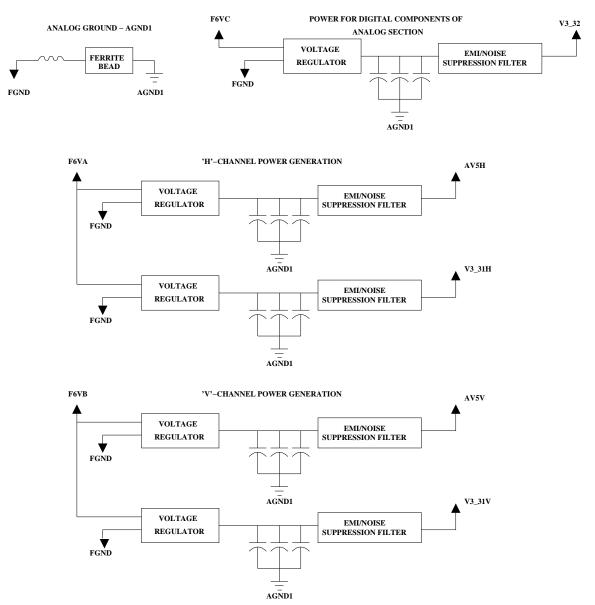

| 6.4  | Power filtering for Analog section                                  |  |

| 6.5  | Voltages for Analog section                                         |  |

| 7.1  | Microcontroller Clocking mechanism                                  |  |

| 7.2  | Clock distribution mechanism - Clock Fanout Buffer                  |  |

| 7.3  | (Adapted from Luko Krnan)                                                             |

|------|---------------------------------------------------------------------------------------|

| 7.4  | Clock distribution mechanism - FPGA2 PLL clock distribution (Adapted from Luko Krnan) |

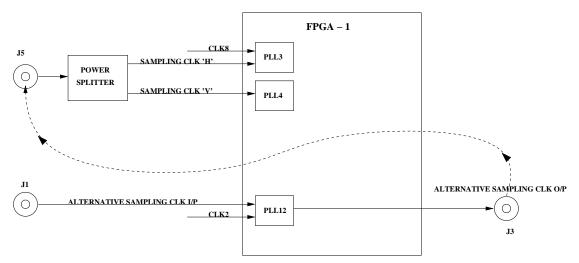

| 7.5  | Clock distribution mechanism - Sampling Clock clock distribution mechanism            |

| 9.1  | Simulation Setup                                                                      |

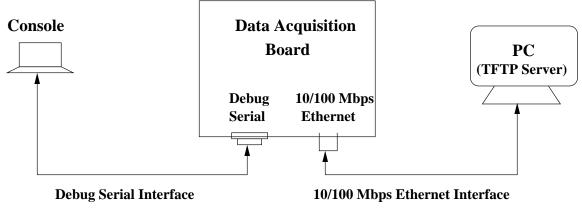

| 11.1 | Test setup - Boot code and 10/100 Mbps Ethernet                                       |

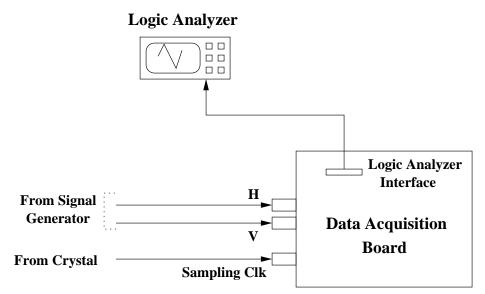

| 11.2 | Test setup - FPGA1 and Analog section                                                 |

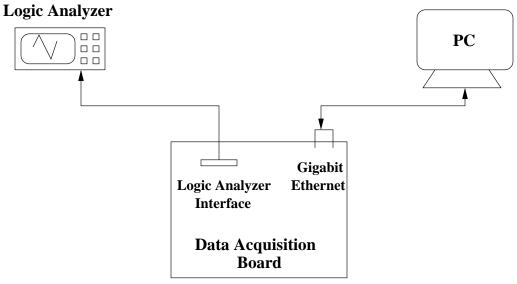

| 11.3 | Test setup - FPGA2 and Gigabit Ethernet Interface 67                                  |

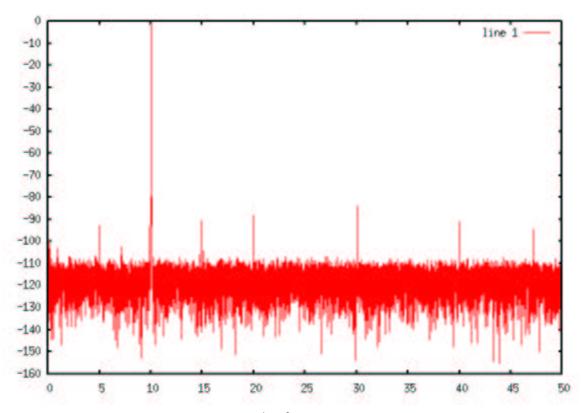

| 12.1 | Analog section test result                                                            |

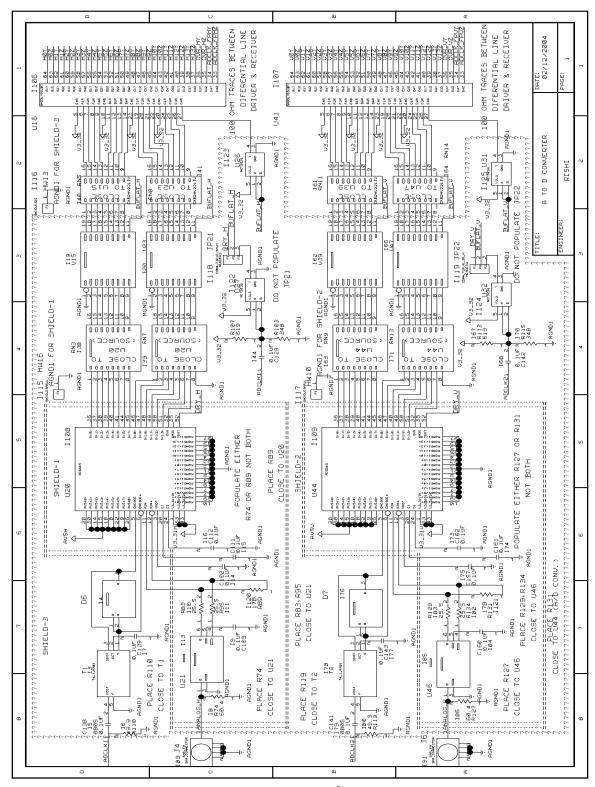

| A.1  | AtoD Converter                                                                        |

| A.2  | Radar Interface & Power filtering (Analog section)                                    |

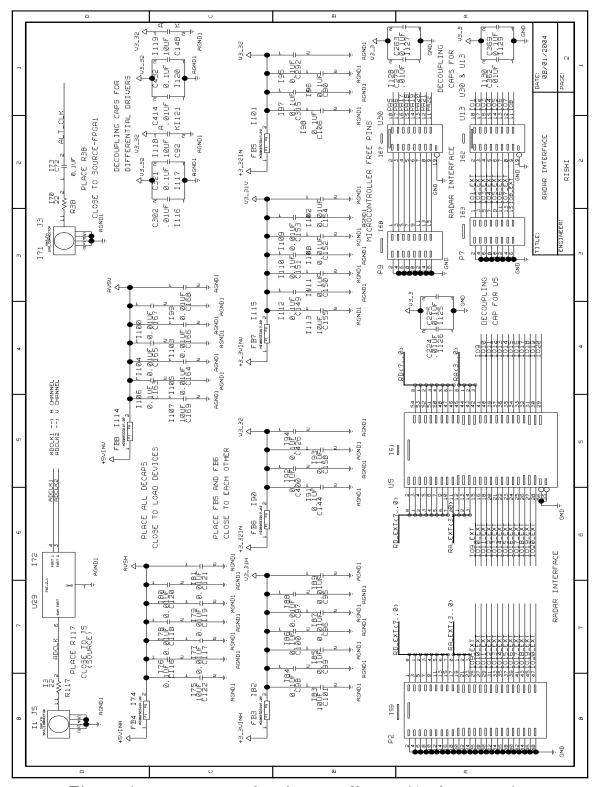

| A.3  | Power filtering (Analog section)                                                      |

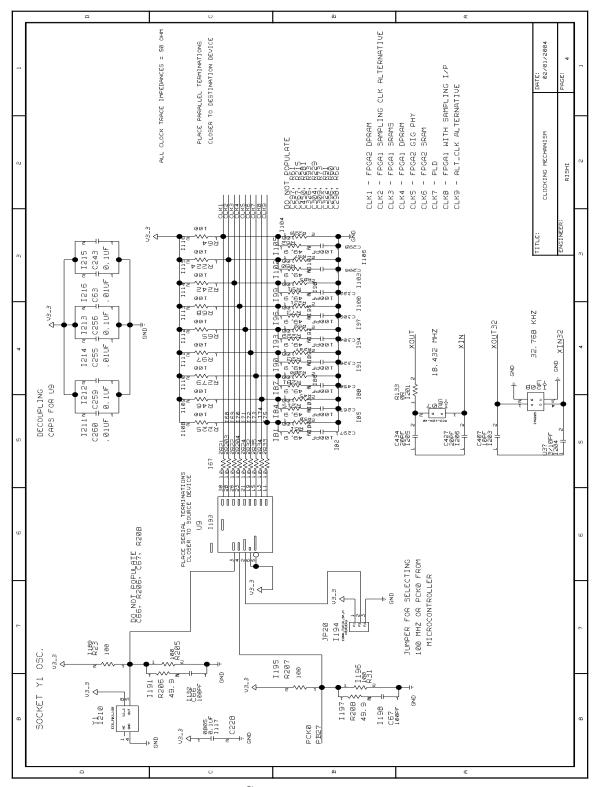

| A.4  | Clock distribution mechanism                                                          |

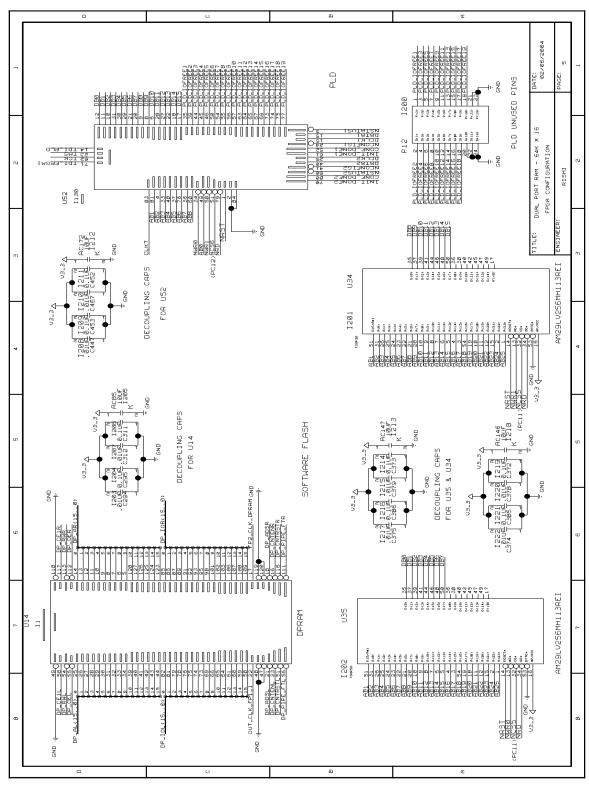

| A.5  | Dual-Port RAM and FPGA Config. (PLD & FLASH)                                          |

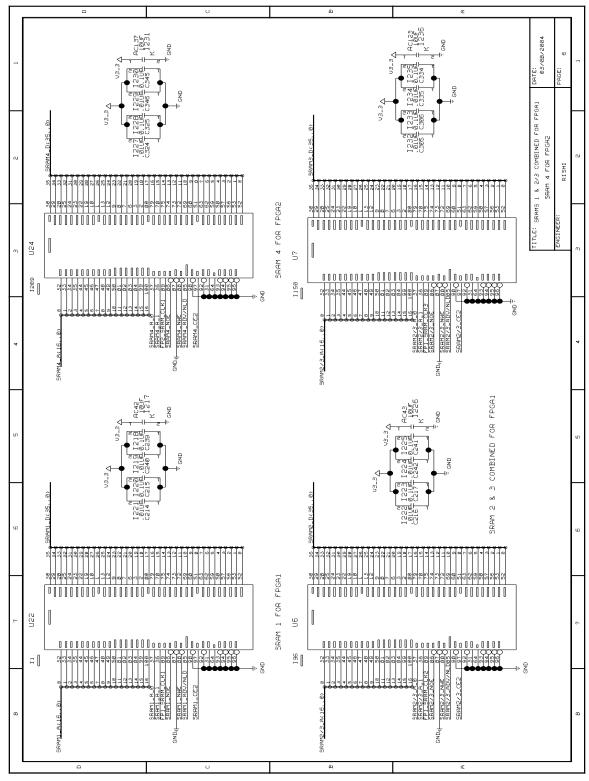

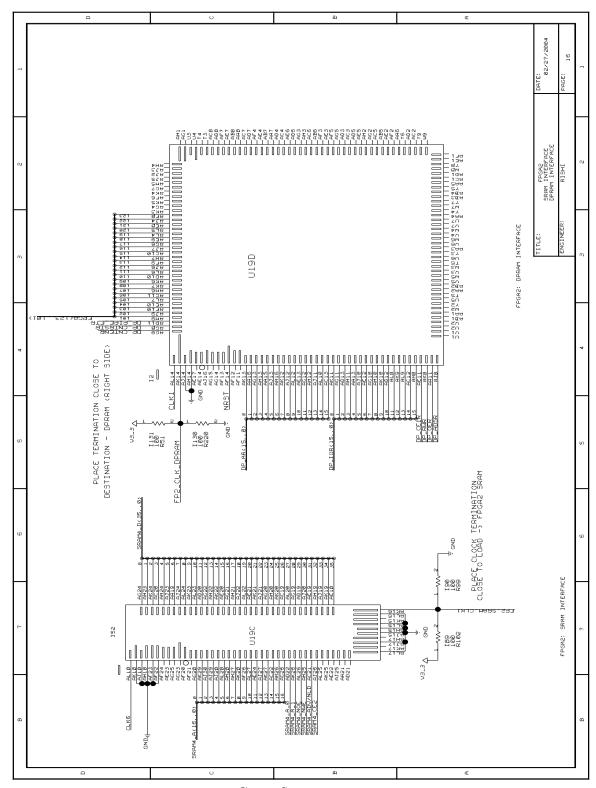

| A.6  | FPGA SRAMs                                                                            |

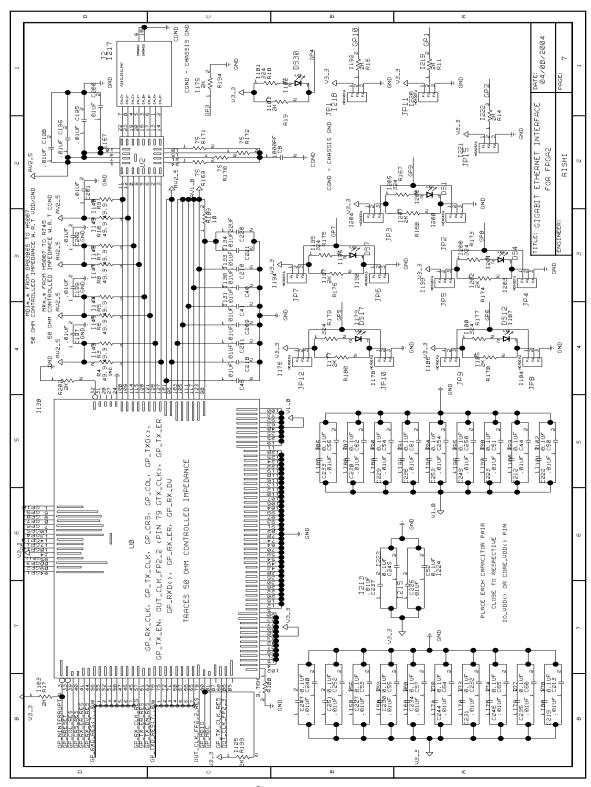

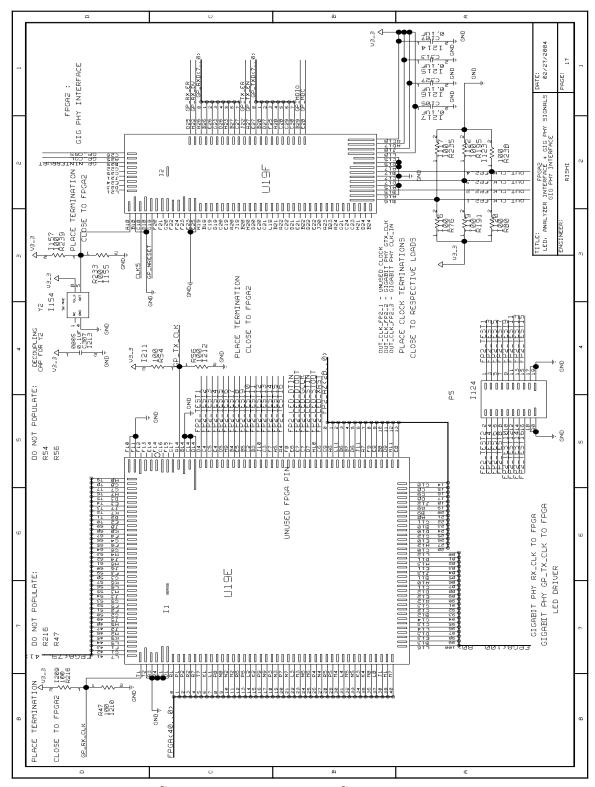

| A.7  | Gigabit Ethernet Interface                                                            |

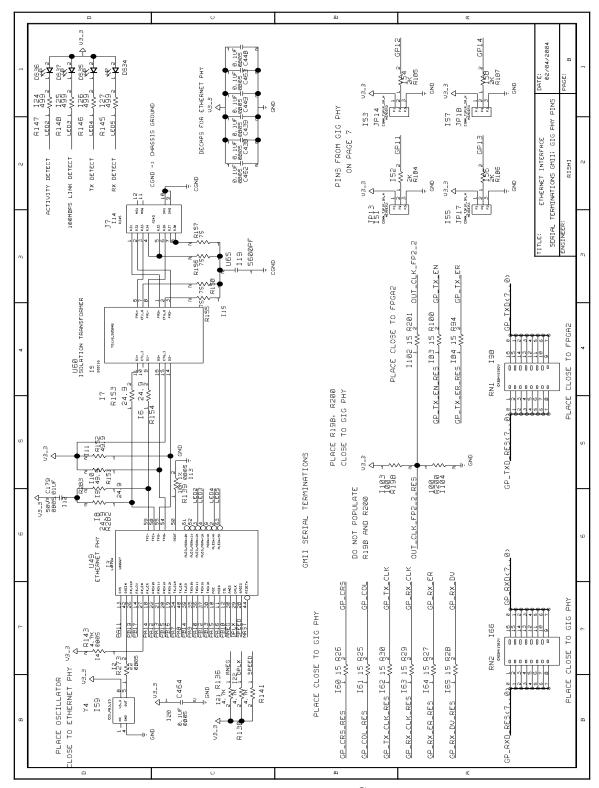

| A.8  | Ethernet Interface & GMII terminations                                                |

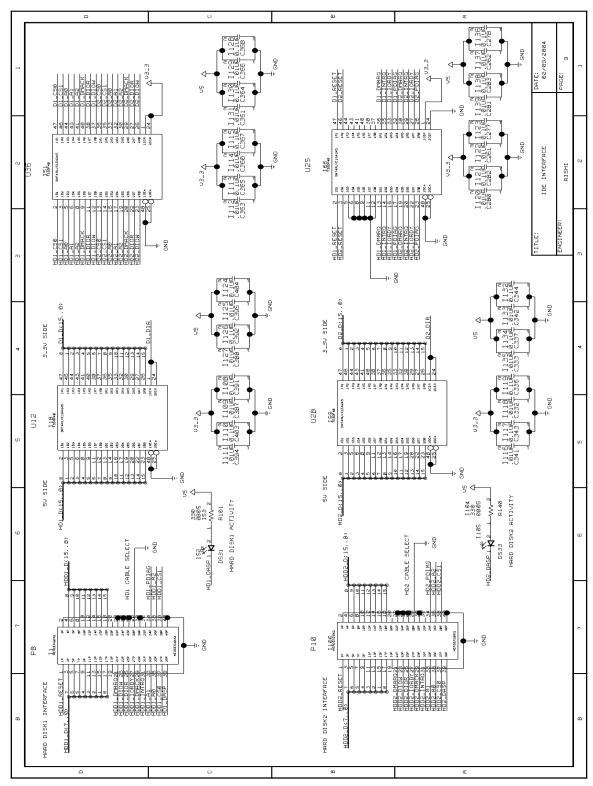

| A.9  | IDE Interface                                                                         |

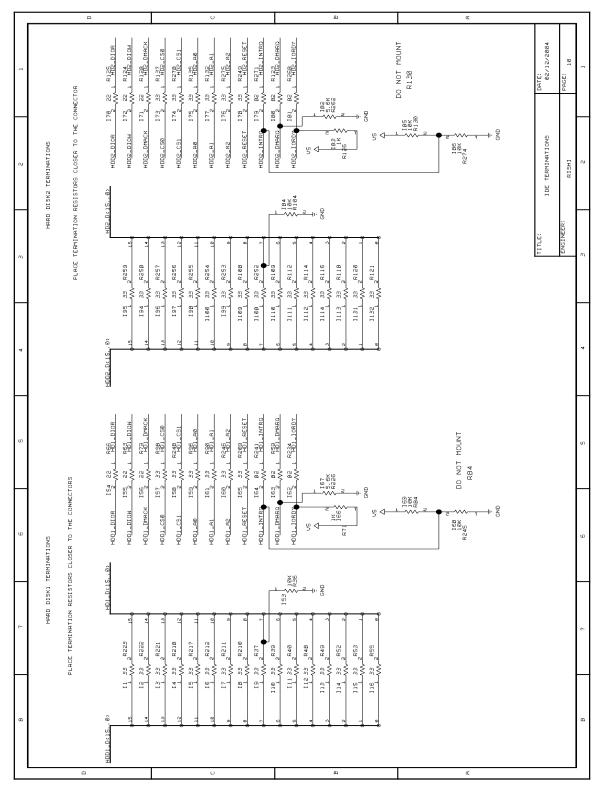

| A.10 | IDE Terminations                                                                      |

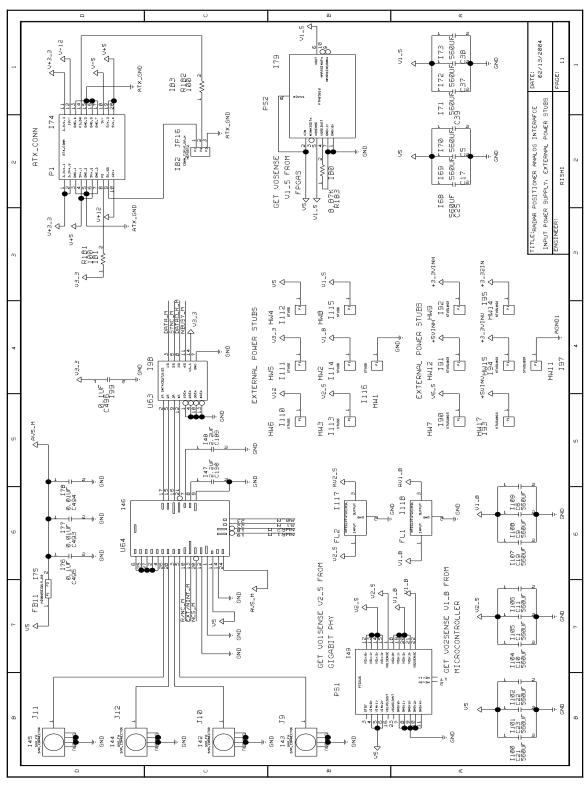

| A.11 | Radar positioner analog channel, Input Power supply and External Power stubs          |

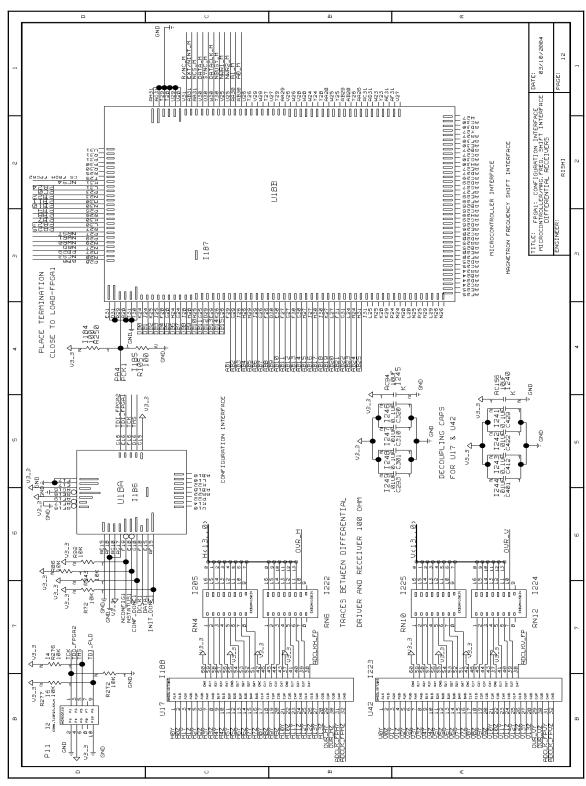

| A.12 | and Diferential Receivers                                                  | 88  |

|------|----------------------------------------------------------------------------|-----|

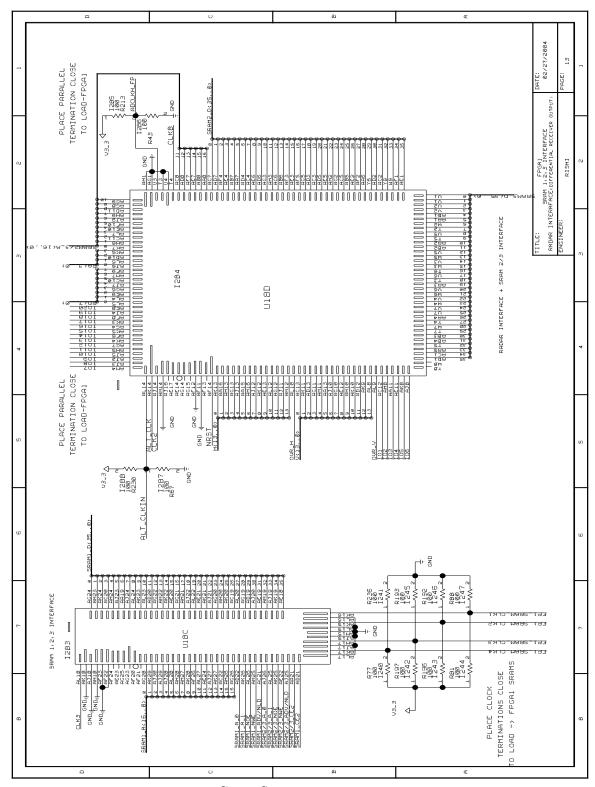

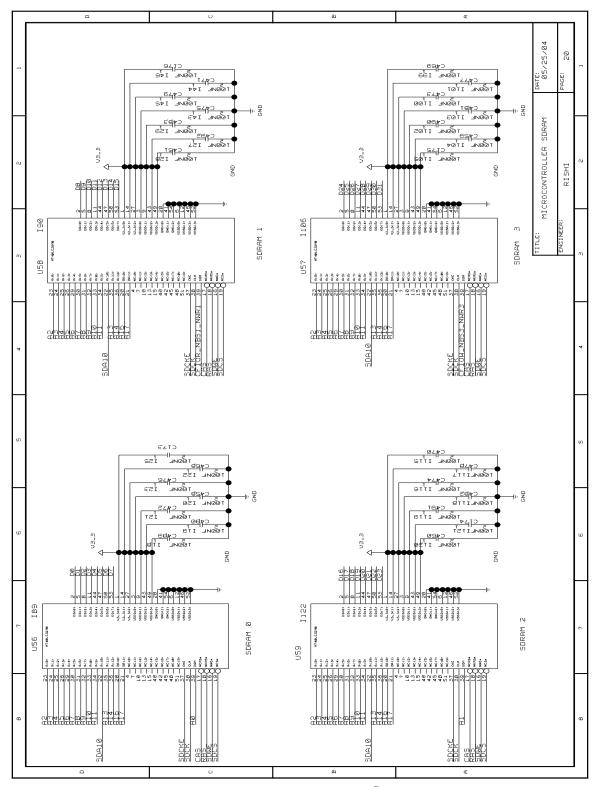

| A.13 | FPGA1: SRAM 1,2 & 3 and Radar interface                                    | 89  |

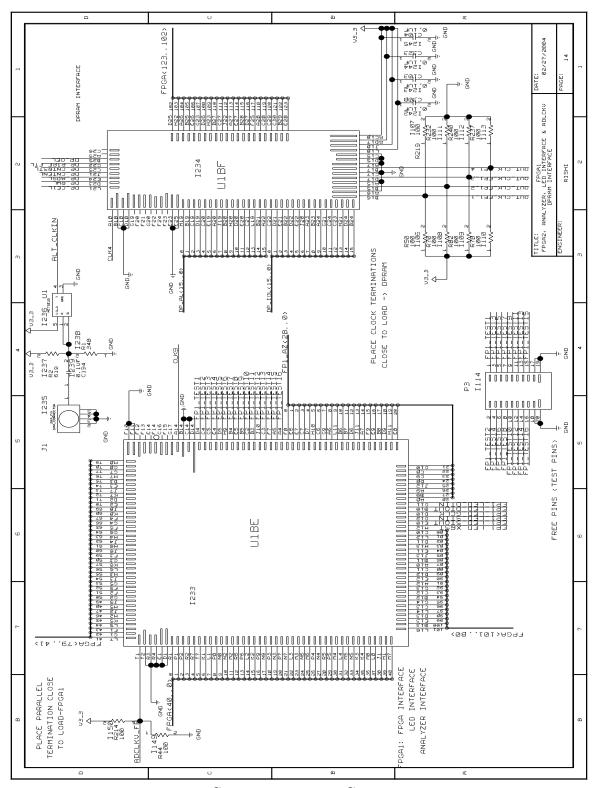

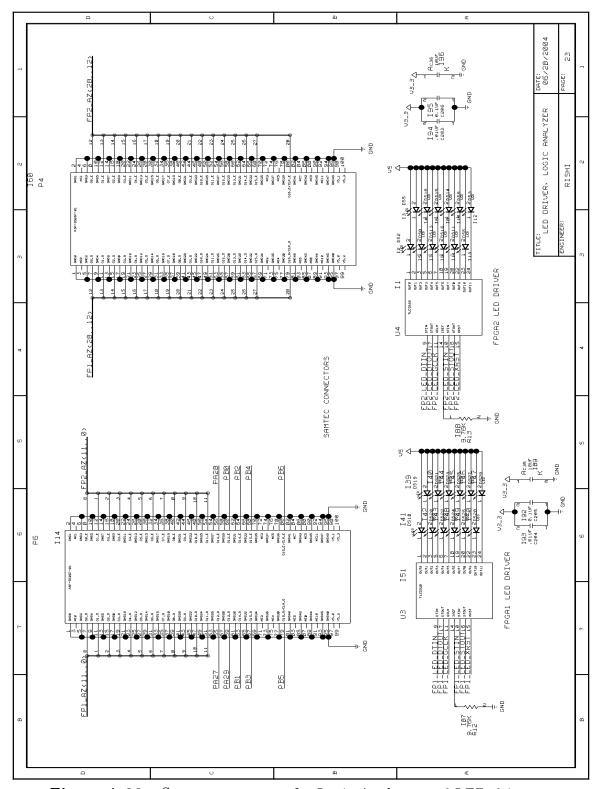

| A.14 | FPGA1: Analyzer, FPGA2 and LED interface                                   | 90  |

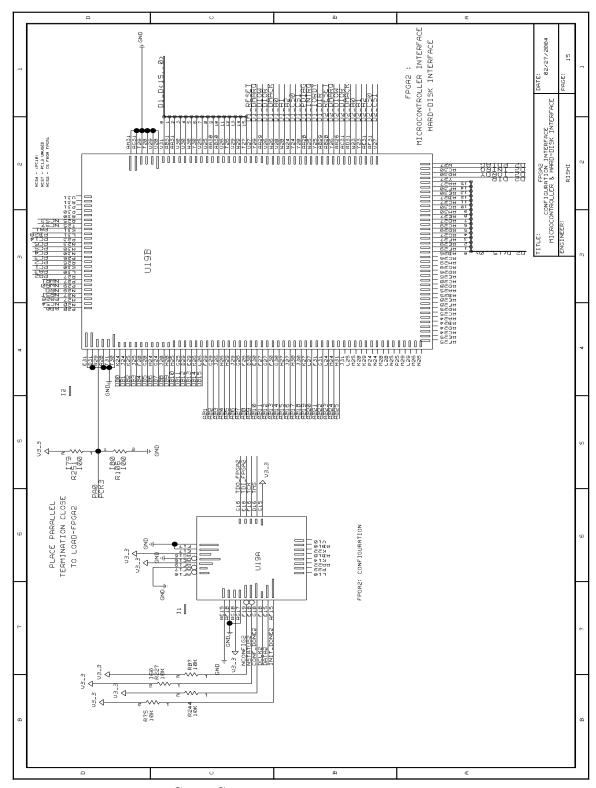

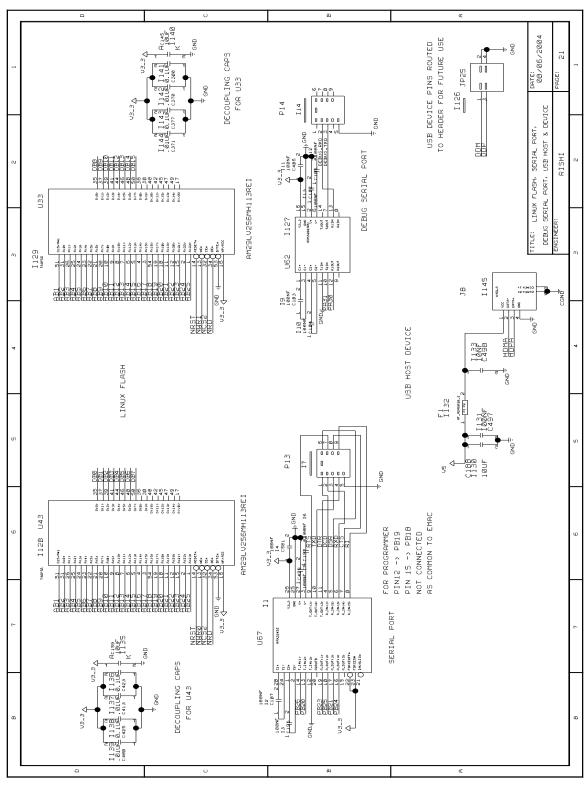

| A.15 | FPGA2: Configuration, Microcontroller and IDE interface                    | 91  |

| A.16 | FPGA2: SRAM and DPRAM interface                                            | 92  |

| A.17 | FPGA2: Analyzer, LED and Gigabit Ethernet PHY interface                    | 93  |

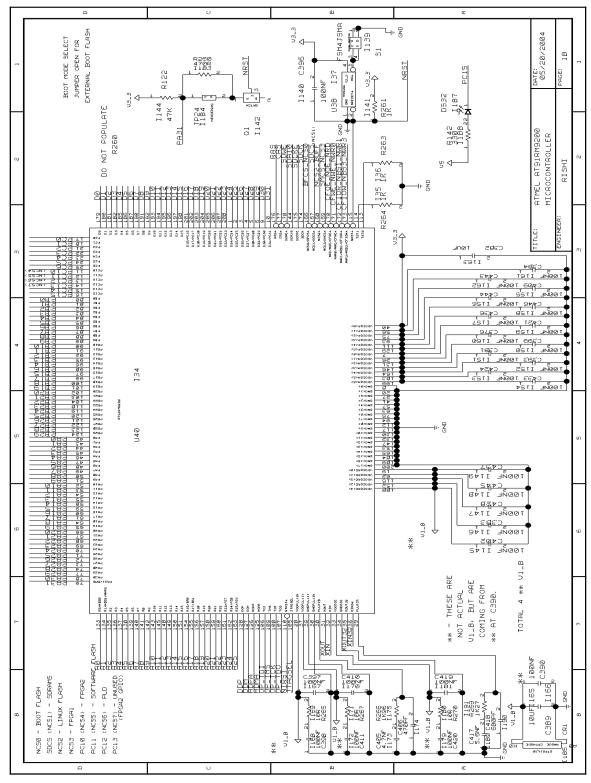

| A.18 | AT91RM9200 - Microcontroller                                               | 94  |

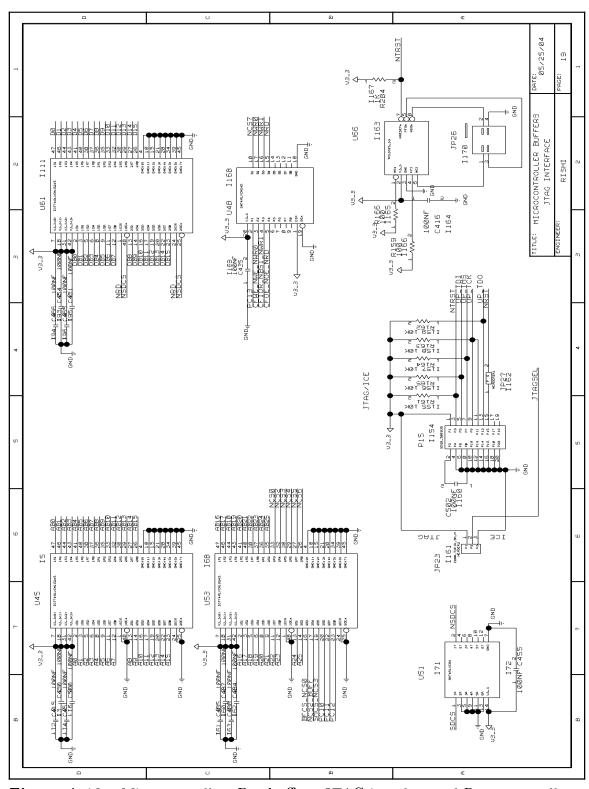

| A.19 | Microcontroller: Bus buffers, JTAG interface and Reset controller. 95      |     |

| A.20 | Microcontroller SDRAMs.                                                    | 96  |

| A.21 | Linux FLASH, Serial & Debug Serial ports and USB Host & Device interfaces. | 97  |

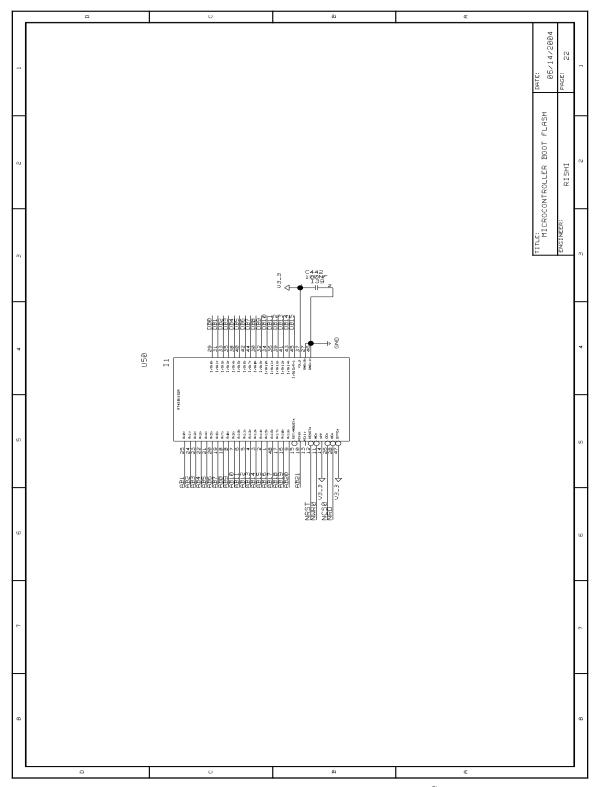

| A.22 | Microcontroller Boot FLASH                                                 | 98  |

| A.23 | Samtec connectors for Logic Analyzer and LED drivers                       | 99  |

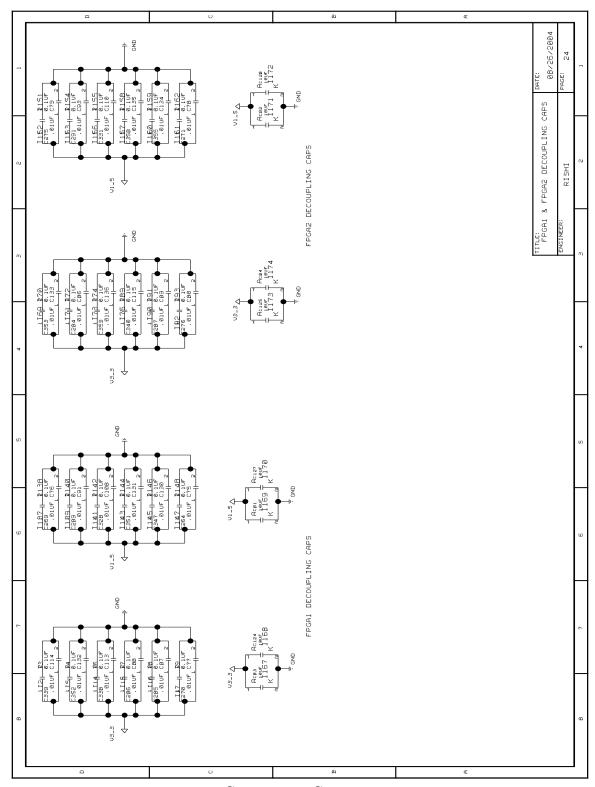

| A.24 | FPGA1 and FPGA2 decoupling capacitors                                      | .00 |

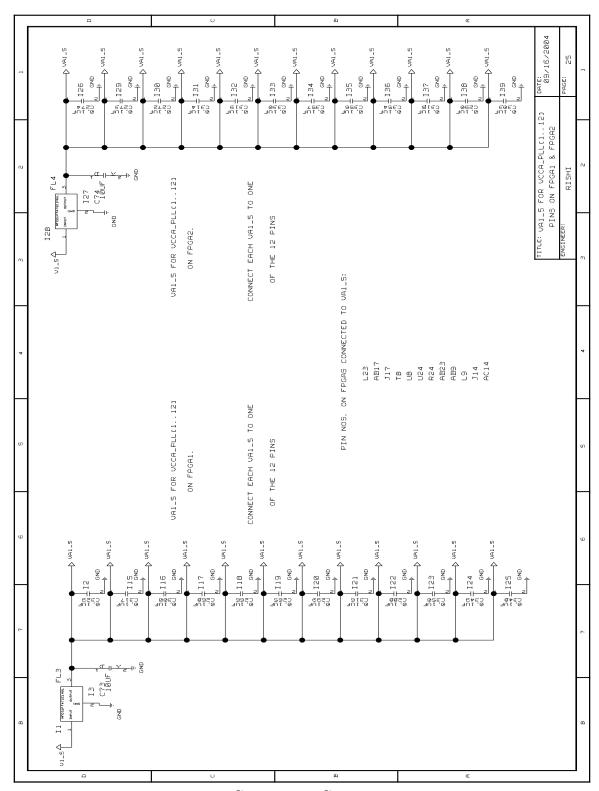

| A.25 | FPGA1 and FPGA2 PLL power filtering                                        | .01 |

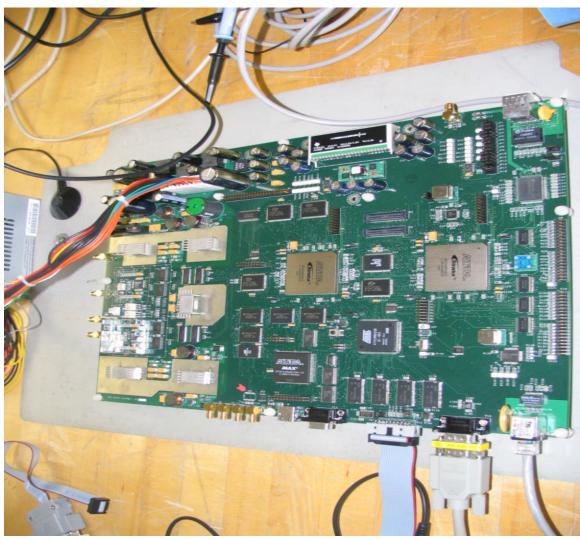

| B 1  | Data Acquisition Board                                                     | 02  |

## CHAPTER 1

## INTRODUCTION

Data acquisition systems are an integral part of radar applications [26] [12] [22]. The raw analog data acquired by a radar system can be cast into meaningful, intelligible data packets only after it has been digitized and processed and can then be stored at suitable locations. All these processes should be fast enough to support high rate analog data inputs [13] and should be completed in real-time, especially for applications such as atmospheric sensing, involved in critical weather predictions such as tornado detection and warning [14]. The processed data requires bulk-storage devices for post-processing and analysis. In the event the storage resources are not accessible locally, a network interface is needed to access these remote bulk-storage devices. Further, these processes require various control signals and parameters, which necessitates an efficient, reliable communication system for the acquisition unit. All the above functions coupled together define the purpose and importance of a data acquisition system in a radar application.

In the past, the devices and components available for constructing a data acquisition system could not support high data rates, complex processing needs, large storage capacities and high-speed reliable network interfaces [7]. The problem was further aggravated due to the large physical dimensions and power consumption of the analog and digital components required. With technological advancements, high-speed devices with limited physical dimensions and excellent power performance are now available off-the-shelf. With the arrival of high speed Ethernet and Gigabit Ethernet interfaces, reliable, high-speed network support is also possible. All these improve-

ments have made the development of a complete data acquisition system with high processing power and a low form-factor an achievable proposal.

The two most commonly used devices on a data acquisition system are Field Programmable Gate Arrays (FPGAs) or general purpose processors and microcontrollers [27]. A well-planned design with well-organized distribution of tasks between these devices paves the way for a state-of-the-art data acquisition architecture. Specialized hardware for high-speed data processing tasks and operations requiring fine-grained timing control can be effectively modeled by a combination of application specific hardware and a reconfigurable processor, which adds the dimension of reconfigurability to the architecture and allows for system flexibility. High-level functions that include administrating and synchronizing the working of all these devices can be achieved by the use of a microcontroller. Thus, an intelligent arrangement of application specific hardware and reconfigurable processors, administered by a microcontroller, as developed in this project, can create a highly effective and powerful data acquisition system.

For this thesis project, we have developed a data acquisition system to meet the requirements of an atmospheric monitoring radar application - the Distributed Collaborative Adaptive Sensing (DCAS) radars [13], being developed at the Engineering Research Center for Collaborative Adaptive Sensing of the Atmosphere (CASA) at the University of Massachusetts-Amherst. This radar system is being developed with the aim of timely prediction and detection of tornados, hazardous weather conditions and floods. The data acquisiton architecture has been implemented using off-the-shelf components such as ARM (Advanced RISC Machine) based Microcontroller and FP-GAs. These two components comprise the main processing and controlling power of this architecture. A variety of communication interfaces have been incorporated in the design for the ease of controlling the system and routing and storing data at suitable locations. A careful distribution of processing requirements and communication

interfaces between the microcontroller and the FPGAs has been designed. Radar data processing, network interface via a Gigabit Ethernet, low-level hard-disk control etc. have been assigned to the FPGAs. High-level operations like hard-disk storage handling, radar control network upload/download via Fast Ethernet, USB etc. has been confined to the ARM microcontroller.

Before fabrication, the functionality of the data acquisition system design was verified through simulations. To test the fabricated board, dummy FPGA algorithms and ARM diagnostic software were written to test various hardware interfaces on the board. The data acquisition board system and its various interfaces have been tested. This system now ready to be integrated with the DCAS radars and applied to a real-time environment.

This report is organized as follows. Chapter 2 describes previous work done in this field and the application of this design. The requirements and specifications set by the radar unit for this data acquisition system are listed in Chapter 3. Chapter 4 describes an architecture to meet these requirements. The configuration, functioning and operations performed by each section of this design and the system as a whole are discussed in detail in Chapter 5. The power filtering mechanism and the clock distribution scheme developed for this system are discussed in chapters 6 and 7 respectively. Chapter 8 pertains to the bootup strategy employed for different components included in this design. This will be followed with a discussion in Chapter 9, on the steps followed for designing and simulating the system. Chapter 10 lists the configuration strap settings needed to be performed on the hardware system. The testing and debugging strategy that was employed for the fabricated boards has been dealt with in chapter 11 followed by the results that were generated during this testing/debugging phase in chapter 12. This report concludes in Chapter 13, with a summary of the ideas and goals driving this project and a few suggestions on future tasks that can be implemented.

## CHAPTER 2

## BACKGROUND

## 2.1 Radar System Overview

The proposed data acquisition system will be integrated with the Distributed Collaborative Adaptive Sensing (DCAS) radars [13]. DCAS systems involve low-cost, small radars deployed on cell phone towers or other infrastructure and designed to observe and detect hazardous weather and floods. Distributed refers to the use of a dense network of radars capable of high spatial and temporal resolution. These systems will operate collaboratively within a dynamic information technology infrastructure, adapting to changing conditions in a manner that meets competing needs of end users; the government, private industry, and the public. Second generation DCAS systems will focus on volumetrically sensing wind and thermodynamic variables in a pre-storm environment, or clear air. A third instantiation of DCAS will involve mobile volumetric sensors that can communicate with ground-based sensors. Thus, studying and monitoring the lower troposphere, the part of the atmosphere that contains most natural and man made hazards, for accurate and timely tornado and flood detection and alarms is the goal of these radars.

For effective and timely weather hazard predictions, the data being collected by these radars need to be digitized, processed into packets of concise, succinct data and dispatched to the end user in real-time. These are the fundamental goals that drive the design of a data acquisition system for such radars.

The proposed system equipped with high-density, high-performance, fast, reconfigurable hardware (FPGAs) [3], an intelligent, embedded, feature rich, master-

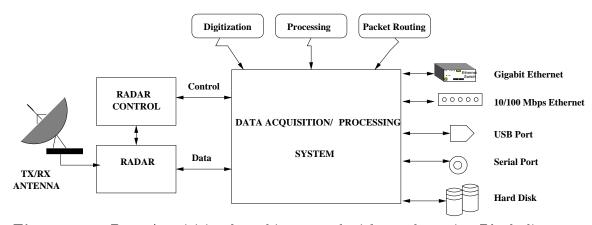

controller (Microcontroller) [9] and contemporary high-speed communication interfaces like Gigabit and 10/100 Mbps Ethernet, Universal Serial Bus (USB), Serial Ports and Integrated Drive Electronics (IDE), is ideally suited for the intended application. A high-level representation of a data acquisition system integrated in a radar unit is as shown in figure 2.1

Figure 2.1. Data Acquisition board integrated with a radar unit - Block diagram.

## 2.2 Background work

Prior work on designing data acquisition systems for weather and ocean monitoring radar systems include [26] and commercial solutions like [15]. The system developed in [26] is equipped with reconfigurable hardware (FPGAs), processor based system control and has communication interfaces such as a 10/100 Mbps Ethernet, serial ports and IDE channels. The 12 bit 65 MSPS AtoD input channels implemented in this system do not meet the 14 bit 100 MSPS requirement [13] of this application. Further, processor speed (processor running at 50 MHz), memory and data output interfaces lack the ability to cope with the high data rates [13] and complex signal processing algorithms [17] required for implementation on bulk data inputs for this application. Commercial solutions like [15] have high-density, high-speed Xilinx Virtex-II FPGA modules. For converting analog inputs from a radar to the digital

domain, this product needs to be integrated to daughter PCBs that add on to the cost and the complexity of the system. USB and parallel port interfaces are the only data output channels available. The data acquisiton architecture developed for this project costs about USD 6,240 per board. Thus, the commercial solutions are not only expensive (USD 15,500 for the basic system and an additional USD 1,100 for two A to D interface daughter boards) but also lack the superior performance and ease of control rendered by a microcontroller and the presence of high-speed communication interfaces, such as the Gigabit Ethernet interface, a necessity for the intended application.

## CHAPTER 3

## RADAR SYSTEM SPECIFICATIONS

## 3.1 Radar System

Data acquisition systems often interface with radar units to form a complete Ocean/Atmosphere monitoring radar system [26] [12] [16] [22]. Predicting tornados [13] is the main purpose of this application. For timely and effective tornado warnings the radar analog data needs to processed by a low latency (in the order of a millisecond) data acquisition system. Thus, real-time data processing is a must for the proposed acquisition system. Initial estimates state that the radar will generate data at a rate of about 100 Mbits per second [13]. For useful information to be extracted from the analog data, complex signal processing algorithms must be implemented to process the data [17]. The basic requirement is to develop a powerful, high-speed data acquisition system with abundant resources to support complex signal processing algorithms and provide standard, high-speed communication interfaces for processed data routing. From the user point of view, it should be a low-cost system made from off-the-shelf components with ease of control and programmability.

## 3.2 Radar Terminology Definitions

Before proceeding to the technical specifications and parameters set by the radar unit for this acquisition system, this section defines certain radar related technical terminologies.

1. Pulse Repetition Frequency (PRF): PRF is the frequency at which radar pulses are transmitted [26].

- 2. Range Gate: The transmitted pulses reflect back from the target and need to be sampled in the window between two transmitted pulses. The samples within the sampling window is called the Range Gates [26].

- 3. Range Resolution: Range resolution is defined as the distance between two consecutive radar samples [26].

## 3.3 Radar Specifications

Following are the specifications [13] set by the radar unit that have to be met by the proposed architecture.

- 1. Support real-time data acquisition, processing and storage.

- 2. Support data rates of about 100 Mbits per second, generated by the radar.

- 3. Support dual channel inputs to accept 10 MHz 30 MHz IF signals.

- 4. Perform digital demodulation, filtering and decimation.

- 5. Perform digital coherent-on-receive magnetron phase correction.

- 6. Support pulse-pair and/or 128-point FFT algorithms, with a raw I and Q pass-through mode, for 300 600 range gate modes.

- 7. Support 100m and 200m range sampling modes.

- 8. Capable of averaging 1 10,000 pulses (non-coherent).

- 9. Support digital frequency drift compensation with accuracy of 2 kHz.

## 3.4 Data Acquisiton System Features

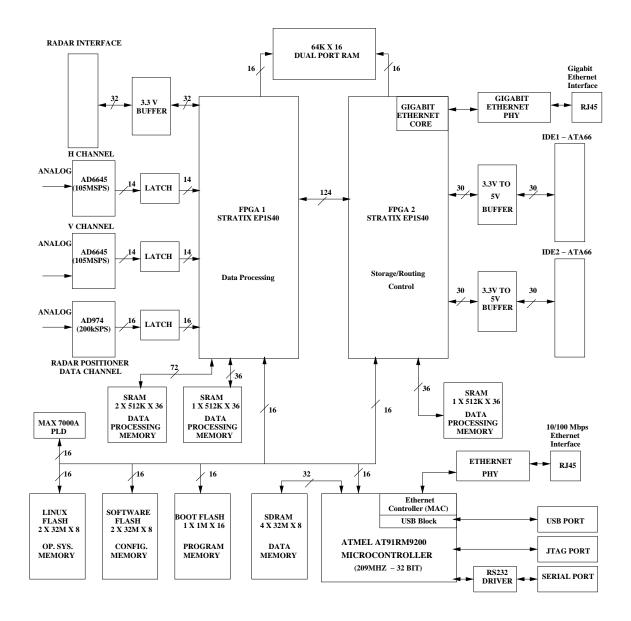

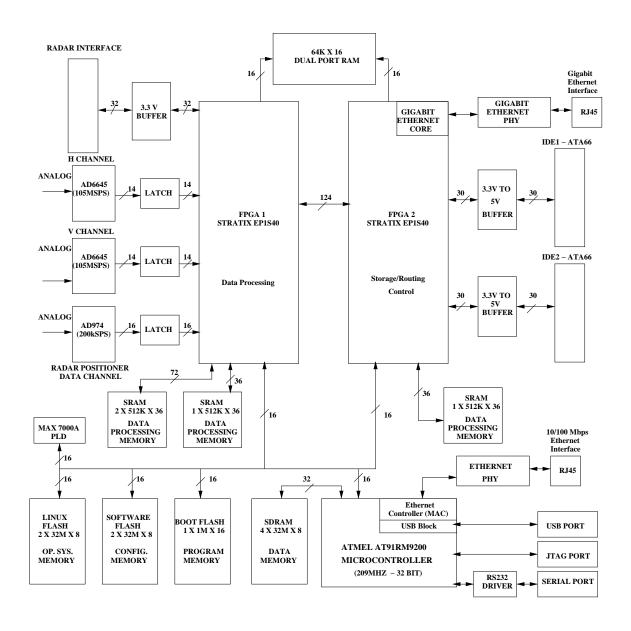

A list of features supported by this design with the objective of meeting the radar-defined specifications and requirements is given below. The block diagram of the proposed architecture is shown in figure 3.1.

Figure 3.1. Block Diagram of Data Acquisition System.

- 1. Two 14 bit 105 MSPS Analog to Digital (A to D) input data channels to support Horizontal (H) and Vertical (V) components of input data.

- 2. Additional 16 bit 200KSPS auxiliary A to D channel for radar positional data or other radar related input information.

- 3. Off-the-shelf, high speed, Altera Stratix FPGAs with abundant internal memory (41,250 Logic elements and 3,423,744 RAM bits), 14 DSP blocks and 112

9x9 bit multipliers [3] to support fast, powerful signal processing algorithms [17] such as Discrete Fourier Transform (DFT), Finite Impulse Response (FIR) and Infinite Impulse Response (IIR) filters and Coordinate Rotation Digital Computer (CORDIC) for implementing coherence on receive algorithms. Reconfigurable hardware (FPGAs) imparts high performance and flexibility [27] to the system.

- 4. ARM embedded processor acting as the master control to the system adding to the ease of control and flexibility of the design.

- 5. On-board memory resources in the form of Flash chips, SDRAMs (Synchronous Dynamic Random Access Memory), SRAMs (Static Random Access Memory) and DPRAM (Dual Port Random Access Memory) to support complex signal processing algorithms on large data quantities.

- 6. Standard contemporary communication interfaces such as Gigabit Ethernet, 10/100 Mbps Ethernet, Universal Serial Bus (USB) port, Serial ports and IDE (Integrated Drive Electronics) channels.

- 7. An interface to the radar for control signals and sampling information.

- 8. Joint Test Action Group (JTAG) port and a dedicated Universal Asynchronous Serial Transmission (UART) debug channel to connect to a PC for testing and debugging the system.

- 9. Use of off-the-shelf, easily available, commonly used components.

In context to the specifications set-forth by the radar system in section 3.3, these resources shall meet the requirements as enumerated below.

1. Fast hardware components, intelligent control and abundance of memory resources will help support real-time data acquisition, processing and storage and

implement signal processing algorithms such as digital demodulation, filtering and decimation, digital coherent-on-receive magnetron phase correction and digital frequency drift compensation with ease.

- 2. Two A to D channels, each 14 bit, capable of supporting 105 MSPS, can support data-rates of upto (14 bit x 105 MSPS x 2 channels) 2.94 Gbps as compared to the 100 Mbps required by the radar system.

- 3. The A to D channels can support dual channel inputs to accept 5 MHz 270 MHz IF signals [6], which exceeds the dual channel inputs to accept 10 MHz 30 MHz IF signal requirement of the radar system.

- 4. This architecture can support modes of upto 1024 range gates with 256 point FFT (with 50% overlap) [17]. This exceeds the required 128-point FFT algorithms for 300 600 range gate modes expected by the radar system.

- 5. With an input bandwidth of 52.5 MHz, this system can support a minimum range of 3 meters (52.5 MHz = 19.04 ns. Total distance = 19.04 ns x speed of light = 5.71 meters. Thus, Range = 3 meters approximately). This exceeds the requirement of a minimum range of 100 meters set by the radar system.

- 6. This system is capable of averaging 1 to 2<sup>48</sup> pulses, the upper limit set by a 48-bit accumulator utilized for the averaging. This is far better than the averaging of 1 10,000 pulses as expected by the radar unit.

Thus, we observe that this data acquisition system supersedes the requirements of the radar unit and is ideally suited for high data rate, real-time data acquisition and processing needs.

## CHAPTER 4

## DATA ACQUISITION SYSTEM ARCHITECTURE

The architecture of this board has been designed considering the requirements defined in Chapter 3.

The block diagram of the proposed architecture is re-drawn in figure 4.1. The two main processing modules of this architecture are the Stratix EP1S40 FPGAs [3], namely FPGA1 and FPGA2, which are being controlled and supervised by an Atmel AT91RM9200 [9] Microcontroller. FPGAs have been shown to be highly effective in performing time varying tasks such as data compression, digital signal processing and communication related operations [27]. For the proposed design, FPGA1 is the data processing center while FPGA2 is the final data product distribution center. The following discussion briefly explains the data and control flow through the proposed architecture.

## 4.1 Radar Interface and Analog Section

The data acquisition system has a radar interface that includes three analog data input channels, sampling clock input channel and a digital interface to feed sampling and control parameters to the system. The board consists of two 14-bit A to D channels (H and V), each of which can sample data at a maximum rate of 105 MSPS and form the two primary analog data input channels. The digital outputs of these A to D channels are latched before being fed to FPGA1 to reduce the critical path [23] and to compensate for board delays. A separate channel is utilized to provide the sampling clock for these A to D conversions. The design also has a 16-bit A to

Figure 4.1. Block Diagram of Data Acquisition System.

D channel as the third analog input channel. This interface can sample data at a maximum rate of 200 KSPS. This is an auxiliary analog channel that can be used to feed radar positioner data to FPGA1. This data can be used to control the positioning of the radar or can be used to add radar positioner information to data [13]. The H and V A to D channels and the sampling clock input channel form the all important, high-speed analog section of this architecture. Inorder to provide noise immunity to

this section, the ground plane of the analog section has been isloated from the ground plane of the digital section. A differential transmitter-receiver combination between the A to D latched outputs and FPGA1 inputs provides a bridge between these two isolated sections of the design. Further, a 32-bit digital interface, a part of the radar interface, can be used to acquire data processing and control parameters from the radar and feed header data to FPGA1. This digital interface is isolated from FPGA1 using 3.3 V buffers.

## 4.2 FPGA1 and FPGA2

FPGA1, the data processing center of this design, receives sampled data over its differential interface to the A to D channels. Various signal processing algorithms, for radar data processing, can be built into FPGA1. A 72-bit high-bandwidth interface to SRAM memory modules assists FPGA1 in implementing high-speed, complex signal processing algorithms.

Both the FPGAs interface with a Dual Port RAM (DPRAM). The DPRAM acts as an intermediate memory module between them. FPGA1 stores a processed packet of data in the DPRAM while working on the next packet. FPGA2 can simultaneously read these processed packets out of the DPRAM for distributing over an output channel.

As mentioned above, FPGA2 is the data distribution control module. It selects one of the different available output channels and routes the processed data packets to the end user. It has a Gigabit Ethernet core [20] embedded in it along with two IDE hard disk controllers [26], in accordance to ATA5/ATA66 standards [29]. An external physical layer device is coupled between the embedded Gigabit Ethernet core and an external connector (RJ45) to form a Gigabit Ethernet interface. This interface, which can support a maximum data transfer rate of 1 Gbps [20], forms the processed-data-output channel for the proposed system. In the event of a network breakdown or

Gigabit Ethernet interface unavailability, the IDE interfaces can be used as a source for temporary data backup.

A 124 bit digital interface between the two FPGAs can be utilized to communicate data processing/routing related parameters or control signals between them. As in the case of FPGA1, FPGA2 also has access to external SRAM modules to facilitate large data storage capacities required especially during the execution of signal processing algorithms.

#### 4.3 Microcontroller

The Atmel ARM based Microcontroller - AT91RM9200 [9] acts as the master control for the system. This chip, which can operate at a maximum speed of 209 MHz (200 MIPS at 180 MHz), is a high performance microcontroller solution for communication based, real-time embedded applications. The microcontroller controls all the operations being performed by the two FPGAs by programming their respective internal registers. It has a built in 10/100 Mbps Ethernet Media Access Controller (EMAC). A physical layer device (PHY) connected between the microcontroller and an external connector (RJ45) forms an Ethernet interface that can support a maximum data transfer rate of 100 Mbps. This interface can be utilized to download data for testing and debugging purposes and to feed control instructions to the system over the network. It also supports a variety of other standard communication interfaces such as a serial interface (via RS232 transceiver and external connector), a dedicated Universal Asynchronous Serial Transmission (UART) debug channel and a Universal Serial Bus (USB) interface, in addition to a standard JTAG (Joint Test Action Group) port. These interfaces can be used for a variety of communication, debug and emulation operations. The microcontroller has access to external FLASH and SDRAM (Synchronous Dynamic RAM) memory modules that act as program and data memories respectively. For the ease of controlling the microcontroller and supporting all available communication interfaces, an operating system [10] has been ported to the microcontroller.

An additional function of the microcontroller is to control the configuration process of the two FPGAs. This architecture supports two FPGA configuration schemes [4]. The FPGAs can either be configured through a dedicated JTAG interface or through an Altera Programmable Logic Device (PLD) [5]. Under the latter approach, a separate 'Software' FLASH is responsible for storing the FPGA configuration files. The PLD and the 'Software' FLASH are controlled by the microcontroller. Thus, by utilising the microcontroller based 10/100 Mbps Ethernet interface, an additional feature of network-based reconfiguration of the FPGAs can be attained.

## CHAPTER 5

#### SYSTEM OPERATION

This chapter pertains to the different building blocks of this system, their operation and their functionality.

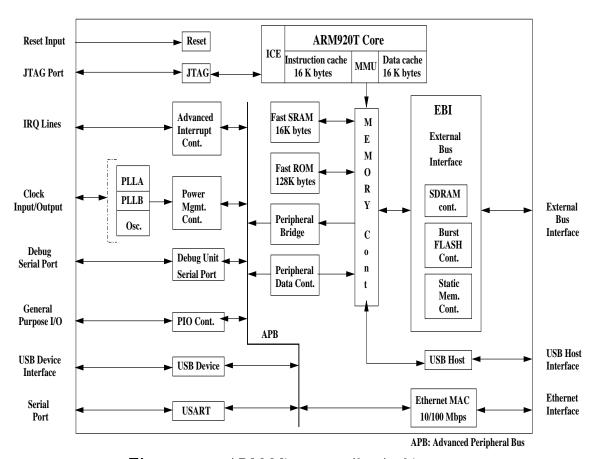

#### 5.1 ARM Microcontroller

As mentioned in the earlier chapters, the microcontroller performs the function of supervising the operation of this system and is an important building block in this architecture. The internal architecture of the ARM microcontroller is shown in figure 5.1.

#### 5.1.1 Introduction

This architecture uses AT91RM9200, an ARM based Microcontroller by Atmel [9]. This microcontroller is a complete system-on-chip built around the 32-bit ARM920T ARM processor that can operate at a maximum speed of 209 MHz (200 MIPS at 180 MHz) and has two separate 16-Kbyte each data and instruction caches. In addition to this processor, AT91RM9200 incorporates a rich set of system and application peripherals and standard interfaces in order to provide a single-chip solution for a wide range of compute-intensive applications that require maximum functionality at minimum power consumption at lowest cost. The AT91RM9200 incorporates a high-speed on-chip SRAM workspace, and a low-latency External Bus Interface (EBI) for seamless connection to whatever configuration of off-chip memories and memory-mapped peripherals is required by the application. In addition to the processor caches, the

Figure 5.1. ARM Microcontroller Architecture.

chip has 16K Bytes of SRAM and 128K Bytes of ROM embedded into it. The EBI incorporates controllers for synchronous DRAM (SDRAM), burst Flash and static memories. The AT91RM9200 integrates a wide range of standard interfaces including USB 2.0 Full Speed (12 Mbits per second) Device, USB 2.0 Host (supporting both full as well as low speed protocols), Serial ports and Ethernet 10/100 Base-T Media Access Controller (MAC), which provides connection to an extensive range of external peripheral devices and a widely used networking layer. Further, debug features such as a JTAG-ICE interface and a dedicated UART debug channel enable the development and debug of all applications, especially those with real-time constraints. The following sub-sections discuss these modules and the working of the microcontroller.

## 5.1.2 Ethernet Media Access Controller (EMAC)

The AT91RM9200 EMAC is compatible with the IEEE 802.3 standard and can operate at 10 or 100 Mbits per second data throughput capability in half-duplex or full-duplex mode. An external physical layer device (PHY) coupled between this EMAC and an external connector (RJ45) forms a 10/100 Mbps Ethernet interface for the design. This EMAC can support a Media Independent Interface (MII) as well as a Reduced Media Independent Interface (RMII). In this design, the microcontroller operates in the MII mode to meet with the PHY specifications. The EMAC manages frame transmission and reception including collision detection, preamble generation and detection, CRC control and generation, transmitted frame padding, frame encapsulation and decapsulation and error detection. The RMII (MII) supplies the 50 MHz (25 MHz) transmission and reception clocks for 100Mbits per second operation to the PHY.

## 5.1.3 Universal Serial Bus (USB) Controller

The USB controller is compliant with the USB 2.0 specifications. The USB controller consists of a USB Host Port (UHP) (number of UHP ports is package specific, there is one UHP for the 208-lead PQFP package used for this design) and a USB Device Port (UDP) [9].

#### 5.1.3.1 USB Host Port (UHP)

The USB Host Port interfaces the USB with the host application. It handles Open HCI protocol (Open Host Controller Interface) as well as USB v2.0 Full-speed (12 Mbps) and Low-speed (1.5 Mbps) protocols. The USB Host Port integrates a root hub and transceivers on downstream ports. It provides several high-speed half-duplex serial communication ports at a baud rate of 12 Mbit/s. Up to 127 USB devices (printer, camera, mouse, keyboard, disk, etc.) and the USB hub can be connected to the USB host in the USB tiered star topology [9]. Required drivers embedded into

the operating system on the microcontroller help interface external USB devices to this system.

## 5.1.3.2 USB Device Port (UDP)

The USB Device Port (UDP) is compliant with the Universal Serial Bus (USB) V2.0 full-speed (12 Mbps) device specification. It is designed to be associated with Atmels embedded USB transceiver and interfaced with the ARM9TDMI core. For this design, the signals of this port are available on an external header and can be utilized to generate a USB device interface daughter board for future applications.

Both the UHP as well as the UDP require a 48 MHz clock input, which is generated internally by the microcontroller.

## 5.1.4 Debug Unit (DBGU)

The Debug Unit provides a single entry point from the processor for access to all the debug capabilities of the microcontroller. The Debug Unit features a two-pin UART that can be used for several debug and trace purposes and offers an ideal medium for in-situ programming solutions and debug monitor communications. Moreover, the association with two peripheral data controller channels permits packet handling for these tasks with processor time reduced to a minimum.

The Debug Unit also makes the Debug Communication Channel (DCC) signals provided by the In-circuit Emulator of the ARM processor visible to the software. These signals indicate the status of the DCC read and write registers and generate an interrupt to the ARM processor, making possible the handling of the DCC under interrupt control.

Finally, the Debug Unit features a Force Reset - 'NTRST' capability that enables the software to decide whether to prevent access to the system via the In-circuit Emulator. This permits protection of the code, stored in ROM.

# 5.1.5 Universal Synchronous Asynchronous Receiver Transceiver (US-ART)

The Universal Synchronous Asynchronous Receiver Transceiver (USART) provides one full duplex universal synchronous asynchronous serial link. Data frame format is widely programmable (data length, parity, number of stop bits) to support a maximum of standards. The receiver implements parity error, framing error and overrun error detection. The receiver timeout enables handling variable-length frames and the transmitter timeguard facilitates communications with slow remote devices. Multi-drop communications are also supported through address bit handling in reception and transmission.

The USART is capable of managing several types of serial synchronous or asynchronous communications. Out of these different modes, the two main that have been implemented in this design are:

- 1. 5- to 9-bit full-duplex asynchronous serial communication:

- MSB- or LSB-first.

- 1, 1.5 or 2 stop bits.

- Parity even, odd, marked, space or none.

- By-8 or by-16 over-sampling receiver frequency.

- Optional hardware handshaking.

- Optional modem signals management.

- Optional break management.

- Optional multi-drop serial communication.

- 2. High-speed 5- to 9-bit full-duplex synchronous serial communication:

- MSB- or LSB-first.

- 1 or 2 stop bits.

- Parity even, odd, marked, space or none.

- by 8 or by-16 over-sampling frequency.

- Optional Hardware handshaking.

- Optional Modem signals management.

- Optional Break management.

- Optional Multi-Drop serial communication.

#### 5.1.6 Memory Map

The Memory Controller is responsible for decoding and mapping the on-chip address space to various embedded and external peripherals. The memory controller performs a first level of decoding, i.e., by the implementation of the Advanced System Bus (ASB) with additional features. This decodes the four highest bits of the 32-bit address bus and splits the 4G bytes of available address space into 11 separate areas.

- 1. One 256-Mbyte address space for internal memories.

- 2. Eight 256-Mbyte address spaces, each assigned to one of the eight chip select lines of the External Bus Interface (EBI), for interfacing with external chips.

- 3. One 256-Mbyte address space reserved for the embedded peripherals.

- 4. An undefined address space of 1536M bytes that returns an Abort if accessed, to assist in application debug.

Figure 5.2 shows the assignment of these memory areas.

#### 5.1.6.1 Internal Memory Mapping

Within the Internal Memory address space, the address decoder of the Memory Controller decodes eight more address bits to allocate 1-Mbyte address spaces for

| 256M Bytes     | 0x0000 0000<br>0x0FFF FFFF | Internal Memories |                            |

|----------------|----------------------------|-------------------|----------------------------|

| 256M Bytes     | 0x1000 0000<br>0x1FFF FFFF | Chip Select 0     | <u> </u>                   |

| 256M Bytes     | 0x2000 0000<br>0x2FFF FFFF | Chip Select 1     |                            |

| 256M Bytes     | 0x3000 0000<br>0x3FFF FFFF | Chip Select 2     |                            |

| 256M Bytes     | 0x4000 0000<br>0x4FFF FFFF | Chip Select 3     | EBI                        |

| 256M Bytes     | 0x5000 0000<br>0x5FFF FFFF | Chip Select 4     | EBI External Bus Interface |

| 256M Bytes     | 0x6000 0000<br>0x6FFF FFFF | Chip Select 5     |                            |

| 256M Bytes     | 0x7000 0000<br>0x7FFF FFFF | Chip Select 6     |                            |

| 256M Bytes     | 0x8000 0000<br>0x8FFF FFFF | Chip Select 7     |                            |

| 6 x 256M Bytes | 0x9000 0000                | Undefined         |                            |

| 1,536 bytes    | 0xEFFF FFFF                | (Abort)           |                            |

| 256M Bytes     | 0xF000 0000<br>0xFFFF FFFF | Peripherals       |                            |

Figure 5.2. External Memory Areas.

the embedded memories, as show in figure 5.3. The allocated memories are accessed along the 1-Mbyte address space and are repeated n times within this address space, n equaling 1M byte divided by the size of the memory. When the address of the access is undefined within the internal memory area, i.e. over the address 0x0040 0000, the Address Decoder returns an Abort to the master.

At reset, depending on the state of the Boot Mode Select (BMS) input pin for the microcontroller, Area 0 in figure 5.3 points either to the on-chip ROM (BMS = 1) or the non-volatile external memory (BMS = 0) connected to chip select zero. After the Remap command, the internal SRAM at address  $0 \times 0020 \ 0000$  is mapped into Internal Memory Area 0.

| 1M Bytes   | 0x0000 0000<br>0x000F FFFF | Internal Memory Area 0                  |            |

|------------|----------------------------|-----------------------------------------|------------|

| 1M Bytes   | 0x0010 0000<br>0x001F FFFF | Internal Memory Area 1<br>Internal ROM  |            |

| 1M Bytes   | 0x0020 0000<br>0x002F FFFF | Internal Memory Area 2 Internal SRAM    |            |

| 1M Bytes   | 0x0030 0000<br>0x003F FFFF | Internal Memory Area 2<br>USB Host Port | 256M Bytes |

| 252M Bytes | 0x0040 0000                | Undefined Area<br>(Abort)               |            |

|            | 0x0FFF FFFF                |                                         | <b> </b>   |

Figure 5.3. Internal Memory Map.

#### 5.1.6.2 External Bus Interface (EBI)

The External Bus Interface (EBI) is designed to ensure successful data transfer between several external devices and the embedded Memory Controller. The Static Memory, SDRAM and Burst Flash Controllers are all featured external Memory Controllers on the EBI. These external Memory Controllers are capable of handling several types of external memory and peripheral devices, such as SRAM, PROM, EPROM, EEPROM, Flash, SDRAM and Burst Flash. The 8 different banks with the associated chip select signals (NCS) are as follows:

- 1. Burst Flash Controller or Static Memory Controller on NCS0 (Chip Select Signal-0)

- 2. SDRAM Controller or Static Memory Controller on NCS1

- 3. Static Memory Controller on NCS3, Optional SmartMedia Support

- 4. Static Memory Controller on NCS4 NCS6, Optional CompactFlash Support

- 5. Static Memory Controller on NCS7

Following list enumerates the components that have been connected to these chipselect signals on our developed architecture:

- 1. Boot FLASH on NCS0.

- 2. SDRAMs on NCS1 (also called as SDCS).

- 3. FLASH chips for storing operating system kernel (Linux FLASH) on NCS2.

- 4. FPGA1 on NCS3.

- 5. FPGA2 on NCS4.

- 6. FLASH chips for storing FPGA configuration files (Software FLASH) on NCS5.

- 7. A Programmable Logic Device (PLD) for FPGA configuration control on NCS6.

- 8. NCS7 is unused (routed to FPGA2 as a general purpose input/output pin).

#### 5.1.6.3 Memory Allocation for Peripherals

The last block in the memory allocation in figure 5.2 is assigned to System and User Peripherals mapping. System peripherals include the Power Management Controller (responsible for generating the different clocks for the system), Memory Controller, Interrupt Controller etc. User peripherals include the USB host and device ports, Ethernet MAC etc.