# DEVELOPMENT AND VERIFICATION OF SYSTEM-ON-A-CHIP COMMUNICATION ARCHITECTURE

A Dissertation Presented

by

JIAN LIANG

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

March 15, 2004

Department of Electrical and Computer Engineering

$\odot$  Copyright by Jian Liang 2004

All Rights Reserved

# Development and Verification of System-On-a-Chip Communication Architecture

by

JIAN LIANG

| Approved as to style and content by: |  |  |  |  |  |

|--------------------------------------|--|--|--|--|--|

|                                      |  |  |  |  |  |

| Russell Tessier, Chair               |  |  |  |  |  |

|                                      |  |  |  |  |  |

| Dennis L. Goeckel, Member            |  |  |  |  |  |

|                                      |  |  |  |  |  |

| Wayne P. Burleson, Member            |  |  |  |  |  |

|                                      |  |  |  |  |  |

| Charles Weems, Member                |  |  |  |  |  |

Seshu B. Desu, Department Head Electrical and Computer Engineering

#### ACKNOWLEDGMENTS

My sincere thanks go to my adviser Professor Russell Tessier. His support and guidance played a major role in this research. It has been a wonderful experience to be a part of Reconfigurable Computing Group for the past five years. I appreciate the help of Professor Dennis L. Goeckel. Weekly meetings with him helped me develop and improve the Turbo decoding algorithm. The committee members, Professor Wayne P. Burleson and Professor Charles C. Weems, have assisted me greatly with their valuable feedbacks on this dissertation work.

It has been a great pleasure for me to work with the researchers on the 3th floor of Knowles Engineering Building. Special thanks go to Andy Laffely and Srini Krishnamoorthy for their help on my research papers. I am also thankful to my colleagues in the Reconfigurable Computing Group for their friendship and supports.

Finally, I would thank my wife for her support. While I was working on my dissertation, she has manged our lives. Her selfless devotion to our family is inspirational.

#### ABSTRACT

# DEVELOPMENT AND VERIFICATION OF SYSTEM-ON-A-CHIP COMMUNICATION ARCHITECTURE

#### March 15, 2004

#### JIAN LIANG

B.E, TSINGHUA UNIVERSITY, BEIJING, CHINA

M.S., TSINGHUA UNIVERSITY, BEIJING, CHINA

Ph.D, University of Massachusetts Amherst

Directed by: Professor Russell Tessier

Recent advances in VLSI technology have led to a dramatic increase in the computation capacities of a single chip. Current industry estimates [55] indicate mass production of silicon devices containing over 1.4 billion transistors by 2013. This proliferation of on-chip resources enables the integration of complex system-on-a-chip (SoC) designs containing a wide range of intellectual property (IP) cores. To provide high performance, SoC integration tools must consider the design of individual IP cores, their on-chip interconnections, and application mapping approaches. In this dissertation, the latter two design issues are addressed through the introduction of a new on-chip communications architecture, adaptive System-on-Chip (aSoC), and its supporting compilation software. Our communications architecture is scalable to tens of heterogeneous cores and can be customized on a per-application basis.

In aSoC, each computation core is associated with a communication interface, which is connected to each other as a two-dimensional mesh. Communication between cores takes place via pipelined, point-to-point connections. The communications are restricted to short wires between cores to allow high speed data transfer and predictable delays. The interface design can be customized based

on core data bandwidths and operating frequencies to allow for efficient use of resources. The power and clock are supplied individually in each tile for diverse working environments of heterogeneous cores.

A supporting software tool, AppMapper, was developed to map applications onto aSoC. Built upon existing compiler infrastructure and taking advantage of user interaction, AppMapper analyzes the high level language applications, schedules the on-chip communications, and configures the communication interfaces in aSoC. To augment the support for heterogeneous cores from third parties, AppMapper outputs the core codes in high level languages format such as C or Verilog, which allows the third-party compilers to handle the core specific optimization.

To evaluate the performance of aSoC, applications are mapped onto the aSoC model chips. The chosen applications include MPEG-II encoder/decoder, image smoothing filter, IIR filter, Doppler radar decoder, and orthogonal frequency division multiplexing (OFDM) modulator. In order to further test aSoC for substantial and complex applications, a Turbo decoding system is mapped onto aSoC devices. A novel adaptive Soft-output Viterbi algorithm (ASOVA) is developed for the Turbo decoder to reduce the computation complexity. By varying the number of survivor paths, ASOVA is capable of adapting its decoding complexity to speed up the decoding in the case of high signal to noise ratio (SNR).

These applications are mapped onto aSoC model devices and their performance is tested. The results are compared to other on-chip communication architectures with the same partitioning. The evaluated architectures include the hierarchical bus modeled from IBM CoreConnect on-chip communication and a dynamic routing model applying oblivious dynamic routing [30]. Based on the simulation results, aSoC outperforms the hierarchical bus model by a factor of five.

## TABLE OF CONTENTS

|     |                                 |                                                             |                                                      |                               | Pa | ge                                     |

|-----|---------------------------------|-------------------------------------------------------------|------------------------------------------------------|-------------------------------|----|----------------------------------------|

| Ac  | CKNOW                           | LEDGM                                                       | MENTS                                                |                               |    | v                                      |

| AB  | STRAC                           | CT                                                          |                                                      |                               |    | vi                                     |

| Lis | зт Оғ                           | TABLE                                                       | ES                                                   |                               |    | xii                                    |

| Lis | зт Оғ                           | Figur                                                       | RES                                                  |                               |    | xiv                                    |

| CE  | ІАРТЕ                           | R                                                           |                                                      |                               |    |                                        |

| 1.  |                                 |                                                             | ION                                                  |                               |    | 1                                      |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Motiva<br>Scalab<br>Suppo<br>Applio<br>Contri               | ation ble aSoC A orting Soft cations butions         | Architecture                  |    | 1<br>4<br>6<br>7<br>8<br>10            |

| 2.  | Back                            | KGROUN                                                      | ND                                                   |                               |    | 12                                     |

|     | 2.1                             | On-Ch                                                       | nip Comm                                             | nunication Architectures      |    | 12                                     |

|     |                                 | 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7 | Arbitrat<br>Hierarch<br>FPGA-I<br>Network<br>Compari | Coint-to-Point Connection     |    | 14<br>15<br>15<br>16<br>17<br>19<br>20 |

|     | 2.2                             | SoC S                                                       | upporting                                            | g Softwares                   |    | 24                                     |

| 3.  | ASoC                            | OVEF                                                        | RVIEW                                                |                               |    | 28                                     |

|     | 3.1                             | aSoC :                                                      | Design Pl                                            | ${ m hilosophy}$              |    | 28                                     |

|     |                                 | 3.1.1<br>3.1.2<br>3.1.3                                     | Flow Co                                              | Overview                      |    | 28<br>31<br>32                         |

|     |                                 |                                                             | 3.1.3.1<br>3.1.3.2                                   | Asynchronous Global Branching |    | 33<br>35                               |

|    | 3.2                                    | aSoC                               | Architecture                                  | 35                         |

|----|----------------------------------------|------------------------------------|-----------------------------------------------|----------------------------|

|    |                                        | 3.2.1<br>3.2.2<br>3.2.3            | Coreports: Connecting Cores to the Network    | 37<br>38<br>41             |

| 4. | Appl                                   | MAPPE                              | R COMPILER AND SIMULATOR                      | 44                         |

|    | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Basic<br>Inter-c<br>Comm<br>Core C | Block Partitioning and Assignment             | 45<br>47<br>49<br>49<br>52 |

| 5. | Ехрь                                   | ERIMEN                             | TAL METHODOLOGY                               | 55                         |

|    | $5.1 \\ 5.2$                           | _                                  |                                               | 55<br>55                   |

| 6. | TARG                                   | GET AS                             | oc Applications6                              | 60                         |

|    | 6.1<br>6.2<br>6.3<br>6.4<br>6.5        | Ortho<br>Doppl<br>Image            | gonal Frequency Division Multiplexing         | 60<br>61<br>62<br>63<br>63 |

| 7. | Adai                                   | PTIVE S                            | SOVA TURBO CODE DECODER APPLICATION ON ASOC 6 | 64                         |

|    | $7.1 \\ 7.2$                           |                                    |                                               | 65<br>67                   |

|    |                                        | 7.2.1                              | Turbo Codes                                   | 67                         |

|    |                                        |                                    |                                               | 69<br>71                   |

|    |                                        | 7.2.2                              | Turbo Code Decoding Algorithms                | 71                         |

|    |                                        |                                    | 0                                             | 72<br>75                   |

|    |                                        | $7.2.3 \\ 7.2.4$                   | *                                             | 77<br>78                   |

|    | 7.3                                    | Adapt                              | sive SOVA Decoding 8                          | 80                         |

|    |                                        | 7.3.1 $7.3.2$                      | O                                             | 82<br>83                   |

|    | 7.4                                    | Simula                             | ation Results                                 | 84                         |

| 8. | HARE       | WARE                    | Implementation of ASOVA 8                                                                 | 89              |

|----|------------|-------------------------|-------------------------------------------------------------------------------------------|-----------------|

|    | 8.1<br>8.2 |                         | ecture of Turbo Decoder                                                                   | 89<br>90        |

|    |            | 8.2.1                   | Traceback Approach                                                                        | 91              |

|    |            |                         |                                                                                           | 91<br>92        |

|    |            | 8.2.2                   | Register Exchange Approach                                                                | 95              |

|    |            |                         | 8.2.2.1 Behavior of Register Exchange                                                     |                 |

|    | 8.3        | Experi                  | mental Approach of FPGA Implementation                                                    | 01              |

|    |            | 8.3.1<br>8.3.2          | FPGA Implementation Parameters                                                            |                 |

| 9. | Мар        | ASOV                    | A Turbo Decoder onto aSoC                                                                 | 05              |

|    | 9.1        | Result                  | s of FPGA Implementation                                                                  | 05              |

|    |            | 9.1.1<br>9.1.2          | Register Exchange FPGA Turbo Decoder                                                      |                 |

|    |            |                         | 9.1.2.1 Traceback ASOVA Turbo Decoder Statistics 19 9.1.2.2 ASOVA Dynamic Reconfiguration | 08<br>11<br>12  |

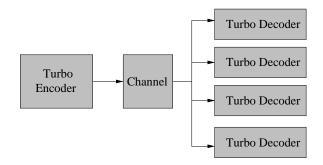

|    | 9.2        | Mappi                   | ng ASOVA onto aSoC                                                                        | 14              |

|    |            | 9.2.1<br>9.2.2<br>9.2.3 | Partitioning of Functional Blocks                                                         | 17              |

| 10 | .aSoC      | SIMUL                   | ATION RESULTS                                                                             | 22              |

|    |            |                         | Parameter Evaluation and Layout                                                           |                 |

|    |            | 10.2.2<br>10.2.3        | Comparison to CoreConnect Architecture                                                    | $\frac{26}{27}$ |

|    |            |                         | me Communication Branching                                                                |                 |

| 11.Conclusion | ON AND | FUTURE | Work. | <br> | <br> | <br> | 135   |

|---------------|--------|--------|-------|------|------|------|-------|

| References    |        |        |       | <br> | <br> | <br> | . 139 |

## LIST OF TABLES

| Table | P                                                                       | age |

|-------|-------------------------------------------------------------------------|-----|

| 2.1   | Summary of On-Chip Architectures                                        | 13  |

| 3.1   | Communication schedules for tiles in Figure 3.2                         | 31  |

| 3.2   | Data-dependent communication control branching for Tile D in Figure 3.3 | 34  |

| 5.1   | aSoC device configurations                                              | 55  |

| 5.2   | Component Parameters                                                    | 58  |

| 7.1   | Expectation of LLR                                                      | 84  |

| 7.2   | Parameter Default Values                                                | 85  |

| 7.3   | (31,27) Code at BER= $10^{-4}$                                          | 87  |

| 9.1   | Register Exchange Turbo Decoder Statistics                              | 106 |

| 9.2   | ASOVA Decoder Statistics for BER= $10^{-4}$ and T=-10                   | 108 |

| 9.3   | ASOVA Performance on a Stratix EP1S10 FPGA                              | 109 |

| 9.4   | Dynamic Reconfiguration                                                 | 112 |

| 9.5   | Decoding Speed of FPGA ASOVA Decoder versus Microprocessors             | 113 |

| 9.6   | Parameters of Stratix and DSPs                                          | 113 |

| 9.7   | Comparison to DSPs                                                      | 114 |

| 9.8   | Comparison Results of (15,13) Code                                      | 114 |

| 9.9   | Resources Usage of Turbo Decoder on aSoC                                | 117 |

| 9.10  | Decoding Speed of aSoC and FPGA Implementation on (31,27) Code          | 119 |

| 9.11  | 1 Transistor Count Comparison of Different Approaches                   | 120 |

| 9.12  | 2 Transistor Count of aSoC Cores                                        | 120 |

| 10.1  | Benchmark statistics used to determine aSoC parameters            | 23 |

|-------|-------------------------------------------------------------------|----|

| 10.2  | Comparison of aSoC and CoreConnect Performance                    | 26 |

| 10.3  | Comparison of a<br>SoC and Hierarchical CoreConnect Performance 1 | 27 |

| 10.4  | Comparison of aSoC and Dynamic Network Performance 1              | 28 |

| 10.5  | Comparison to published work                                      | 29 |

| 10.6  | Control branching transfer example                                | 30 |

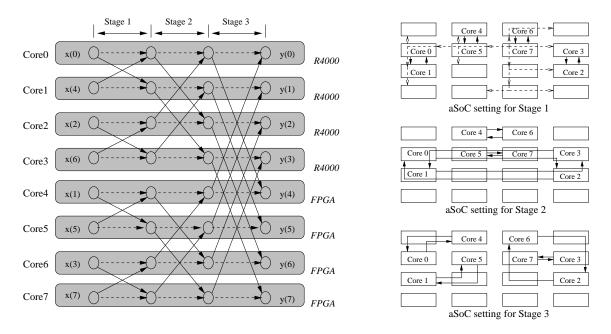

| 10.7  | FFT application run time for N points (times in uS)               | 31 |

| 10.8  | Scalability of the MPEG2 Encoder                                  | 32 |

| 10.9  | Scalability of Turbo Decoder                                      | 33 |

| 10.10 | OScalability of image smoothing for 800x600 pixel image           | 33 |

| 10.11 | Doppler run time for N points (times in uS)                       | 34 |

## LIST OF FIGURES

| Figure |                                                                                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Adaptive System-on-a-Chip (aSoC)                                                                                                                                     | . 4  |

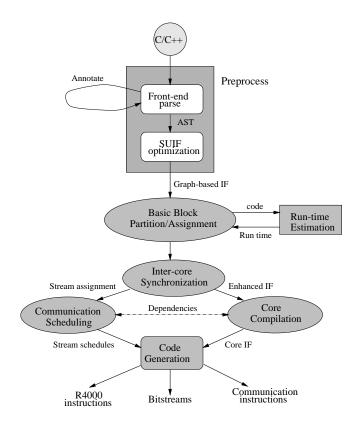

| 1.2    | Flowchart of AppMapper                                                                                                                                               | . 7  |

| 2.1    | Design Space of SoC                                                                                                                                                  | . 14 |

| 2.2    | Illustration of Relative Tradeoff between Architectures                                                                                                              | . 19 |

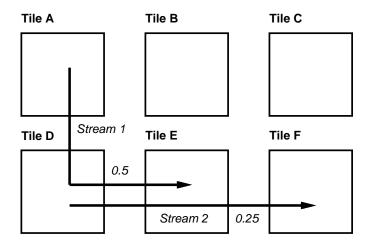

| 3.1    | Multi-core data streams 1 and 2. This example shows data streams from Tile A to Tile E and from Tile D to Tile F. Fractional bandwidth usage is indicated in italics | . 29 |

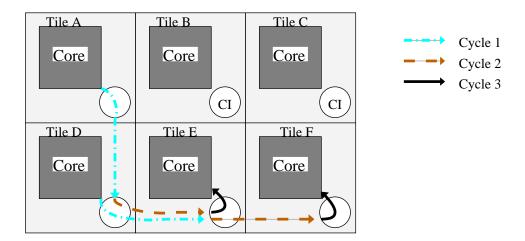

| 3.2    | Pipelined stream communication across multiple communication interfaces                                                                                              | . 30 |

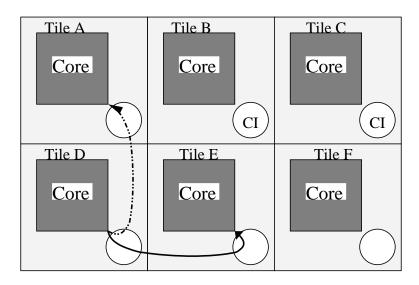

| 3.3    | Example of distinct stream paths for two communication schedules which send data from a source to different destinations                                             | . 34 |

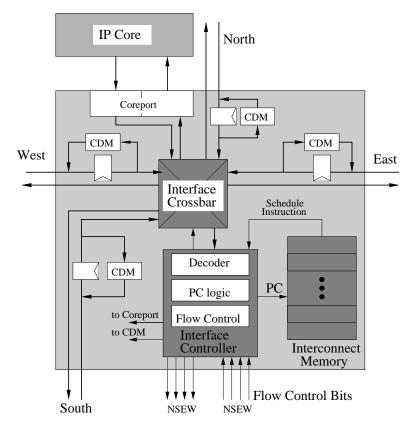

| 3.4    | Core and Communication Interface                                                                                                                                     | . 36 |

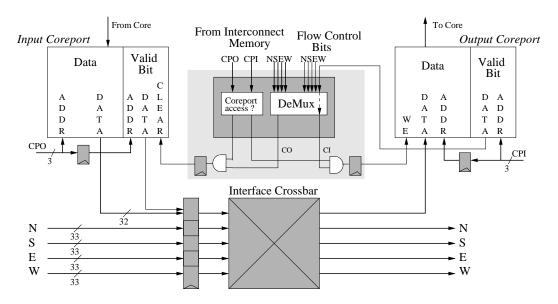

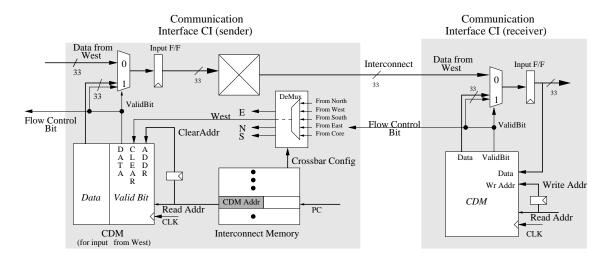

| 3.5    | Detailed communication interface                                                                                                                                     | . 37 |

| 3.6    | Input and output coreport interface                                                                                                                                  | . 38 |

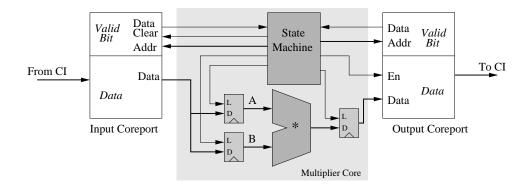

| 3.7    | Multiplier coreport interface                                                                                                                                        | . 40 |

| 3.8    | Flow Control Scheme                                                                                                                                                  | . 41 |

| 4.1    | aSoC Application Mapping Flow                                                                                                                                        | . 46 |

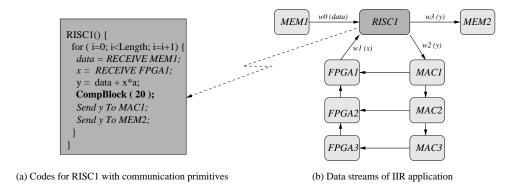

| 4.2    | Inter-core synchronization                                                                                                                                           | . 48 |

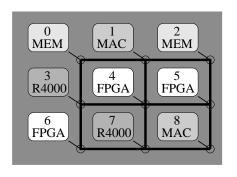

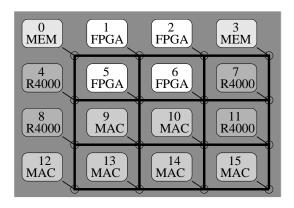

| 5.1    | aSoC topologies: 9 and 16 cores                                                                                                                                      | . 56 |

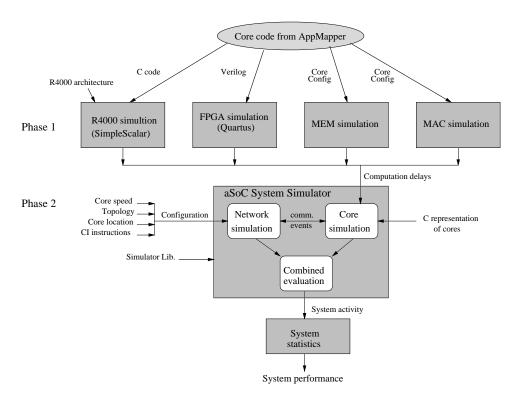

| 5.2    | aSoC System Simulator                                                                                                                                                | . 57 |

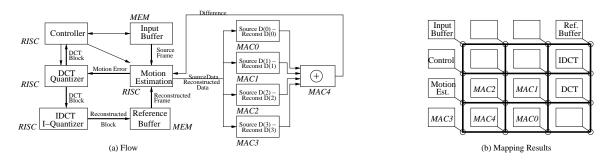

| 6.1    | Partitioning of MPEG-2 encoder to a $4\times4$ aSOC configuration                                                                                                    | . 61 |

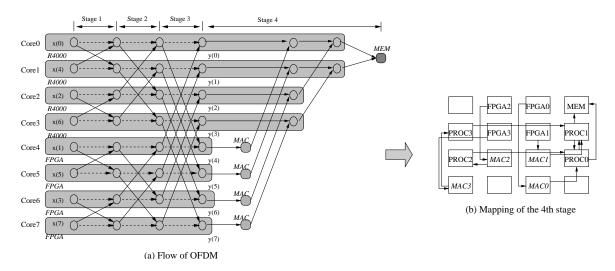

| 6.2    | OFDM mapped to 16 core aSOC model                                                                                                                                    | . 61 |

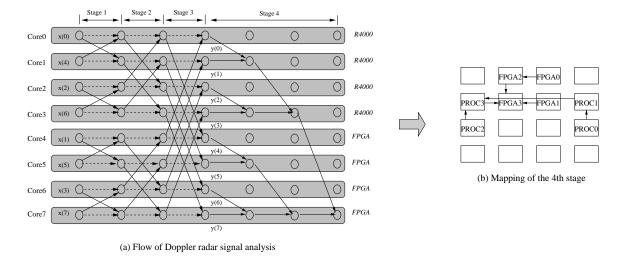

| 6.3  | Doppler radar signal analysis mapped to 16 core aSOC model               | 62  |

|------|--------------------------------------------------------------------------|-----|

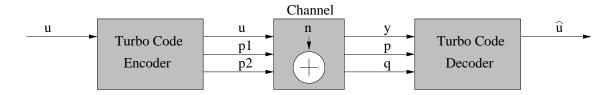

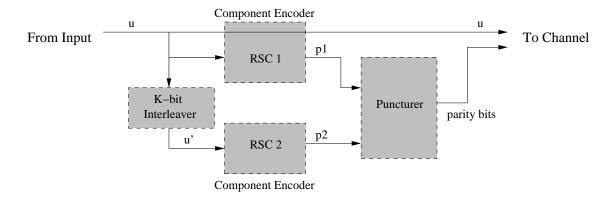

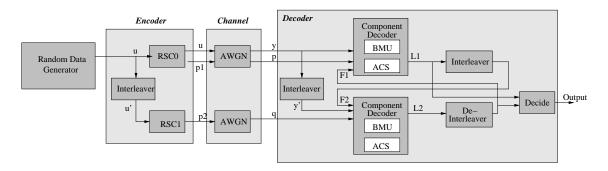

| 7.1  | Turbo Code System                                                        | 67  |

| 7.2  | Turbo Code Encoder                                                       | 69  |

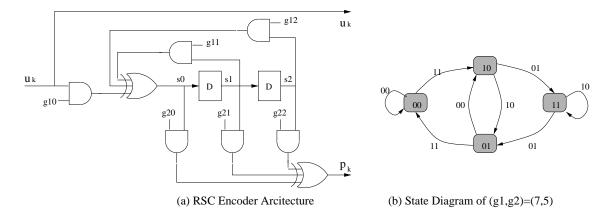

| 7.3  | RSC Architecture and State Diagram                                       | 70  |

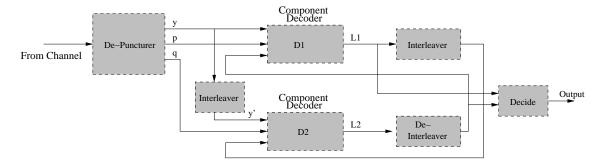

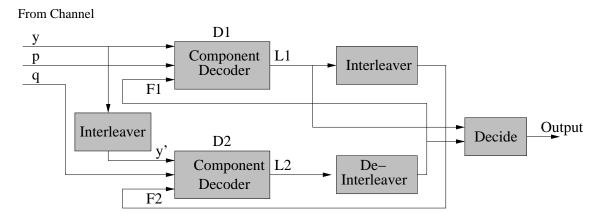

| 7.4  | Iterative Decoder                                                        | 72  |

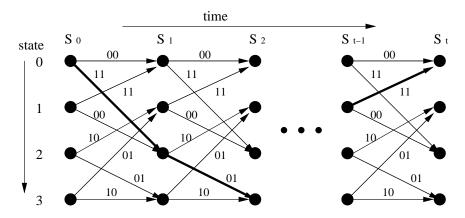

| 7.5  | Trellis Diagram                                                          | 72  |

| 7.6  | Hard-decision Viterbi Algorithm                                          | 73  |

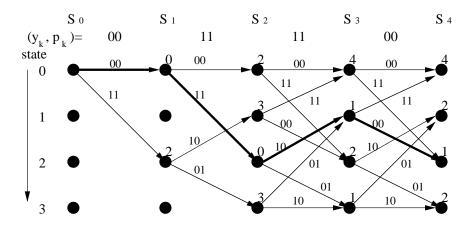

| 7.7  | Trellis Diagram of SOVA                                                  | 76  |

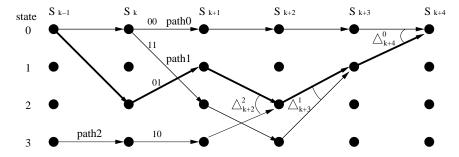

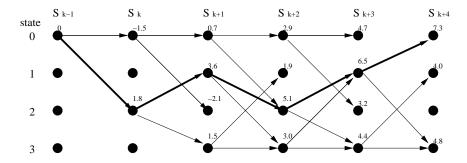

| 7.8  | Trellis Diagram of Adaptive SOVA $(T = 1.0, N_{max} = 3)$                | 80  |

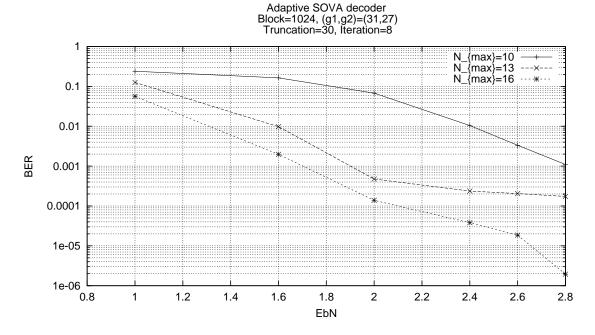

| 7.9  | Performance with Varying $N_{max}$                                       | 82  |

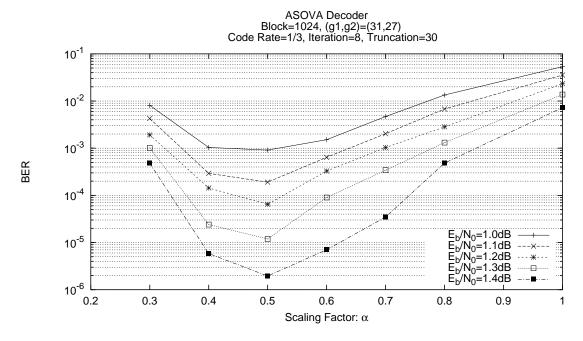

| 7.10 | Performance with Varying $\alpha$                                        | 86  |

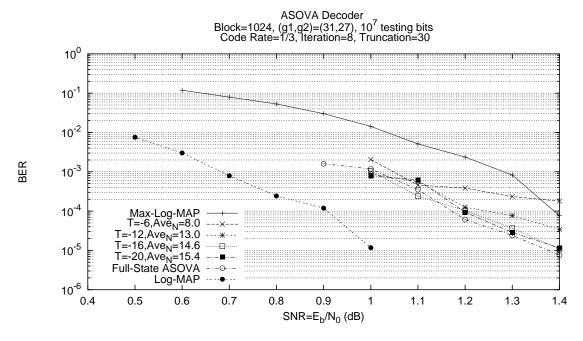

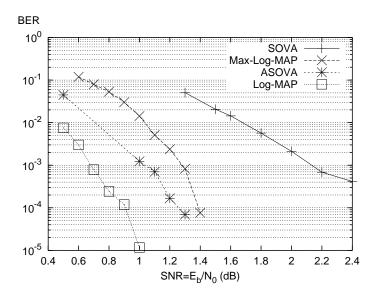

| 7.11 | Performance of ASOVA                                                     | 87  |

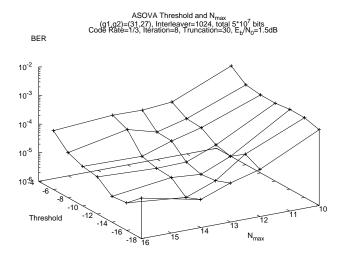

| 7.12 | Affects of Threshold and $N_{max}$                                       | 88  |

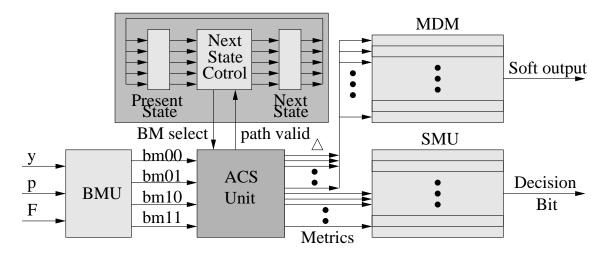

| 8.1  | Block Diagram of Turbo Decoder                                           | 89  |

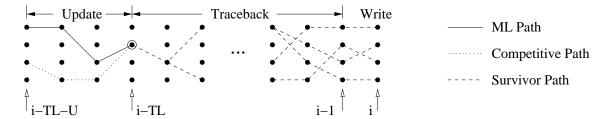

| 8.2  | Traceback SOVA                                                           | 91  |

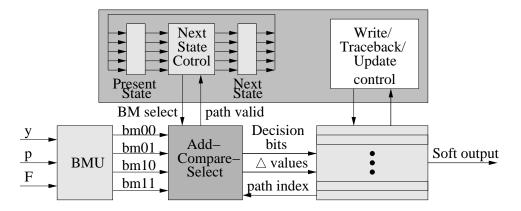

| 8.3  | Architecture of Traceback Component Decoder                              | 92  |

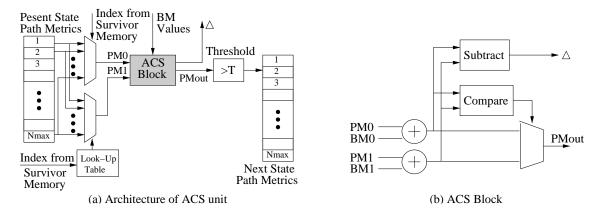

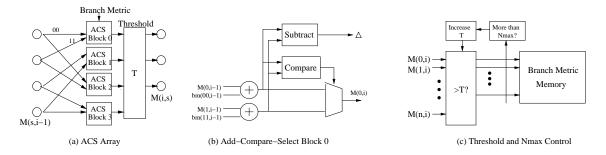

| 8.4  | Add-Compare-Select Components                                            | 93  |

| 8.5  | Block Diagram of Register Exchange ASOVA Component Decoder $\ .$ .       | 97  |

| 8.6  | Architecture of Add-Compare-Select Unit                                  | 98  |

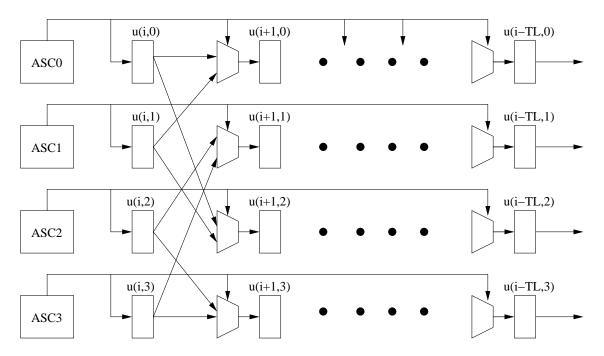

| 8.7  | Architecture of Survivor-Memory-Unit                                     | 99  |

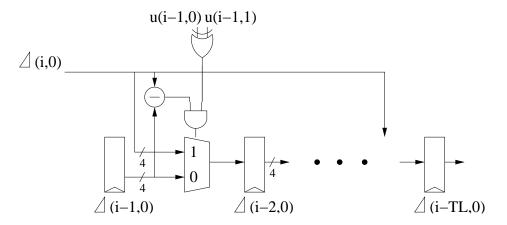

| 8.8  | Metric Difference Memory Architecture                                    | 100 |

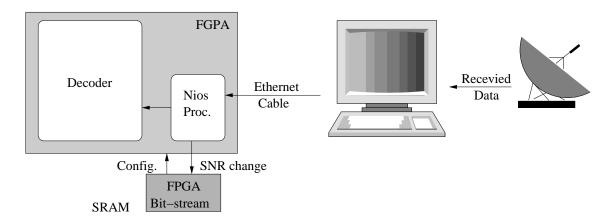

| 8.9  | Turbo Code Experiment System                                             | 104 |

| 9.1  | ASOVA Performance for a (31,27) code versus competing decoder algorithms | 106 |

| 9.2  | SNR Distribution of Log-Normal Shadowing Channel                         | 110 |

| 9.3  | ASoC Partitioning of Turbo Decoder              | 115 |

|------|-------------------------------------------------|-----|

| 9.4  | System with Four Turbo Decoders                 | 116 |

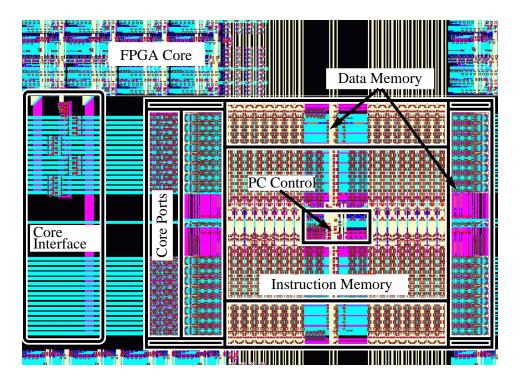

| 10.1 | Layout of FPGA Core and Communication Interface | 124 |

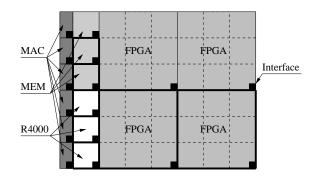

| 10.2 | Non-uniform aSoC core configuration             | 124 |

| 10.3 | Mapping Result of FFT                           | 130 |

#### CHAPTER 1

#### Introduction

The increase of gate count per chip makes the IP core based System-on-a-Chip (SoC) a feasible solution for chip design. Currently used bus-based on-chip communication architecture has become the limiting factor of SoCs for its un-scalable nature. A novel on-chip communication platform, the Adaptive System-on-a-Chip (aSoC), is developed to fulfill this requirement. ASoC applies a core-based mesh architecture using a pipelined, packet-switching communication network for heterogeneous cores. A compiler tool is developed to statically schedule the on-chip communications in aSoC.

#### 1.1 Motivation

The dramatic increase in the transistor capacity of a single chip has led to the design concepts of System-on-a-Chip (SoC). Current industry estimates [55] indicate that mass production of silicon devices containing over 1.4 billion transistors would be possible by 2013. To reduce the exponential increase in the design complexity of such a huge hardware resource, SoC makes use of a core-based structure, in which the cores can be embedded processors, large soft elements and algorithmic subsystems. These block elements are the reusable Intellectual Property (IP) cores obtained from company libraries, prior internal designs or licensed from third parties. With well-designed IP cores, SoC designers can focus on the system level optimizations.

In such a core-based SoC architecture with numerous of IP cores, the on-chip communication is the focus of the whole system. One of the critical points to be considered by the core designers is the communication bandwidth with other cores or memory. With a highly parallelized and pipelined architecture, current processor cores are able to issue multiple instructions per cycle. Most instructions require two or three operands. The communication bandwidth requirements of such cores is generally compatible with the core kernel speed. When modern VLSI techniques allow SoC to integrate increasing number of IP cores, on-chip communication will become the bottleneck for SoC. Other recent studies [63] indicate that on-chip communication has already become the limiting factor in SoC performance.

Most current SoC designs apply a bus-based communication architecture [39, 78, 52, 4, 3]. In the near future, when the number of on-chip cores scales, these architectures will soon fail to provide the demanded communication ability on account of the following factors: dynamic allocation of communication resources, limited data bandwidth and the clock skew and capacitance along the lone bus lines.

- Significant amounts of dynamic arbitration for shared communication resources across even a small number of components can quickly form a performance bottleneck, especially for data-intensive, stream-based computation. The centralization of the arbitrary controller also restricts the number and physical location of the cores.

- At any given time, a bus can be occupied by a single bus master. Other bus

masters have to wait until the end of the current transaction before they can

compete for the bus control, which means low communication efficiency and,

therefore, limited bandwidth.

- To operate reliably, the *clock* skew should be under 10%, i.e. less than 5ns in current techniques [105]. When the chip is large and the bus line is long, the clock speed for the bus has to be slowed down to make sure that the skew is within the reliable range. Even though repeaters can be used to reduce the

signal skew, it is still a serious problem when the bus lines have to travel across several cores.

• An additional, the *capacitance* of the interfaces, will also limit the number of cores that a bus can drive.

The design process of SoC is made more complex by the need of heterogeneous cores of differing applications. The heterogeneous nature of cores in terms of clock speed, resources, and processing capability makes cost modeling difficult. Additionally, communication modeling for interconnection with long wires and variable arbitration protocols limits performance predictability required by computation and communication scheduling. To fulfill different cores' requirements, modern on-chip buses support more than one communication scheme, such as DMA, burst transfers, split transactions, priority arbitration, and so on [54, 39]. Besides the data bus, each core has to provide a set of control signals to the central bus controller, which significantly degrades the communication performance.

Realizing the problems of bus-based architecture, numerous approaches has been proposed lately for on-chip communication with differing topologies, such as 1D array [34], 2D meshes [74, 103, 24], hierarchical network [66], hexagon mesh [70], and so on. These architectures can be categorized by their scheduling schemes into two classes: the static network which is scheduled at compile-time, and the dynamic network-on-chip (NoC) architectures. The former [74, 70, 24, 104], which is named the FPGA-like architecture, relies on the compilers to schedule the communication which simplifies the hardware resources, but loses the flexibility to change the communication pattern in run time, which is required by many applications with data dependent communications. As a result, the SoCs with FPGA-like architectures usually target specific function or applications with fixed communication patterns like multi-media and DSP. The latter [12, 50, 31] presents the idea of using dynamic

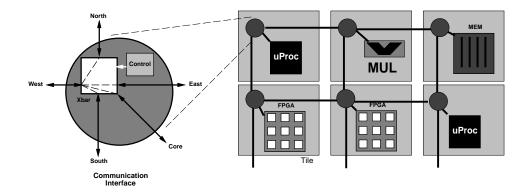

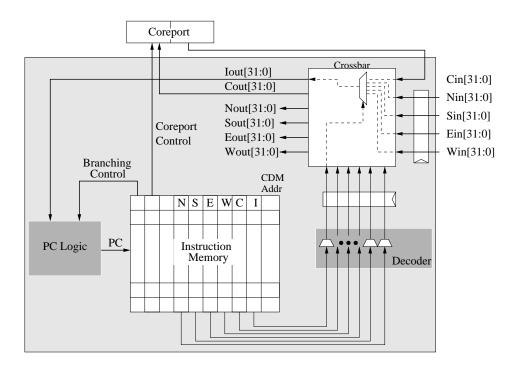

Figure 1.1. Adaptive System-on-a-Chip (aSoC)

networks for on-chip communication. These approaches provide full flexibility for communication, but the arbitration and scheduling totally rely on the network which results in high hardware costs. To better solve the dynamic routing problems, such as deadlock, congestion and buffering, more complicated circuitry will be required.

To better address the problems of prohibitive cross-chip communication on account of increasing die sizes, future SoCs will require a communication platform that can support a variety of diverse IP cores. This platform must also be scalable in terms of hardware resource cost, physical characteristics, application mapping, and software support.

#### 1.2 Scalable aSoC Architecture

Our modular communications architecture, adaptive system-on-a-chip (aSoC), provides a platform for next generation on-chip systems. The goal of aSoC is to build a scalable on-chip communication platform to solve the problems faced by the current bus-based architectures. By employing a pipelined packet-switching network, aSoC is able to achieve scalable data bandwidth. Furthermore, the static scheduling scheme makes aSoC a low-cost architecture for on-chip designs.

As shown in Figure 1.1, an aSoC device contains a two-dimensional mesh of computational *tiles*. Each tile consists of a core and an associated communication

interface. The interface design can be customized based on core data bandwidths and operating frequencies to allow for efficient use of resources. The power and clock are supplied individually to each tile for diverse working environments of heterogeneous cores.

The neighboring tiles are connected using a pipelined, packet-switching network.

To address the previously mentioned limiting factors of bus-based communication architecture, aSoC is designed with the following techniques:

- Arbitration: Static scheduling is employed in aSoC to eliminate the dynamic arbitration of bus-based architecture. While statically-scheduled data transfer is optimized in compile time, the software-based mechanism for data routing has been developed to reduce the congestion overhead. While most of the communications can be obtained by statically analyzing the codes, some data dependent communications can be handled by dynamic communication pattern switching of aSoC.

- Bandwidth: While the bandwidth of bus architecture is limited by the exclusive occupation of the bus master, the communication between aSoC nodes takes place via pipelined, point-to-point connections. Multiple data pieces are transferred simultaneously on the network on different pipelined stages. The number of stages is the number of tiles through which the data travels. As a result, the bandwidth is scalable with the size of the system. The wire length between cores is carefully chosen to balance the network speed, communication latency and core size.

- Clock: By limiting inter-core communication to short wires with predictable performance, high-speed communication can be achieved. Furthermore, the regularity of mesh architecture allows the network to work synchronously, which guarantees the simplicity and high speed of the communication network.

• Capacitance: ASoC has a pipelined architecture. At each stage, a communication interface drives a single core. As a result, the capacitance will not accumulate when system scales.

Compared to other scalable networks, aSoC is a low cost, heterogeneous flexible platform that fills the gap between the Network-on-Chip (NoC) and FPGA-like architectures. The aSoC platform provides a communication substrate for computation dense applications in the domains of DSP, multi-media and wireless communications. Most of these applications have highly predictable on-chip communication patterns, which enable a static scheduling network in aSoC. To reduce the hardware cost and improve the simplicity, aSoC reuses the wires using packet-switching based on static scheduling. Furthermore, aSoC combines the static network with certain dynamic scheme, which enables aSoC to adapt the network dynamically to the communication pattern changes and improves the flexibilities of aSoC. The static scheduling scheme with limited dynamic function makes aSoC simpler than the NoC approach.

#### 1.3 Supporting Software

In aSoC, the static communication scheduling is applied to optimize its inter-core communication. While this job can be done manually for two or three cores, an automated software tool is required for larger aSoC chips. An application mapping tool, AppMapper, has been developed to translate high-level language application representations to aSoC devices.

The compilation is made more complicated by the heterogeneous cores. To maintain the flexibility of core selection, AppMapper leaves the core-related optimization for the third-part core compilers. AppMapper outputs the instructions for IP cores in the format of high level languages like C, Verilog or other control codes. They can be easily translated into core specific machine codes using the compilers provided

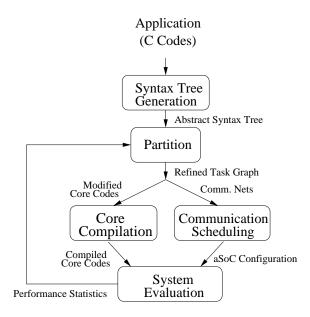

Figure 1.2. Flowchart of AppMapper

by the core vendors. As a result, users are able choose the cores appropriate for their applications without modifying the kernel of AppMapper.

As shown in Figure 1.2, compiler steps, including syntax tree generation, code partitioning, communication scheduling, system evaluation and core-dependent compilation are part of the AppMapper flow. Although each step has been fully automated, design interfaces for manual intervention are provided to improve mapping efficiency. Based on the performance statistics from system evaluation, manual interventions are allowed for better aSoC partition. Novel algorithms based on advanced cost functions have been developed for both partitioning and scheduling based on heuristic techniques.

A system-level simulator allows for performance evaluation prior to design implementation.

#### 1.4 Applications

Key components of the aSoC architecture, including the communication interface architecture, have been simulated and implemented in 0.18 micron technology.

Experimentation results show that a communication network speed of 400MHz with a 6% communication area overhead to on-chip IP cores.

A set of applications have been developed and tested for the aSoC devices. The applications are chosen carefully from multi-media, DSP and communication domains, including MPEG-2 encoder/decoder, IIR filter and an image processing kernel, Doppler radar and OFDM modulator. These applications have been mapped to 9 and 16 core aSoC devices via the AppMapper tool.

While the above applications are relative small and regarded as DSP cores rather than applications, a Turbo decoding system has been mapped onto the aSoC platform. This turbo code simulation system includes a turbo encoder, a channel simulator, and a turbo decoder. The turbo decoder employs a novel adaptive soft-output Viterbi algorithm (ASOVA) which reduces the complexity of the Soft-Output Viterbi Algorithm [48] with a competitive error correction ability. In addition, ASOVA can adapt its decoding complexity according to the input signal to noise ratio (SNR). This Turbo decoder is mapped onto an Altera Stratix FPGA on the Nios development board [6] to verify its functionality. After obtaining the required parameters from the FPGA testing, the Turbo decoder is simulated on aSoC devices. The advantages of the high data bandwidth of aSoC are depicted in the comparison to other implementations of the same Turbo code simulation system on FPGA and bus-based architectures.

Performance comparison between aSoC implementations and other more traditional on-chip communication platforms, such as an on-chip bus, show an aSoC performance improvement by up to a factor of five. Simulation results also reveal that aSoC have better scalability for systems with more cores over bus architecture.

#### 1.5 Contributions

The contribution of this dissertation includes four major parts.

- Construct the architecture of aSoC. A novel statically scheduling packet-switching on-chip network, aSoC, is designed for SoCs. ASOC applies a pipelined architecture which solves the problem of the inter-core communication bottleneck of next generation SoCs.

- Develop an automated compiling software and simulator, AppMapper, for aSoC. AppMapper is able to map high level language applications into aSoC silicon. The simulator traces the network cycle by cycle and provides the system performance information. Furthermore, it can also simulate other communication architectures, such as bus, hierarchical bus, dynamic networks, etc. with minor setting changes.

- Validate the aSoC architecture using software simulation. Based on the layout parameters, aSoC test chips with 9 cores and 16 cores are created. DSP applications are mapped onto these aSoC test chips. For the purpose of comparison, models are also established using the same topology with other communication architectures, namely, bus, hierarchical bus, and dynamic network. Experimental results show that the implementation using aSoC architecture runs up to five times faster than bus architecture, and outperforms other models.

- Develop a novel Turbo code decoding algorithm, ASOVA, which simplifies the complexity of SOVA [48] while maintaining the error correction ability. This Turbo code system is mapped onto aSoC to demonstrate the aSoC performance with larger applications.

Publications related to this dissertation include:

Jian Liang, Andrew Laffely, Sriram Srinivasan, and Russell Tessier, An Architecture and Compiler for Scalable On-Chip Communication, Transaction of VLSI (accepted).

- Jian Liang, Russell Tessier, and Dennis L. Goeckel, A Dynamically-Reconfigurable, Power-Efficient Turbo Decoder, in FCCM'04 (Field-Programmable Custom Computing Machines) (submitted)

- 3. Jian Liang, Russell Tessier, Oskar Mencer, Floating Point Unit Generation and Evaluation for FPGAs, in FCCM'03 (Field-Programmable Custom Computing Machines), Napa, CA. Apr. 2003.

- 4. Jian Liang, Sriram Swaminathan, Russell Tessier, aSoC: A Scalable, Single-Chip Communications Architecture, in *Proceedings of the IEEE International Conference on Parallel Architectures and Compilation Techniques*, Philadelphia, PA. October 2000.

- 5. Andrew Laffely, Jian Liang, Wayne Burleson and Russell Tessier, Adaptive System on a Chip (aSoC): a Backbone for Power-Aware Signal Processing Cores, in *Proceedings of IEEE International Conference on Image Processing*, Barcelona, Spain, Sep. 2003.

- 6. Andrew Laffely, Jian Liang, Prashant Jain, Ning Weng, Wayne Burleson and Russell Tessier, Adaptive Systems on a Chip (aSoC) for Low-Power Signal Processing, in *Proceedings of the Asilomar Conference on Signals, Systems,* and Computers, Monterey, California, November 2001.

- Andrew Laffely, Jian Liang, Russell Tessier, C. Andras Moritz and Wayne Burleson, Power-Aware System on a Chip, in the Boston Area Architecture Workshop, Boston, MA, Jan. 2003

#### 1.6 Overview

This dissertation presents a review of SoC-related communication architectures and the state-of-the-art SoC compiling tools in Chapter 2. Chapter 3 reveals the

details of our communication architecture and explains its suitability for on-chip interconnection. Chapter 4 demonstrates the application mapping methodology and describes component algorithms. Simulation environment and experimental approach are described in Chapter 5, and Chapter 6 introduces the DSP applications that are mapped onto aSoC devices. To further test aSoC, a Turbo decoding system has been developed for aSoC. Chapter 7 reveals the adaptive Soft-output Viterbi algorithm (ASOVA), which is developed to reduce the decoding complexity. Chapter 8 explains the architecture to implement ASOVA in hardware. Chapter 9 verifies the FPGA implementation of the ASOVA Turbo decoder and maps it onto aSoC devices. The required parameters for aSoC implementation and performance results obtained from the FPGA implementation are presented. In Chapter 10, the experimental results for aSoC devices are presented. These results are compared against the performance of alternate interconnect approaches. Finally, Chapter 11 concludes this dissertation and proposes the potential research directions.

#### CHAPTER 2

#### BACKGROUND

Various communication architectures are used on System-on-a-Chip (SoC) and embedded system designs. This chapter briefly reviews these on-chip communication architectures. An attempt is made to group the existing communication platforms by their structures. The advantages and pitfalls of each group are analyzed, and figures are shown to better illustrate the trade-offs between architecture groups and the position of aSoC in the design space. Furthermore, the supporting softwares for SoCs are also reviewed, and the difference from the software tool for aSoC, AppMapper, is pointed out.

#### 2.1 On-Chip Communication Architectures

Examination of current on-chip protocols provides insight into the requirements of on-chip interconnect and its differences from traditional multiprocessor networks. Notable, common threads through these on-chip interconnect architectures include the *simplicity* of the required circuitry, the *flexibility* support for numerous interconnection topologies and the *connectivity* provided for each core. Simplicity is the resource cost to for the hardware, and the connectivity here means the average data bandwidth that the communication architecture can provide for each local core. The flexibility is defined as how easy a system can change its communication pattern to establish a new connection. For example, buses provide high flexibility for the connected cores, while fixed point-to-point connections have a limited flexibility since a new chip has to be designed to allowed for another connection.

| Project     | Cite  | First Pub. | Arch.          | Flex.  | Conn.  | Cores  |

|-------------|-------|------------|----------------|--------|--------|--------|

| Coral       | [13]  | 2000       | Fixed/Bus      | Low    | Low    | Heter. |

| Daytona     | [2]   | 2000       | Bus            | High   | Low    | Heter. |

| IDT         | [52]  | 2000       | Bus            | High   | Low    | Heter. |

| AMBA        | [39]  | 1997       | Hier. Bus      | High   | Median | Heter. |

| CoreConnect | [54]  | 2000       | Hier. Bus      | High   | Median | Heter. |

| PI Bus      | [78]  | 1997       | Hier. Bus      | High   | Low    | Heter. |

| MATRIX      | [74]  | 1996       | 2D Mesh        | Median | Median | Homo.  |

| CHESS       | [70]  | 1999       | Hex Array      | Median | Median | Homo.  |

| DP-FPGA     | [24]  | 1994       | FPGA-like      | Median | Median | Homo.  |

| Pleiades    | [66]  | 1997       | Hier. Crossbar | Median | Median | Heter. |

| RAW         | [103] | 1997       | 2D Mesh        | High   | High   | Homo.  |

| Dally       | [31]  | 2000       | 2D Mesh        | High   | High   | Homo.  |

| aSoC        | [67]  | 2000       | network        | Media  | High   | Heter. |

Table 2.1. Summary of On-Chip Architectures

Since the cost of hardware resources heavily depends on the system size and architecture choices, the simplicity will be addressed later in this section while the trade-off between the connectivity and flexibility for the different communication architecture designed will be first discussed.

Since Numerous on-chip interconnect approaches have been proposed as a means to connect intellectual property (IP) cores, for better understanding this trade-off, these approaches can be classified based on the architecture to five groups: fixed point-to-point connection, arbitrated buses, hierarchical buses connected via bridges, FPGA-liked static switching networks and Network-on-Chip (NoC). A few examples and their classifications are listed in Table 2.1.

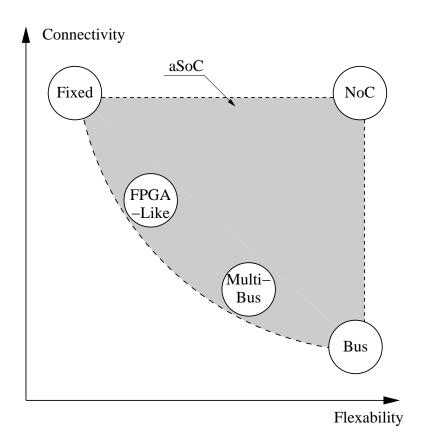

An overview of these architects on the design space of connectivity and flexibility is shown in Figure 2.1. The circles represent the approximate location of each group in the design space, however, due to the various trade-offs, designs in the same group might be scattering around and not restricted by the circle. The achievable trade-offs are given by the shaded area.

Figure 2.1. Design Space of SoC

#### 2.1.1 Fixed Point-to-Point Connection

Using the fixed point-to-point connection architectures [32, 13], signals between cores are transferred by dedicated wires. These architectures are most used in small ASIC designs. All connections are decided at design time and can not be changed later.

Fixed connections have lowest flexibility and are located in the left-top corner in Figure 2.1. The connectivity of fixed connections is high, but it comes with un-affordable design cost. In addition, the required number of wires for such a system will increase exponentially when the number of cores goes up. It is unfeasible to route such a huge amount of wires except in a very regular mesh.

#### 2.1.2 Arbitrated Bus

The bus architecture connects multiple cores using long bus lines. The bus lines are time-shared under the control of the bus arbitrator. The bus-based approaches include [52, 81, 94, 2]. In general, all of these architectures have similar arbitration characteristics to master/slave off-chip buses with several new features including data pipelining [52], replacement of tri-state drivers with multiplexers [81], and separated address/data buses due to the elimination of off-chip pin constraints.

These approaches are put in the right-bottom corner of Figure 2.1. While flexible, they have poor connectivity due to the centralized arbitration and the fixed bandwidth that has to be shared by all cores in a system.

#### 2.1.3 Hierarchical Bus

Since an arbitrated bus is unable to fulfill the bandwidth requirement of multiple cores, hierarchical bus architectures are employed in many designs to increase connectivity. Hierarchical Bus combines several buses together using hierarchical nodes or bus bridges. Cores on the same bus can communicate without interfering with the cores on another bus, but communication across buses requires additional delay. Several current on-chip interconnects support the connection of hierarchical buses via bridges [4, 39], multiplexed memory/processor interconnect solutions [3], or variable topologies (e.g. partial crossbar, tree) [54].

AMBA [39] is a hierarchical bus model that consists high speed Processor Local Buses (PLB) and low speed On-chip Peripheral Buses (OPB). The PLB can be dedicated to the high-speed data transfers such as CPU and caches without interfering with slow peripheral IO units. A PLB can be connected to an OPB via a PLB-OPB bridge to allow data exchanges on these two buses. Other hierarchical bus architectures [4, 3, 54] apply similar schemes but utilize different protocols and hardware modules.

In Figure 2.1, Hierarchical bus is above the arbitrated bus. It increases the connectivity and allows the connections of more cores than a single bus architecture. On the other hand, while it still able to coordinate on-chip data paths among heterogeneous components as a bus architecture, certain flexibility is sacrificed since the some of the communications have to go across a bus bridge.

#### 2.1.4 FPGA-Like Architecture

An alternate approach allows for static scheduling and programmable interconnect such as the type found in field-programmable gate arrays (FPGAs). To provide simplicity, this architecture employs a static network, whose configuration is decided at compile-time. With limited flexibility, the wires in such static networks are dedicated to a given communication link and does not support wire reuse. Most of these architectures can only change its communication network by rewriting the configurations [74, 24]. The connectivity of many FPGA-like architectures are also less than the fixed point-to-point connection since some nodes have to go across a couple switches to communicate. To simplify the architecture, the network is built for homogeneous small cores. Typical FPGA-like architectures can be found in MATRIX [74], CHESS Array [70], DP-FPGA [24] and Wan et al. [104]. As an exception, Pleiades [66] presents a hierarchical static crossbar-based network using heterogeneous coarse cores.

In Figure 2.1, it can be seen that the FPGA-like circle is located between the Fixed and Bus, which indicates that this architecture is not as flexible as bus or hierarchical bus, but better than fixed connections. On the other axle, FPGA-like architectures have better connectivity for its mesh communication network but weaker than fixed architectures due to the overhead of switches. This architecture is relatively cheaper in hardware resources with less flexibility and connectivity.

#### 2.1.5 Network-on-Chip (NoC)

Network-on-chip (NoC) is a network of computational, storage and I/O resource, interconnected by a network of switches. Resources communicate with each other using addressed data packets routed to their destination by the switch fabric [50]. Similarly, researchers at Stanford University propose a SoC interconnect using packet-switching [31]. The idea of performing on-chip dynamic routing is described and simulated but is not yet implemented. MicroNetwork [106] provides on-chip communication via a pipelined interconnect. A rotating resource arbitration scheme is used to coordinate inter-node transfer for dynamic requests. This mechanism is limited by the need for extensive user interaction in design mapping.

The architecture of pipelined packet-switched interconnect has been used effectively for multiprocessor communication for over 25 years. Compile-time static routing of communication has been used effectively in a number of parallel processing systems. In iWarp [20], inter-processor communication patterns were determined during program compilation and were implemented with the aid of programmable, inter-processor buffers. This concept has been extended by the NuMesh project [92] to include collections of heterogeneous processing elements interconnected in a mesh topology. While pre-scheduled routing is appropriate for static data flows with predictable communication paths such as those found in DSP, most applications rely on at least minimal run-time support for data-dependent data transfer. Often, this support takes the form of complicated per-node dynamic routing hardware embedded within a communication fabric.

To reduce the affects of clock skew in large chips, the technique of Global Asynchronous Local Synchronous (GALS) are proposed [75, 105, 56, 77]. GALS provides asynchronous interfaces between cores which allows the cores to work on different clock speed. When solving the problems for data to travel across clock domain, GALS further increases the complexity of NoC architecture.

Recently, researcher in Fulcrum Microsystems presents the Nexus, a verified GALS interconnect ready for commercial usage [69], which is able to efficiently interconnect SoCs modules with different clock domains. The Nexus system features a crossbar with the IP cores around it. While heterogeneous IPs with different clock frequencies are allowed, clock-domain converters connect the local synchronous modules to the asynchronous crossbar. The crossbar, which is designed with the asynchronous-circuit techniques and based on the quasi-delay-insensitive (QDI) timing model, carry the data across the chip. All parts of the system are safely flow controlled and arbitration is employed to resolve the contention on output ports. The Nexus system supports 16 ports with each of 36-bit. In the 130-nm generic logic process, it operates at a frequency of 480 MHz at 1.5V and  $25^{\circ}C$ . For a typical Nexus system,  $4.15 \ mm^2$  is used. The Nexus system provides an efficient on-chip interconnect architecture for SoCs with different clock domains. However, since the asynchronous crossbar can be occupied by only one port at a time, data congestion is unavoidable, which limits the scalability of the system.

To be applied in on-chip communications, NoC provides a highly scalable solution. For this reason, NoC is located on the far top of Figure 2.1. It requires complicated circuits for the dynamic routing, buffering, flow control and interfacing. This solution is proposed for next generation large systems having over one billion transistors [50]. To reduce the overhead of communication network, a coarse granularity is preferred.

A recent example of this approach can be found in the Reconfigurable Architecture Workstation (RAW) project [103], which provides both a static (determined at compile-time) and dynamic (determined at run-time) network. Limiting the dynamic routing and relying mostly on the static network, RAW simplifies its architecture and sacrifices flexibility.

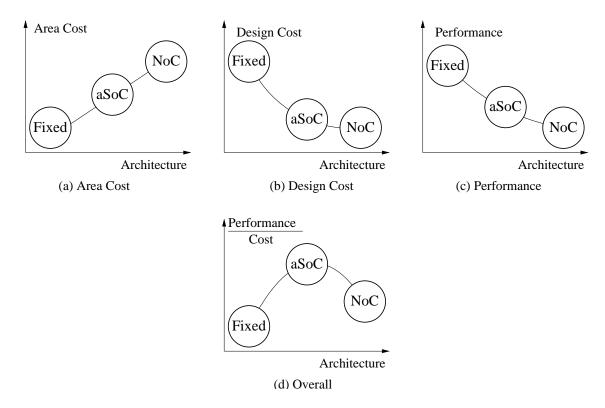

Figure 2.2. Illustration of Relative Tradeoff between Architectures

#### 2.1.6 Comparisons on Performance and Cost

As shown in Figure 2.1, both fixed point-to-point architecture and NoC have high connectivity. The aSoC has been designed to have high connectivity in the design space. By trading flexibility, aSoC is able to provide required communication bandwidth with affordable circuit complexity. Further analysis has been done in the following to reveal the trade-offs between these architectures.

Besides connectivity and flexibility, other important aspects of hardware architectures include simplicity and performance. Since quantitative comparison depends on the detailed architecture of a module, relative analysis is used to explore their relationships. Figure 2.2 presents a relative comparison between the three architectures of aSoC, NoC and fixed in terms of area cost, design time cost, and performance.

The fixed point-to-point architecture, as a customized design architecture, can achieve top performance with more efficient area usage than aSoC and NoC as

shown conceptually in Figure 2.2(c) and Figure 2.2(a). However, as the system size increases, this advantage will be diluted by the huge amount of wires required for full connection. On the other hand, the design time cost of fixed point-to-point architecture is very expensive when any change in a system is required. The whole communication architecture has to be redesigned if a IP core is removed from or added into a system. The prohibitive design cost violates the divide and conquer idea of SoCs and generates poor performance to cost ratio as illustrated in Figure 2.2(d).

On the contrary, the design cost for NoC is almost ignorable. NoC employs a regular communication network for the IP cores. Once the network and the interfaces are set up, it costs little to put in another IP core into the system. As illustrated in Figure 2.2(b), NoC achieves the lowest design cost among the three architectures. As mentioned in Section 2.1.5, the NoC design comes with the cost of complex circuitry to deal with the packets and routing, which increases the area usage and reduces the performance.

#### 2.1.7 Position of aSoC in the Design Space

As described above, present on-chip communication architectures have their pitfalls while providing some useful features. The NoC requires huge area resources to support its flexible communication network, and no physical design has been established as far as we know. The fixed point-to-point architecture has efficient area mapping, but its cost to design the system is prohibitive when IP cores need to be changed. FPGA-like architectures are limited by their flexibility and the bus architectures are limited by the bandwidth they can provide. To fulfill the requirements of the next generation on-chip communication, a new architecture has to be created.

ASoC is designed to fill in the gap between these existing communication architecture for the next generation SoCs. Compared to the above mentioned on-chip communication methodologies, aSoC provides a better overall performance to cost ratio. For SoCs, the cost means not only the area resources but also the design cost. The concept of SoC is proposed to reduce the prohibitive design cost for chips with large amount of transistors. A communication architecture for SoCs cannot ignore the design cost and just focus on other issues. As a result, the evaluated cost includes both the area resources and the design cost.

Several techniques are employed to guarantee aSoC a better performance to cost ratio. A packet-switching scheme is used in aSoC to provide high connectivity, and pipelined near-neighboring wires enable aSoC a high clock speed. By using static-scheduling, aSoC can be implemented with a simpler circuitry than NoC. To better understand the position of aSoC in the design space, the relationships between aSoC and other architectures in terms of connectivity, flexibility, cost and performance are discussed.

• Connectivity. One of most important goals for aSoC is to provide scalable communication bandwidth for SoCs. High connectivity is necessary for aSoC to achieve this goal. A regular 2-D mesh communication network is employed to provide the required bandwidth. In such an mesh, each core can communicate with its four neighbors in a clock cycle. A packet-switching scheme is used on the aSoC network to transfer the data between local cores, which allows wires to be shared by different communications at different time cycles so that limited number of wires are able to provide a connectivity competitive to fixed point-to-point architecture. As shown in Figure 2.1, aSoC is located at the same connectivity level of NoC and fixed point-to-point.

• Flexibility. ASoC has a higher flexibility than the FPGA-like and fixed point-to-point architectures. With a packet-switching scheme, the connections of the aSoC network is changed by control instructions every cycle in every network node. As a comparison, fixed point-to-point architecture can not change its communication pattern once the chip is fabricated, and the FPGA-like architecture can only modify its connecting settings once per application by reconfiguring the entire chip. In Figure 2.1, aSoC is to the left of both fixed point-to-point and the FPGA-like architecture.

Compared to NoC, aSoC has lower flexibility in order to reduce circuit complexity. ASoC employs a static scheduling scheme, with which the communication patterns are pre-scheduled at compile time. The changes of the aSoC network connections are controlled by pre-set instructions, unlike the fully run-time dynamic changing in NoCs or buses. Further analysis indicates that the reduced flexibility of aSoC does not affect the performance of aSoC. ASoC is designed for the high data rate DSP applications. In many cases, the DSP applications are running with predictable communication patterns which are able to be determined by the static scheduling at compile time. In addition, aSoC also supports dynamic communication pattern switching with the dynamic data dependent control. With all the techniques, aSoC is flexible enough to support its target applications.

• Area Cost. As mentioned above, the loss in flexibility buys aSoC a lot of simplicity by employing a static scheduling and avoiding the dynamic arbitration. The concepts of NoC have been simulated in software to validation its performance, but, as far as we know, no hardware implementation has been built due to its resource requirement for arbitration and buffers. With static scheduling, aSoC is able to achieve high connectivity with a simple architecture,

which will be described in detail in Chapter 3.

Simpler than NoC, aSoC is considered more expensive than a customized fixed point-to-point architecture in small system, which is illustrated in Figure 2.2(a). However, in large systems, fixed point-to-point architectures will lose because of their exponential increase in system size.

• Design Cost. ASoC provides a communication platform for heterogeneous SoCs. It allows SoCs to choose various IP cores from pre-designed libraries or third-part IP core vendors. With a regular mesh architecture and well-defined the interfaces between cores and the communication network, low design cost is required to design a SoC containing different cores. As a result, aSoC has a low design cost compared with the customized fixed point-to-point architecture, which is presented in Figure 2.2(b).

While carefully compared to NoC architecture, aSoC supports heterogeneous cores. As a result, the aSoC interface has to communicate across clock domain to various local IP cores. It introduces some more design overhead compared to NoC. Once a proper core interface protocol is established, this overhead is negligible and results in a design cost very close to NoC. In addition, the overhead is worthwhile considering the performance benefits brought by the heterogeneous cores suitable for applications.

• Performance. ASoC architecture aims to provide scalable communication bandwidth for SoCs. Based on the common sense of scalability, aSoC should be able to improve performance with the size of the system increases. To achieve this goal, the packet-switching mesh network is employed to guarantee a high connectivity, the near-neighboring pipeline wires are used for high clock speed, and static-scheduling is designed to avoid data congestion. With all these schemes, aSoC can achieve a better performance than the NoC since it

can run at a high clock speed and NoC requires the dynamic arbitration and suffers from the data congestion.

ASoC is not designed to beat the performance of fixed point-to-point architecture, since, with a customized design, fixed architecture can be refined for a given application with sufficient effort in designing. Figure 2.2(c) illustrates the relationship in performance between aSoC, NoC and fixed point-to-point architecture.

Combining the features mentioned above, aSoC achieves a better performance/cost and fills in the gap between the NoC, FPGA-like and fixed point-to-point architectures. As illustrated in Figure 2.2(d), aSoC has better performance to cost ratio than fixed point-to-point architecture and NoC. The static scheduling packet-switching architecture of aSoC avoids the prohibitive design cost required in fixed point-to-point architectures. Compared to NoC, aSoC wins because of its smaller area resources requirement and better performance.

## 2.2 SoC Supporting Softwares

Generally, an application is specified in a high-level language(HLL) such as C/C++ or FORTRAN. A compiler converts the HLL into an intermediate representation(IR), which contains the necessary control and data dependency information. It is then applied to a more complex and machine-dependent phase that includes the following stages: instruction selection, scheduling, resource allocation, code optimizations/transformations, and code generation [95]. Unfortunately, the effectiveness of these stages depend heavily on the target architecture, chosen algorithm, and optimal ordering. So, for a core-changeable SoC, pre-existing core compilers are often applied in optimizing the codes for each core.

To date, few integrated compilation environments have been created for heterogeneous systems-on-a-chip. The MESCAL system [60] provides a high-level

programming interface for embedded SoCs. Though flexible, this system is based on a communication protocol stack which may not be appropriate for data stream-based communication. Several projects [62] [63] have adapted embedded system compilers to SoC environments. These compilers target bus-based interconnect rather than a point-to-point network. Previous work in system synthesis provides some direction regarding compilation for SoC systems. Cost-based tradeoffs between hardware, software, and communication were evaluated by Wan et al. [104]. In Dick and Jha [84], partitioning was followed by a hill-climbing based task placement stage. In Lee et al. [64], a loop-based partitioner and space-time scheduler were used to isolate tasks to specific cores and to coordinate communication. This software system and the system described in [104] contain front-end interfaces to high-level languages through standard intermediate forms.

As another example, Pleiades[66] uses an energy-conscious methodology to guide its mapping and partitioning. Most commercial SoC compilers, such as PSoC[29] and CSoC[108], allow users to specify the task for each core. In Triscend CSoC compiler, FastChip, users can choose either software, dedicated hardware or configurable hardware to implement a given function. Either HLL(c,HDL) or net-lists can be used as the input. A built-in compiler is then applied to convert the application into configure data for CSoC.

But most compilers are unable to coordinate the inter-core communications to reduce potential congestion, since they target a bus or hierarchical bus template. Some compilers for packet-switched systems did reduce congestion. As mentioned above, RAW[64], NuMesh[92], and iWarp[20] support static scheduling and packet-switched communication. Their supporting software can pre-schedule the data communication at compile time to avoid congestion.

iWarp ConSet model schedules a phase-based communication model. The phase means a group of pathways which can be active at the same time. Each iWarp cell has 20 logic channels allowing up to 20 pathways at one time. Pathways in different phases can share the hardware resources. Extra control circuits and time are dedicated to phase changing. Because of the synchronization of the cells, the time required for phase changing is quite significant. Dijkstra's algorithm is applied in ConSet to find the shortest path for pathways. On NuMesh, a Communication OPerator language(COP[71]) is built to optimize the phase and data transfer organizations. The routing kernel of COP is developed from hierarchical commodities flow routing. The RAW machine assumes that the network contention is low. Most performance improvement focus on the scheduler. So, the dimension-ordered routing is employed.

As a compiler for aSoC, AppMapper differs from the above compilers as explained below:

- No congestion: Only static routing is used in AppMapper, which means that all data communications are scheduled by AppMapper in such a way that runtime congestion cannot happen.

- Scalability: Instead of hierarchical commodities flow algorithm, AppMapper's space-time routing is based on a shortest path search algorithm whose complexity is associated with the number of data streams not the system size.

- Simpler: aSoC communication architecture is more compact than multi-processor systems. All the data communication is scheduled in one loop. Without the overhead of phase-changing as in iWarp and NuMesh, the communication interface saves silicon area.

- Decouple with cores: Rather than being fixed, the cores in aSoC can be selected from a group of candidates.

• *Higher throughput:* Without the congestion of bus and the phase-changing and dynamic routing overhead of multiprocessor systems, AppMapper expects high throughput.

## CHAPTER 3

#### ASOC OVERVIEW

# 3.1 aSoC Design Philosophy

Successful deployment of adaptive systems-on-a-chip (aSoC) requires the architectural development of an inter-node communication interface, the creation of supporting design mapping software, and the successful translation of target applications. Before discussing these issues, the basic operating model of aSoC interconnect is presented.

## 3.1.1 Design Overview

As shown in Figure 1.1, a standardized communication structure provides a convenient framework for the use of intellectual property (IP) cores. A simple core interface protocol, joining the core to the communication network, creates architectural modularity. By limiting inter-core communication to short wires exhibiting predictable performance, high-speed point-to-point transfer is achieved. Since heterogeneous cores can operate at a variety clock frequencies, the communication interface provides both data transport and synchronization between processing and communication clock domains.

Inter-core communication using aSoC takes place in the form of data *streams* [92] which connect data sources to destinations. To achieve the highest possible bandwidth, our architecture is targeted towards applications, such as video, communications, and signal processing, that allow most inter-core communication patterns to be extracted at compile time. By using the mapping tools, described

Figure 3.1. Multi-core data streams 1 and 2. This example shows data streams from Tile A to Tile E and from Tile D to Tile F. Fractional bandwidth usage is indicated in italics.

in Chapter 4, it is possible to determine how much bandwidth each inter-core data stream requires relative to available communication channel bandwidth. Since stream communication can generally be determined at compile time [92], our system can take advantage of minimized network congestion by scheduling data transfer in available data channels.

As seen in Figure 3.1, each stream requires a specific fraction of overall communication link bandwidth. For this example,  $Stream\ 1$  consumes  $\frac{0.5}{1}$  of available bandwidth along links it uses and  $Stream\ 2$  requires  $\frac{0.25}{1}$ . This bandwidth is reserved for a stream even if it is not used at all times to transfer valid data. At specific times during the computation, data can be injected into the network at a lower rate than the reserved bandwidth, leaving some bandwidth unused. In general, the path taken by a stream may require data transfer on multiple consecutive clock cycles. On each clock cycle, a different stream can use the same communication resource. The assignment of streams to clock cycles is performed by a communication scheduler based on required stream bandwidth. Global communication is broken into a series of step-by-step hops that is coordinated by a distributed set of individual

Figure 3.2. Pipelined stream communication across multiple communication interfaces

tile communication schedules. During communication scheduling, near-neighbor communication is coordinated between neighboring tiles. As a result of this bandwidth allocation, the dynamic timing of the core computation is decoupled from the scheduled timing of communications.

The cycle-by-cycle behavior of the two example data streams in Figure 3.1 is shown in Figure 3.2. For *Stream 2*, data from the core of *Tile D* is sent to the left (West) edge of *Tile E* during communication clock cycle 0 of a four-cycle schedule. During cycle 1, connectivity is enabled to transfer data from *Tile E* to the West edge of *Tile F*. Finally, in cycle 2 the data is moved to its destination, the core of *Tile F*. During four consecutive clock cycles, **two** data values are transmitted from *Tile A* to *Tile E* in a pipelined fashion forming *Stream 1*. Note that the data stream is pipelined and the physical link between *Tile D* and *Tile E* is shared between the two streams at different points in time. Stream transfer schedules are iterative. At the conclusion of the fourth cycle, the four-cycle sequence re-starts at cycle 0 for new pieces of data. The communication interface serves as a cycle-by-cycle switch for stream data. Switch settings for the four-cycle transfer in Figure 3.2 are shown in Table 3.1.

| Cycle | Tile A        | Tile D        | Tile E       | Tile F       |

|-------|---------------|---------------|--------------|--------------|

| 0     | core to south | core to east  |              |              |

| 1     | core to south | north to east | west to east |              |

| 2     |               | north to east | west to core | west to core |

| 3     |               |               | west to core |              |

Table 3.1. Communication schedules for tiles in Figure 3.2

Stream-based routing differs from previous static routing networks [20]. Static networks demand that all communication patterns be known at compile time along with the exact time of all data transfers between cores and the communication network. Unlike static routing, stream-based routing only requires that bandwidth be allocated but not necessarily used during a specific invocation of the transfer schedule. Communication is set up as a pipeline from source to destination cores. This approach does not require the exact timing of all transfers, but rather, data only needs to be inserted into the correct stream by the core interface at a communication cycle allocated to the stream. Computation can be overlapped with communication in this approach since the injection of stream data into the network is decoupled from the arrival of stream data.

#### 3.1.2 Flow Control

Since cores may operate asynchronously to each other, individual stream data values must be tagged to indicate validity. When a valid stream data value is inserted into the network by a source core at the time slot allocated for the stream, it is tagged with a single valid bit. As a result of communication scheduling, the allocated communication cycle for stream data arrival at a destination is predefined. The data valid bit can be examined during the scheduled cycle to determine if valid data has been received by the destination. If data production for a stream source temporarily runs ahead of data consumption at a destination, data for a specific stream can temporarily back up in the communication network. To avoid deadlock,

data buffer storage is required in each intermediate communication interface for each stream passing through the interface. With buffering, if a single stream is temporarily blocked, other streams which use the affected communication interfaces can continue to operate unimpeded. A data buffer location for each stream is also used at each core-communication interface boundary for intermediate storage and clock synchronization.

The use of flow control bits and local communication interface buffering ensures data transfer with the following characteristics:

- All data in a stream follows the same source-destination path.

- All stream data is guaranteed to be transfered in order.

- In the absence of congestion, all stream data requires the same amount of time to be transferred from source to destination

- Computation is overlapped with communication.

#### 3.1.3 Run-time Stream Management

For a number of real-time applications, inter-core communication patterns may vary over time. This requirement necessitates the capability to invoke and terminate streams at various points during application execution and, in some cases, to dynamically vary stream source and destination cores at run-time. In developing our architecture, we consider support for the following two situations: (1) all necessary streams required for execution are known at compile-time but are not all active simultaneously at run-time and, (2) some stream source-destination pairs can only be determined at run-time.

## 3.1.3.1 Asynchronous Global Branching