1.

- Learning how to use interrupts.

- Interfacing to an external bus.

- State machines in a PLD.

- Data handshaking.

- Moving towards a full system.

- Improve on Lab 1

- **\*** Efficient printing of character strings

- $\star$  Program Timer 0.

- Interface 7032 PLDs to 16F877.

- one switch attached to PLD input

- four LEDs attached to PLD output.

- 16F877 reads switch inputs, write LEDs

- Four bit counter created inside PLD.

- Value echoed to terminal if switch value changes.

— Need to set interrupt vector.

— Need to return from interrupt.

|          | org<br>goto | H'000'<br>Mainline |   | Reset vector<br>Location of start of program                   |

|----------|-------------|--------------------|---|----------------------------------------------------------------|

| Mainline | 0           | H'004'<br>IntServ  | • | Interrupt vector<br>Start of int service routine               |

|          | ••••        |                    |   |                                                                |

| IntServ  | org<br>     | Н'100'             | • | put service routing at 0x100<br>first inst. of service routine |

|          | <br>retfie  |                    | ; | return from interrupt instr.                                   |

- 1. Interrupts enabled (INTCON, PIE1)

- 2. Interrupt stimulus (timer/counter overflows)

- 3. Interrupts disabled (bit 7 INTCON)

- 4. Jump to interrupt vector (address 0x4).

- 5. Jump to interrupt service routine.

- 6. Complete interrupt service routine.

- 7. Re-enable interrupts (RETFIE).

### PIC16F87X

2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                           | R/W-0      | R/W-0                                  | R/W-0       | R/W-0     | R/W-0 | R/W-x |                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------|-------------|-----------|-------|-------|----------------------------------------------------------------------------------------------------------------------|

| GIE    | PEIE                                                                                                                                                                                                                                                                            | TOIE       | INTE                                   | RBIE        | TOIF      | INTF  | RBIF  | R = Readable bit                                                                                                     |

| bit7   |                                                                                                                                                                                                                                                                                 |            |                                        |             |           |       | bit0  | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7: | it 7: GIE: Global Interrupt Enable bit<br>1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                                                                                                                                                   |            |                                        |             |           |       |       |                                                                                                                      |

| bit 6: | 1 = Enab                                                                                                                                                                                                                                                                        | les all un | nterrupt Er<br>masked p<br>ripheral in | eripheral i | nterrupts |       |       |                                                                                                                      |

| bit 5: | <b>TOIE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                                                                                                            |            |                                        |             |           |       |       |                                                                                                                      |

| bit 4: | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                                                                                                        |            |                                        |             |           |       |       |                                                                                                                      |

| bit 3: | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                      |            |                                        |             |           |       |       |                                                                                                                      |

| bit 2: | <b>TOIF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                                                          |            |                                        |             |           |       |       |                                                                                                                      |

| bit 1: | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur                                                                                                      |            |                                        |             |           |       |       |                                                                                                                      |

| bit 0: | <ul> <li>0 = The RB0/INT external interrupt did not occur</li> <li><b>RBIF</b>: RB Port Change Interrupt Flag bit</li> <li>1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)</li> <li>0 = None of the RB7:RB4 pins have changed state</li> </ul> |            |                                        |             |           |       |       |                                                                                                                      |

DS30292B-page 20

© 1999 Microchip Technology Inc.

## PIC16F87X

#### 2.2.2.4 PIE1 REGISTER

The PIE1 register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

| REGISTER 2-4: | PIE1 | REGISTER | (ADDRESS 8Ch) |

|---------------|------|----------|---------------|

|---------------|------|----------|---------------|

| R/W-0                | R/W-0                                                                                                                                                                             | R/W-0       | R/W-0       | R/W-0       | R/W-0         | R/W-0        | R/W-0  |                                                                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|---------------|--------------|--------|--------------------------------------------------------------------------------------|

| PSPIE <sup>(1)</sup> | ADIE                                                                                                                                                                              | RCIE        | TXIE        | SSPIE       | CCP1IE        | TMR2IE       | TMR1IE | R = Readable bit                                                                     |

| bit7                 |                                                                                                                                                                                   | I           | L           | 1           | I             | I            | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n= Value at POR reset |

|                      | bit 7: <b>PSPIE</b> <sup>(1)</sup> : Parallel Slave Port Read/Write Interrupt Enable bit<br>1 = Enables the PSP read/write interrupt<br>0 = Disables the PSP read/write interrupt |             |             |             |               |              |        |                                                                                      |

|                      | ADIE: A/D<br>1 = Enable<br>0 = Disabl                                                                                                                                             | es the A/D  | converte    | r interrupt |               |              |        |                                                                                      |

|                      | RCIE: US<br>1 = Enable<br>0 = Disabl                                                                                                                                              | es the US/  | ART recei   | ve interrup | ot            |              |        |                                                                                      |

|                      | <b>TXIE</b> : USART Transmit Interrupt Enable bit<br>1 = Enables the USART transmit interrupt<br>0 = Disables the USART transmit interrupt                                        |             |             |             |               |              |        |                                                                                      |

|                      | SSPIE: Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt                                                            |             |             |             |               |              |        |                                                                                      |

|                      | CCP1IE: CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                                                                            |             |             |             |               |              |        |                                                                                      |

|                      | <b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt                             |             |             |             |               |              |        |                                                                                      |

|                      | TMR1IE: TMR1 Overflow Interrupt Enable bit         1 = Enables the TMR1 overflow interrupt         0 = Disables the TMR1 overflow interrupt                                       |             |             |             |               |              |        |                                                                                      |

| Note 1:              | PSPIE is re                                                                                                                                                                       | served on 2 | 28-pin devi | ces; always | maintain this | s bit clear. |        |                                                                                      |

© 1999 Microchip Technology Inc.

DS30292B-page 21

# **RETFIE** Instruction

## PIC 16F877

### PIC16F87X

| RETFIE                  | Return from Interrupt       | RLF              | Rotate Left f through Carry                                                                                                                                                                                      |

|-------------------------|-----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                 | [label] RETFIE              | Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                         |

| Operands:<br>Operation: | None $TOS \rightarrow PC$ , | Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                               |

| oporation               | $1 \rightarrow \text{GIE}$  | Operation:       | See description below                                                                                                                                                                                            |

| Status Affected:        | None                        | Status Affected: | С                                                                                                                                                                                                                |

|                         |                             | Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the<br>result is placed in the W register.<br>If 'd' is 1, the result is stored back<br>in register 'f'. |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two cycle instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Operation:       | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Status Affected: | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'.<br>$\circleterflow \circleterflow \$ |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                                 |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two cycle<br>instruction. |  |  |  |

| SLEEP            |                                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> SLEEP<br>]                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \mbox{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                         |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |

| Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |

© 1999 Microchip Technology Inc.

DS30292B-page 143

### PIC 16F877

### PIC16F87X

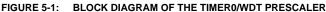

#### 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- · 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- · Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PICmicro<sup>™</sup> Mid-Range MCU Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the watchdog timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

#### 5.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

© 1999 Microchip Technology Inc.

DS30292B-page 47

- Initialize timer 0 to overflow about every .0327 seconds.

- $\star$  See example on page 100 of Peatman.

- Force interrupt when counter overflows.

- When interrupt occurs, toggle Port C, bit 2.

- Be sure to initialize appropriate registers.

- Goal: Use ports A, B, C, D to exchange data with PLD.

- Port A four bit address value.

- Port B four bit data input.

- Port C up to six control signals.

- Port D four bit data output.

- Create a four-bit write and read transaction.

- Transfer should be robust.

- Valid signals indicate when data transfer occurs.

- Four bit *address* followed by *data*.

- For a PIC write, PIC must wait for acknowledge.

- For a PIC read, PLD must wait for data acknowledge.

- Use 4MHz clock for both PIC and PLD.

- Show handshaking signals on logic analyzer.

- Configure port C data direction register.

- PIC data valid/EPLD data accept (PICSTROBE)

Port C output.

- PIC data accept/EPLD data valid (PLDSTROBE) Port C input.

- PIC Read/Write signal  $(R/W_{-})$ Port C output.

- Could use other encodings.

- Interface 12 address/data + control signals to PIC.

- One switch input into PLD.

- Four LED outputs from PLD.

- Four bit internal register.

- Address and  $R/W_{-}$  used to select destination.

After port A, B, C, D initialization:

- 1. Send address to Port A.

- 2. Set  $R/W_{-}$  signal to read.

- 3. Assert PICREADY signal.

- 4. Sample PLDREADY to see if PLD has address.

- 5. When PLDREADY asserted, deassert PICREADY.

- 6. Wait for PLDREADY deasserted.

- 7. Repeat previous six steps with *data* on Port D.

After port A, B, C, D initialization:

- Similar address transaction as write.

- Read value from EPLD to port B.

- Follow sequential rules.

- Data shouldn't be overwritten.

- Can be simulated with MPSIM

- Implement using VHDL.

- One state machine to check/fetch addresses.

- $\star$  check PICREADY.

- $\star$  assert/deassert PLDREADY

- One state machine for READ transactions:

- $\star$  Decode address.

- \* Enable correct location (switches, register)

- $\star$  Assert data to Port B.

- One state machine for WRITE transactions:

- $\star$  Decode address.

- \* Enable correct location (LEDs, register)

- $\star$  Read data from Port D to correct location.

- Need to display a string of characters.

- Consider printing string "wow"

| call  | wait  | ; subroutine which checks PIR bit 4. |

|-------|-------|--------------------------------------|

| movlw | 'w'   | ; send ASCII w char. to W            |

| movwf | TXREG | ; send w char. to UART trans. buffer |

| call  | wait  | ; subroutine which checks PIR bit 4. |

| movlw | °0'   | ; send ASCII o char. to W            |

| movwf | TXREG | ; send o char. to UART trans. buffer |

| call  | wait  | ; subroutine which checks PIR bit 4. |

| movlw | 'w'   | ; send ASCII w char. to W            |

| movwf | TXREG | ; send w char. to UART trans. buffer |

— Approach is clumsy, verbose.

— Before introducing the new approach, consider this code.

|       | ORG 0x0<br>goto Start | ; jump to the start of the program |

|-------|-----------------------|------------------------------------|

|       | ORG 0x5               |                                    |

| sub1  | nop                   | ; start of a subroutine            |

|       |                       |                                    |

|       | return                | ; return from subroutine           |

|       |                       |                                    |

|       | ORG 0x30              |                                    |

| Start |                       |                                    |

|       | •                     |                                    |

|       | call sub1             | ; call the routine                 |

|       | nop                   | ; first instr. after return        |

— When *call* is executed the following happens:

- 1. PC receives address of *sub1*

- 2. top of stack (TOS) receives return addr.

- When *return* is executed the following happens:

- 1. PC receives top of stack (TOS), the return address.

- Consider a new instruction RETLW k

- When retlw is executed the following happens:

- 1. PC receives top of stack (TOS), the return address.

- 2. The constant value k is placed in the W register

- What if the k value was a character?

# Character String Program

## PIC 16F877

| BANKORAN      | 4 EQU H'20'<br>ORG BANKORAM<br>cblock<br>POINTER<br>endc                                       | ; equate a constant to hex 20.<br>; reserve space in DATA MEMORY<br>; create a pointer in bank 0 at location 20<br>; name of value |

|---------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|               | ORG 0x0<br>goto Start                                                                          | ; jump to the start of the program                                                                                                 |

| sub1          | ORG 0x5<br>movf POINTER, W<br>addwf PCL, F<br>retlw A'w'<br>retlw A'o<br>retlw A'w'<br>retlw O | ; move value in POINTER to W<br>; add value to PC                                                                                  |

|               | RETURN                                                                                         | ; shouldn't get here                                                                                                               |

| Start<br>Loop | ORG 0x30<br>clrf POINTER<br>call sub1                                                          |                                                                                                                                    |

| -             |                                                                                                | ; check if return value is 0                                                                                                       |

|               | btfsc status, z                                                                                | ; branch if not 0                                                                                                                  |

|               | goto Done                                                                                      | ; else done                                                                                                                        |

|               |                                                                                                | ; check bit 4 in PIR                                                                                                               |

|               | movwf TXREG                                                                                    |                                                                                                                                    |

|               | •                                                                                              | ; increment POINTER                                                                                                                |

|               | goto Loop                                                                                      | ; print another character                                                                                                          |

|               | ORG 0x60                                                                                       |                                                                                                                                    |

| Done          | nop                                                                                            |                                                                                                                                    |

| goto Do       | one                                                                                            |                                                                                                                                    |

| 20            |                                                                                                | Peatman - page 49                                                                                                                  |

| 20            |                                                                                                | i caunan - page 45                                                                                                                 |

— Possible to replace numerous RETLW instructions with dt directive.

```

BankO MACRO ; macro to select bank 0

bcf STATUS, RPO

bcf STATUS, RP1

ENDM

```

- Make 16F877 macros for read/write transactions.

- Macros are *expanded* by assembler.

- Later changes can be confined to macro.

- Rewire lab kit for lab two (PLD, clock)

- Implement using VHDL.

- Demonstrate using logic analyzer.

- Implement serial interface using constant strings.

- Implement timer 0 interrupt and LED toggle.

- Check write transaction first.

- Look at signals on analyzer.

- Debug read transaction.

- Get interrupts with timer working.

- Get constant string code working.

- Demonstrate working system.

- Peatman chapter 5

- Peatman pages 100-103

- Peatman section 8.7 (skim)

- 16F877 data sheet pages 46-49

- 16F877 data sheet pages 131-133

- 16F877 data sheet pages 20-21

- Altera 7032 data sheet

- Display constant strings using directive dt.

- Program counter to toggle LED with interrupts.

- Implement bus transaction with PLD.

- VHDL state machines in PLD to handle data transfer.

- Logic analyzer usage.