1.

- Learning the architecture of the PIC16F877

- Learning the instruction set of the PIC16F877

- Understanding chip power-up.

- Practice with 16F877 debugging equipment

- Implementation of serial I/O

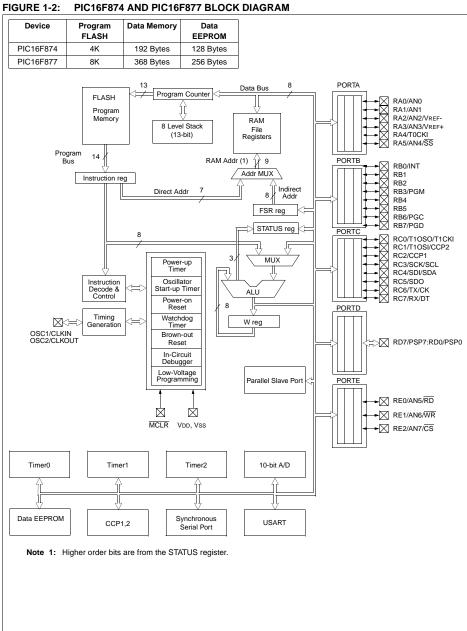

Figure 2-1 of 16F877 data sheet.

- Two main instances of reset

- $\star$  Power applied to 16F877

- $\star \overline{MCLR}$  asserted active low

- goto Start located at instruction memory location 0000h.

- Note that reset vector allocated *four* 14-bit values

- First program instruction could be located at 0005h

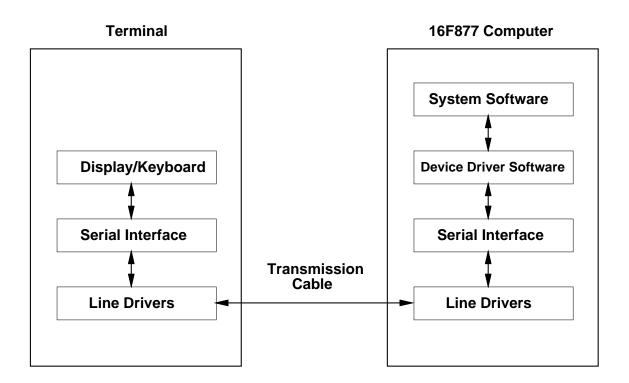

- Two bit cable connects computer/terminal (receive/transmit).

- Keystroke sends character to 16F877

- 16F877 character transmission sends a value to terminal screen

## Serial Data Transmission

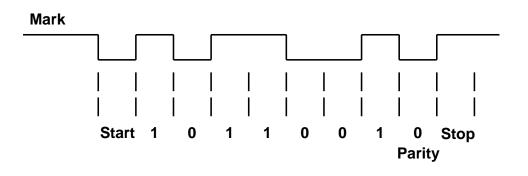

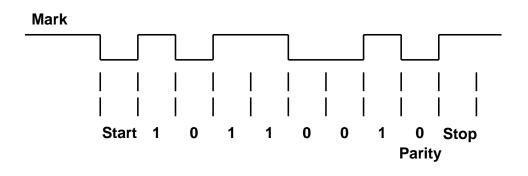

- Inactive *mark* indicates no activity

- Start bit indicates beginning of data transfer

- Seven bit character transmitted

- Even parity indicates even number of ones.

- Single stop bit indicates completion of transfer.

<sup>© 1999</sup> Microchip Technology Inc.

## Serial Data Transmission

|                   |     |          | $b_6b$       | $_{5}b_{4}$  |              |     |

|-------------------|-----|----------|--------------|--------------|--------------|-----|

|                   | ••• | 3        | <b>4</b>     | <b>5</b>     | 6            | ••• |

| $b_3 b_2 b_1 b_0$ | ••• | 011      | 100          | 101          | 110          | ••• |

| 0000              | ••• | 0        | 0            | Р            | ,            | ••• |

| 0001              | ••• | 1        | $\mathbf{A}$ | $\mathbf{Q}$ | a            | ••• |

| 0010              | ••• | <b>2</b> | В            | $\mathbf{R}$ | $\mathbf{b}$ | ••• |

| 0011              | ••• | 3        | $\mathbf{C}$ | $\mathbf{S}$ | С            | ••• |

| 0100              | ••• | <b>4</b> | $\mathbf{D}$ | $\mathbf{T}$ | $\mathbf{d}$ | ••• |

| 0101              | ••• | <b>5</b> | $\mathbf{E}$ | $\mathbf{U}$ | e            | ••• |

- UART receives eight bit value (D0-D7)

- UART serializes data and adds control/parity bits

- UART outputs 0 to 5V signal.

- RS-232 driver/receiver converts output to  $\pm 10 V$

## **16F877 UART Implementation**

- Operates as parallel/serial transmitter

- Operates as serial/parallel receiver

- Accessed via special-purpose registers

- $\star$  Each accessed with a separate address

- \* Control/status registers (RCSTA, TXSTA)

- \* Baud rate generator (SPBRG)

- \* Data registers (TXREG, RCREG)

- \* Interrupt registers (PIR1, PIE1)

# 16F877 Data Memory and Register Files

### PIC16F87X

| Indirect addr.(*)                          | 00h | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h | Indirect addr.(*)                          | 180 |

|--------------------------------------------|-----|--------------------------------------------|------------|--------------------------------------------|------|--------------------------------------------|-----|

| TMR0                                       | 01h | OPTION REG                                 | 81h        | TMR0                                       | 100h | OPTION_REG                                 | 181 |

| PCL                                        | 02h | PCL                                        | 82h        | PCL                                        | 102h | PCL                                        | 182 |

| STATUS                                     | 02h | STATUS                                     | 83h        | STATUS                                     | 102h | STATUS                                     | 183 |

| FSR                                        | 04h | FSR                                        | 84h        | FSR                                        | 104h | FSR                                        | 184 |

| PORTA                                      | 05h | TRISA                                      | 85h        | TOR                                        | 105h | TOK                                        | 185 |

| PORTB                                      | 06h | TRISA                                      | 86h        | PORTB                                      | 106h | TRISB                                      | 186 |

| PORTC                                      | 07h | TRISE                                      | 87h        | TORTB                                      | 107h | INIOD                                      | 187 |

| PORTD (1)                                  | 08h | TRISC <sup>(1)</sup>                       | 88h        |                                            | 108h |                                            | 188 |

| PORTE <sup>(1)</sup>                       | 09h | TRISE (1)                                  | 89h        |                                            | 109h |                                            | 189 |

| PCLATH                                     | 0Ah | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah | PCLATH                                     | 18/ |

| INTCON                                     | 0Bh | INTCON                                     | 8Bh        | INTCON                                     | 10Bh | INTCON                                     | 18  |

| PIR1                                       | 0Ch | PIE1                                       | 8Ch        | EEDATA                                     | 10Ch | EECON1                                     | 180 |

| PIR2                                       | 0Dh | PIE1<br>PIE2                               | 8Dh        | EEADR                                      | 10Dh | EECON2                                     | 180 |

| TMR1L                                      | 0Eh | PCON                                       | 8Eh        | EEDATH                                     | 10Eh | Reserved <sup>(2)</sup>                    | 18  |

| TMR1H                                      | 0Fh | 1001                                       | 8Fh        | EEADRH                                     | 10Eh | Reserved <sup>(2)</sup>                    | 18F |

| T1CON                                      | 10h |                                            | 90h        | 22/18/11                                   | 110h | Received                                   | 190 |

| TMR2                                       | 11h | SSPCON2                                    | 91h        |                                            | 111h |                                            | 191 |

| T2CON                                      | 12h | PR2                                        | 92h        |                                            | 112h |                                            | 192 |

| SSPBUF                                     | 13h | SSPADD                                     | 93h        |                                            | 113h |                                            | 193 |

| SSPCON                                     | 14h | SSPSTAT                                    | 94h        |                                            | 114h |                                            | 194 |

| CCPR1L                                     | 15h | 00101/1                                    | 95h        |                                            | 115h |                                            | 195 |

| CCPR1H                                     | 16h |                                            | 96h        |                                            | 116h |                                            | 196 |

| CCP1CON                                    | 17h |                                            | 97h        | General                                    | 117h | General                                    | 197 |

| RCSTA                                      | 18h | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h | Purpose<br>Register                        | 198 |

| TXREG                                      | 19h | SPBRG                                      | 99h        | 16 Bytes                                   | 119h | 16 Bytes                                   | 199 |

| RCREG                                      | 1Ah | or bitte                                   | 9Ah        | ,                                          | 11Ah | ,                                          | 19A |

| CCPR2L                                     | 1Bh |                                            | 9Bh        |                                            | 11Bh |                                            | 19E |

| CCPR2H                                     | 1Ch |                                            | 9Ch        |                                            | 11Ch |                                            | 190 |

| CCP2CON                                    | 1Dh |                                            | 9Dh        |                                            | 11Dh |                                            | 19[ |

| ADRESH                                     | 1Eh | ADRESL                                     | 9Eh        |                                            | 11Eh |                                            | 19E |

| ADCON0                                     | 1Fh | ADCON1                                     | 9Fh        |                                            | 11Fh |                                            | 19F |

|                                            | 20h |                                            | A0h        |                                            | 120h |                                            | 1A( |

| General<br>Purpose<br>Register<br>96 Bytes |     | General<br>Purpose<br>Register<br>80 Bytes | EFh        | General<br>Purpose<br>Register<br>80 Bytes | 16Fh | General<br>Purpose<br>Register<br>80 Bytes | 1EF |

|                                            | 7Fh | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h | accesses<br>70h - 7Fh                      | 1FC |

| Bank 0                                     |     | Bank 1                                     |            | Bank 2                                     |      | Bank 3                                     |     |

| _                                          |     | ta memory location                         | ns, read   |                                            |      |                                            |     |

© 1999 Microchip Technology Inc.

## **TXSTA:** Trans. Status and Control Register

### PIC16F87X

#### 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, serial EEPROMs etc.

Г

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

| R/W-0<br>CSRC | R/W-0<br>TX9                                                                   | R/W-0<br>TXEN                    | R/W-0<br>SYNC | U-0       | R/W-0<br>BRGH | R-1<br>TRMT | R/W-0<br>TX9D | R = Readable bit                                                                      |

|---------------|--------------------------------------------------------------------------------|----------------------------------|---------------|-----------|---------------|-------------|---------------|---------------------------------------------------------------------------------------|

| bit7          | 17.9                                                                           | TALIN                            | 51110         |           | BROTT         |             | bit0          | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:        | CSRC: Clo<br>Asynchron<br>Don't care<br>Synchrono<br>1 = Master<br>0 = Slave r | ous mode<br>us mode<br>mode (Clo | ock generat   |           |               | G)          |               |                                                                                       |

| bit 6:        | <b>TX9</b> : 9-bit <sup>1</sup><br>1 = Selects<br>0 = Selects                  | s 9-bit trans                    | smission      |           |               |             |               |                                                                                       |

| bit 5:        | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br><b>Note:</b> SRE             | nit enabled<br>nit disabled      |               | (EN in SY | NC mode.      |             |               |                                                                                       |

| bit 4:        | SYNC: US<br>1 = Synchr<br>0 = Asynch                                           | onous mo                         | de            |           |               |             |               |                                                                                       |

| bit 3:        | Unimplem                                                                       | ented: Re                        | ad as '0'     |           |               |             |               |                                                                                       |

| bit 2:        | BRGH: Hig<br>Asynchron<br>1 = High sp                                          | ous mode                         | ate Select b  | it        |               |             |               |                                                                                       |

|               | 0 = Low sp<br>Synchrono<br>Unused in                                           | us mode                          |               |           |               |             |               |                                                                                       |

| bit 1:        | <b>TRMT</b> : Tra<br>1 = TSR er<br>0 = TSR fu                                  | mpty                             | Register S    | tatus bit |               |             |               |                                                                                       |

| bit 0:        | <b>TX9D:</b> 9th                                                               |                                  |               |           |               |             |               |                                                                                       |

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

<sup>© 1999</sup> Microchip Technology Inc.

REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                                                                                         | R/W-0                                                                                | R/W-0                                   | R/W-0               | R-0        | R-0          | R-x         |                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|---------------------|------------|--------------|-------------|----------------------------------------------------------------------------------------------------------------------|

| SPEN   | RX9                                                                                                                           | SREN                                                                                 | CREN                                    | ADDEN               | FERR       | OERR         | RX9D        | R = Readable bit                                                                                                     |

| bit7   |                                                                                                                               |                                                                                      | -                                       |                     |            | -            | bit0        | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7: | SPEN: Ser<br>1 = Serial p<br>0 = Serial p                                                                                     | ort enable                                                                           | d (Configu                              | ires RC7/R          | X/DT and   | RC6/TX/CI    | K pins as s | erial port pins)                                                                                                     |

| bit 6: | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                                                                            | 9-bit rece                                                                           | otion                                   |                     |            |              |             |                                                                                                                      |

| bit 5: | SREN: Sing<br>Asynchrono<br>Don't care<br>Synchrono<br>1 = Enable<br>0 = Disable<br>This bit is c<br>Synchrono<br>Unused in t | us mode -<br>us mode -<br>s single red<br>s single red<br>leared afte<br>us mode - s | master<br>ceive<br>ceive<br>r reception |                     | te.        |              |             |                                                                                                                      |

| bit 4: | <b>CREN</b> : Cor<br>Asynchrono<br>1 = Enable<br>0 = Disable<br>Synchrono<br>1 = Enable<br>0 = Disable                        | ous mode<br>s continuou<br>es continuo<br>us mode<br>s continuou                     | us receive<br>us receive<br>us receive  | until enable        | e bit CREN | l is cleared | (CREN ov    | rerrides SREN)                                                                                                       |

| bit 3: |                                                                                                                               | ous mode s<br>s address o                                                            | 9-bit (RX9<br>detection,                | = 1)<br>enable inte |            |              |             | ffer when RSR<8> is set<br>used as parity bit                                                                        |

| bit 2: | FERR: Fran<br>1 = Framing<br>0 = No fran                                                                                      | g error (Ca                                                                          |                                         | ted by read         | ling RCRE  | G register   | and receive | e next valid byte)                                                                                                   |

| bit 1: | <b>OERR</b> : Ove<br>1 = Overrue<br>0 = No ove                                                                                | n error (Ca                                                                          |                                         | ed by clear         | ing bit CR | EN)          |             |                                                                                                                      |

| bit 0: | RX9D: 9th                                                                                                                     | hit of recei                                                                         | ) etch hav                              | Can be nar          | ity bit)   |              |             |                                                                                                                      |

# **Baud Rate Generator**

- Clock rate for 16F877 is 4MHz

- Transmit/receive rate may vary (9600 bps, 19200 bps, etc)

- Need to scale system clock

Table 10-1 of 16F877 data sheet.

- -X is 8 bit SPBRG value

- $\star$  located at addres 99h

- BRGH value located in TXSTA

| TABLE               | E 10-3: | BAUI       | ORATES                      | FOR A   | SYNCH      | IRONOU                      | S MOD         | E (BRG     | H = 0)                      |  |

|---------------------|---------|------------|-----------------------------|---------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| DAUD                | F       | osc = 20 N | IHz                         | F       | osc = 16 N | 1Hz                         | Fosc = 10 MHz |            |                             |  |

| BAUD<br>RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | -       | -          | -                           | -       | -          | -                           | -             | -          | -                           |  |

| 1.2                 | 1.221   | 1.75       | 255                         | 1.202   | 0.17       | 207                         | 1.202         | 0.17       | 129                         |  |

| 2.4                 | 2.404   | 0.17       | 129                         | 2.404   | 0.17       | 103                         | 2.404         | 0.17       | 64                          |  |

| 9.6                 | 9.766   | 1.73       | 31                          | 9.615   | 0.16       | 25                          | 9.766         | 1.73       | 15                          |  |

| 19.2                | 19.531  | 1.72       | 15                          | 19.231  | 0.16       | 12                          | 19.531        | 1.72       | 7                           |  |

| 28.8                | 31.250  | 8.51       | 9                           | 27.778  | 3.55       | 8                           | 31.250        | 8.51       | 4                           |  |

| 33.6                | 34.722  | 3.34       | 8                           | 35.714  | 6.29       | 6                           | 31.250        | 6.99       | 4                           |  |

| 57.6                | 62.500  | 8.51       | 4                           | 62.500  | 8.51       | 3                           | 52.083        | 9.58       | 2                           |  |

| HIGH                | 1.221   | -          | 255                         | 0.977   | -          | 255                         | 0.610         | -          | 255                         |  |

| LOW                 | 312.500 | -          | 0                           | 250.000 | -          | 0                           | 156.250       | -          | 0                           |  |

| BAUD        |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|-------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | 0.300  | 0          | 207                         | 0.301             | 0.33       | 185                         |  |  |

| 1.2         | 1.202  | 0.17       | 51                          | 1.216             | 1.33       | 46                          |  |  |

| 2.4         | 2.404  | 0.17       | 25                          | 2.432             | 1.33       | 22                          |  |  |

| 9.6         | 8.929  | 6.99       | 6                           | 9.322             | 2.90       | 5                           |  |  |

| 19.2        | 20.833 | 8.51       | 2                           | 18.643            | 2.90       | 2                           |  |  |

| 28.8        | 31.250 | 8.51       | 1                           | -                 | -          | -                           |  |  |

| 33.6        | -      | -          | -                           | -                 | -          | -                           |  |  |

| 57.6        | 62.500 | 8.51       | 0                           | 55.930            | 2.90       | 0                           |  |  |

| HIGH        | 0.244  | -          | 255                         | 0.218             | -          | 255                         |  |  |

| LOW         | 62.500 | -          | 0                           | 55.930            | -          | 0                           |  |  |

| TABLE 10-4 | . DAUD KAILS | TOR ASTNCIRONOUS | WODE (BROIT = T) |

|------------|--------------|------------------|------------------|

|            |              | FOR ASYNCHRONOUS |                  |

| II (DEE             | - 10 4.          | BACOB        | 101120                      |                  |              |                             | MODE (  |            | ,                           |

|---------------------|------------------|--------------|-----------------------------|------------------|--------------|-----------------------------|---------|------------|-----------------------------|

| BAUD                | F                | osc = 20 M   | Hz                          | Fo               | osc = 16 M   | Hz                          | F       | osc = 10 M | Hz                          |

| RATE<br>(K)         | KBAUD            | %<br>ERROR   | SPBRG<br>value<br>(decimal) | KBAUD            | %<br>ERROR   | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | -                | -            | -                           | -                | -            | -                           | -       | -          | -                           |

| 1.2                 | -                | -            | -                           | -                | -            | -                           | -       | -          | -                           |

| 2.4                 | -                | -            | -                           | -                | -            | -                           | 2.441   | 1.71       | 255                         |

| 9.6                 | 9.615            | 0.16         | 129                         | 9.615            | 0.16         | 103                         | 9.615   | 0.16       | 64                          |

| 19.2                | 19.231           | 0.16         | 64                          | 19.231           | 0.16         | 51                          | 19.531  | 1.72       | 31                          |

| 28.8                | 29.070           | 0.94         | 42                          | 29.412           | 2.13         | 33                          | 28.409  | 1.36       | 21                          |

| 33.6                | 33.784           | 0.55         | 36                          | 33.333           | 0.79         | 29                          | 32.895  | 2.10       | 18                          |

| 57.6                | 59.524           | 3.34         | 20                          | 58.824           | 2.13         | 16                          | 56.818  | 1.36       | 10                          |

| HIGH                | 4.883            | -            | 255                         | 3.906            | -            | 255                         | 2.441   | -          | 255                         |

| LOW                 | 1250.000         |              | 0                           | 1000.000         |              | 0                           | 625.000 |            | 0                           |

| DAUD                | F                | osc = 4 MI   | Hz                          | Fos              | c = 3.6864   | MHz                         |         |            |                             |

| BAUD<br>RATE<br>(K) | KBAUD            | %<br>ERROR   | SPBRG<br>value<br>(decimal) | KBAUD            | %<br>ERROR   | SPBRG<br>value<br>(decimal) |         |            |                             |

| 0.3                 | -                | -            | -                           | -                | -            | -                           |         |            |                             |

| 1.2                 | 1.202            | 0.17         | 207                         | 1.203            | 0.25         | 185                         |         |            |                             |

| 2.4                 | 2.404            | 0.17         | 103                         | 2.406            | 0.25         | 92                          |         |            |                             |

| 9.6                 | 9.615            | 0.16         | 25                          | 9.727            | 1.32         | 22                          |         |            |                             |

|                     |                  |              |                             |                  |              |                             |         |            |                             |

| 19.2                | 19.231           | 0.16         | 12                          | 18.643           | 2.90         | 11                          |         |            |                             |

| 19.2<br>28.8        | 19.231<br>27.798 | 0.16<br>3.55 | 12<br>8                     | 18.643<br>27.965 | 2.90<br>2.90 | 11<br>7                     |         |            |                             |

|                     |                  |              |                             |                  |              |                             |         |            |                             |

| 28.8                | 27.798           | 3.55         | 8                           | 27.965           | 2.90         | 7                           |         |            |                             |

| 28.8<br>33.6        | 27.798<br>35.714 | 3.55<br>6.29 | 8<br>6                      | 27.965<br>31.960 | 2.90<br>4.88 | 7<br>6                      |         |            |                             |

DS30292B-page 98

© 1999 Microchip Technology Inc.

PIR1 REGISTER 2.2.2.5

The PIR1 register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                | R/W-0                                                                                                                                                                                                                                   | R-0          | R-0                            | R/W-0                        | R/W-0                        | R/W-0           | R/W-0       |                                             |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------|------------------------------|------------------------------|-----------------|-------------|---------------------------------------------|--|--|--|--|

| PSPIF <sup>(1)</sup> | ADIF                                                                                                                                                                                                                                    | RCIF         | TXIF                           | SSPIF                        | CCP1IF                       | TMR2IF          | TMR1IF      | R = Readable bit                            |  |  |  |  |

| bit7                 |                                                                                                                                                                                                                                         |              |                                |                              |                              |                 | bit0        | W = Writable bit<br>- n= Value at POR reset |  |  |  |  |

| bit 7:               | PSPIF <sup>(1)</sup> :                                                                                                                                                                                                                  | Parallel Sla | ve Port Re                     | ad/Write Int                 | errupt Flag b                | it              |             |                                             |  |  |  |  |

|                      | 1 = A read                                                                                                                                                                                                                              | or a write   | operation h                    | nas taken pla                | ace (must be                 |                 | oftware)    |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | has occurre                    |                              |                              |                 |             |                                             |  |  |  |  |

| bit 6:               |                                                                                                                                                                                                                                         |              | Interrupt F<br>n complete      | 0                            |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | on is not co                   |                              |                              |                 |             |                                             |  |  |  |  |

| bit 5:               | RCIF: USA                                                                                                                                                                                                                               | ART Receiv   | /e Interrupt                   | Flag bit                     |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | ive buffer is                  |                              |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | ive buffer is                  |                              |                              |                 |             |                                             |  |  |  |  |

| bit 4:               |                                                                                                                                                                                                                                         |              | nit Interrupt<br>smit buffer i |                              |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | smit buffer i                  |                              |                              |                 |             |                                             |  |  |  |  |

| bit 7:               |                                                                                                                                                                                                                                         |              |                                | (SSP) Inter                  |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              |                                | has occurre<br>will set this |                              | be cleared in   | software be | fore returning from the interrupt ser-      |  |  |  |  |

|                      | SPI                                                                                                                                                                                                                                     | e. The con   | ditions that                   | will set this                | bit are:                     |                 |             |                                             |  |  |  |  |

|                      | A transmis                                                                                                                                                                                                                              | sion/recep   | tion has tal                   | ken place.                   |                              |                 |             |                                             |  |  |  |  |

|                      | I <sup>2</sup> C Slave                                                                                                                                                                                                                  | aion/racan   | tion has tal                   |                              |                              |                 |             |                                             |  |  |  |  |

|                      | I <sup>2</sup> C Master                                                                                                                                                                                                                 |              | แบท กลร เล                     | ten place.                   |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | tion has tal                   |                              |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              |                                |                              | by the SSP n                 |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              |                                |                              | by the SSP m<br>d by the SSP |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              |                                |                              |                              |                 | ule.        |                                             |  |  |  |  |

|                      | The initiated acknowledge condition was completed by the SSP module.<br>A start condition occurred while the SSP module was idle (Multimaster system).<br>A stop condition occurred while the SSP module was idle (Multimaster system). |              |                                |                              |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              |                                | the SSP mo<br>has occurred   |                              | e (iviuitimaste | er system). |                                             |  |  |  |  |

| bit 2:               |                                                                                                                                                                                                                                         | •            | upt Flag bi                    |                              |                              |                 |             |                                             |  |  |  |  |

|                      | Capture M                                                                                                                                                                                                                               | ode          |                                |                              |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              |                                |                              | t be cleared i               | in software)    |             |                                             |  |  |  |  |

|                      | Compare I                                                                                                                                                                                                                               |              | r capture o                    | ccurrea                      |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | compare m                      | atch occurr                  | ed (must be                  | cleared in so   | ftware)     |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | r compare                      | match occu                   | rred                         |                 |             |                                             |  |  |  |  |

|                      | PWM Mod<br>Unused in                                                                                                                                                                                                                    |              |                                |                              |                              |                 |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | R2 Match Ir                    | terrupt Flag                 | bit                          |                 |             |                                             |  |  |  |  |

|                      | 1 = TMR2                                                                                                                                                                                                                                | to PR2 ma    | tch occurre                    | ed (must be                  | cleared in sc                | oftware)        |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | match occ                      |                              |                              |                 |             |                                             |  |  |  |  |

| bit 0:               |                                                                                                                                                                                                                                         |              | flow Interru                   |                              | rad in active                | (10)            |             |                                             |  |  |  |  |

|                      |                                                                                                                                                                                                                                         |              | d not overfl                   |                              | red in softwa                | iie)            |             |                                             |  |  |  |  |

|                      | PSPIF is r                                                                                                                                                                                                                              |              |                                |                              |                              |                 |             |                                             |  |  |  |  |

DS30292B-page 22

© 1999 Microchip Technology Inc.

Figure 10-1 of 16F877 data sheet.

- Initialize baud rate generator

- Configure TXSTA (mode, # bits, etc)

- Check bit 4 in PIR1 to see if transmit buffer is empty

- When buffer empty, send value to TXREG address (19h)

Figure 10-4 of 16F877 data sheet.

- Initialize baud rate generator

- Configure RCSTA (port enable, # bits, etc)

- Check bit 5 in PIR1 to see if receive buffer is full

- When buffer full, get value from RCREG address (1Ah)

Figure 11-7 in Peatman book.

- MAX232 drivers convert between 5/10V.

- -2 wires needed for terminal connection.

- Port A should be configured as data input

- -4 switches attached to lower bits of port A

- Port B should be configured as data output

- 4 LEDs connected to port B (RB1-RB4)

- Observe code on page 29 of data sheet for detailed discussion

- Register ADCON1 described on page 112 of 16F877 data sheet

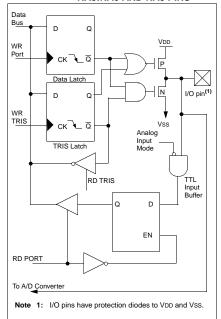

#### 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a hi-impedance mode). Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

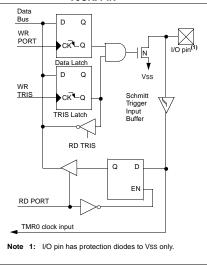

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ;                  |       |

|-------|---------|-----|--------------------|-------|

| BCF   | STATUS, | RP1 | ; Bank0            |       |

| CLRF  | PORTA   |     | ; Initialize PORTA | by    |

|       |         |     | ; clearing output  |       |

|       |         |     | ; data latches     |       |

| BSF   | STATUS, | RP0 | ; Select Bank 1    |       |

| MOVLW | 0x06    |     | ; Configure all pi | ns    |

| MOVWF | ADCON1  |     | ; as digital input | s     |

| MOVLW | 0xCF    |     | ; Value used to    |       |

|       |         |     | ; initialize data  |       |

|       |         |     | ; direction        |       |

| MOVWF | TRISA   |     | ; Set RA<3:0> as i | nputs |

|       |         |     | ; RA<5:4> as outpu | its   |

|       |         |     | ; TRISA<7:6> are a | lways |

|       |         |     | ; read as '0'.     |       |

|       |         |     |                    |       |

### PIC16F87X

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

#### FIGURE 3-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

© 1999 Microchip Technology Inc.

### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| J-0<br>DFM<br>bit7      | -                         | _                                        | -                                    |             | /W-0<br>CFG3                           | R/W-0<br>PCFG2 | R/W<br>PCF | 1          | PCFG0<br>bit0 | W = W<br>U = Ur | eadable bit<br>ritable bit<br>nimplemented b<br>ad as '0' |

|-------------------------|---------------------------|------------------------------------------|--------------------------------------|-------------|----------------------------------------|----------------|------------|------------|---------------|-----------------|-----------------------------------------------------------|

| 1<br>0<br>6-4: <b>U</b> | = Left Ju<br>nimpleme     | ustified. 6<br>stified. 6 I<br>ented: Re | most sigr<br>east signi<br>ad as '0' | nificant bi | ts of ADRI<br>s of ADRE<br>n Control b | SL are rea     |            |            |               | - n = Va        | alue at POR res                                           |

| PCFG3:<br>PCFG0         | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1                | AN5 <sup>(1)</sup><br>RE0            | AN4<br>RA5  | AN3<br>RA3                             | AN2<br>RA2     | AN1<br>RA1 | AN0<br>RA0 | VREF+         | VREF-           | Chan /<br>Refs <sup>(2)</sup>                             |

| 0000                    | А                         | А                                        | А                                    | А           | Α                                      | А              | А          | А          | Vdd           | Vss             | 8/0                                                       |

| 0001                    | A                         | А                                        | А                                    | А           | VREF+                                  | А              | А          | А          | RA3           | Vss             | 7/1                                                       |

| 0010                    | D                         | D                                        | D                                    | Α           | A                                      | А              | А          | А          | Vdd           | Vss             | 5/0                                                       |

| 0011                    | D                         | D                                        | D                                    | Α           | VREF+                                  | А              | А          | А          | RA3           | Vss             | 4/1                                                       |

| 0100                    | D                         | D                                        | D                                    | D           | A                                      | D              | А          | A          | VDD           | Vss             | 3/0                                                       |

| 0101                    | D                         | D                                        | D                                    | D           | VREF+                                  | D              | А          | А          | RA3           | Vss             | 2/1                                                       |

| 011x                    | D                         | D                                        | D                                    | D           | D                                      | D              | D          | D          | VDD           | Vss             | 0/0                                                       |

| 1000                    | Α                         | A                                        | А                                    | Α           | VREF+                                  | VREF-          | А          | А          | RA3           | RA2             | 6/2                                                       |

| 1001                    | D                         | D                                        | А                                    | Α           | A                                      | А              | А          | Α          | VDD           | Vss             | 6/0                                                       |

| 1010                    | D                         | D                                        | А                                    | Α           | VREF+                                  | Α              | Α          | А          | RA3           | Vss             | 5/1                                                       |

| 1011                    | D                         | D                                        | А                                    | Α           | VREF+                                  | VREF-          | Α          | А          | RA3           | RA2             | 4/2                                                       |

| 1100                    | D                         | D                                        | D                                    | А           | VREF+                                  | VREF-          | А          | А          | RA3           | RA2             | 3/2                                                       |

| 1101                    | D                         | D                                        | D                                    | D           | VREF+                                  | VREF-          | А          | А          | RA3           | RA2             | 2/2                                                       |

| 1110                    | D                         | D                                        | D                                    | D           | D                                      | D              | D          | А          | Vdd           | Vss             | 1/0                                                       |

| 1111                    | D                         | D                                        | D                                    | D           | VREF+                                  | VREF-          | D          | А          | RA3           | RA2             | 1/2                                                       |

|                         | I/O<br>These cha          |                                          |                                      |             | he 28-pin                              |                | ilabla aa  | A/D innu   | to and the    | numor of a      | analog channels                                           |

DS30292B-page 112

© 1999 Microchip Technology Inc.

- Send prompt to terminal

- Wait for affirmative response

- Read 4 bit value from port A

- Write value to port B

- Check if value in switches changed

- If yes, send changed value to terminal.

- If no, keep checking.

# Reading

- Data sheet 29-33 port  $\mathrm{I}/\mathrm{O}$

- Data sheet 112 ADCON1

- Data sheet 95-104 UART

- Peatman, chapter 11 UART

- MAX232 data sheet

- Try assembling a small program first to write a value to the LEDs

- Program 16F877 to read from port A, write to port B

- Program 16F877 to print a message to terminal.

- Try reading in a character and then echoing to the terminal

- Combine the code segments to complete the lab.

- Test code BEFORE coming to Lab

- Make sure switches and LEDS working correctly

- Make good use of lab time

- Take an incremental approach to design and test.

- Report hardware problems to TAs, lab staff

- Write down report of issues problems so you won't forget

- I/TA will ask questions and review hardware/code

- Report should contain the following:

- $\star$  Introduction

- \* Lab overview

- \* Hardware schematic (including all chips, connections and pin numbers)

- $\star$  Brief discussion of code

- $\star$  Full, well-commented code

- \* Discussion of problems encountered (each student)

- \* Full reference list (including data sheets).