# **ENGIN 112**

# Intro to Electrical and Computer Engineering

Lecture 28

# Timing Analysis

#### **Overview**

- Circuits do not respond instantaneously to input changes

- Predictable delay in transferring inputs to outputs

- Propagation delay

- ° Sequential circuits require a periodic clock

- Goal: analyze clock circuit to determine maximum clock frequency

- Requires analysis of paths from flip-flop outputs to flip-flop inputs

- Even after inputs change, output signal of circuit maintains original output for short time

- Contamination delay

# **Sequential Circuits**

- Sequential circuits can contain both combinational logic and edge-triggered flip flops

- A clock signal determines when data is stored in flip flops

- ° Goal: How fast can the circuit operate?

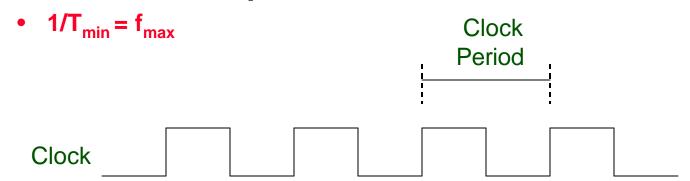

- Minimum clock period: T<sub>min</sub>

- Maximum clock frequency: f<sub>max</sub>

- Maximum clock frequency is the inverse of the minimum clock period

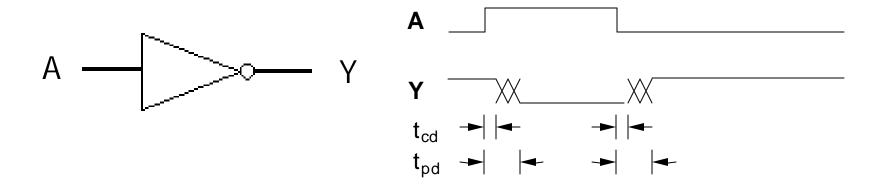

### **Combinational Logic Timing: Inverter**

- ° Combinational logic is made from electronic circuits

- An input change takes time to propagate to the output

- ° The output remains unchanged for a time period equal to the contamination delay, t<sub>cd</sub>

- ° The new output value is guaranteed to valid after a time period equal to the propagation delay, tpd

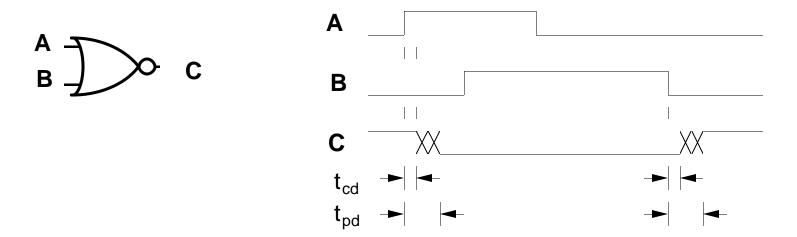

### **Combinational Logic Timing: XNOR Gate**

- The output is guaranteed to be stable with old value until the contamination delay

- Unknown values shown in waveforms as Xs

- The output is guaranteed to be stable with the new value after the propagation delay

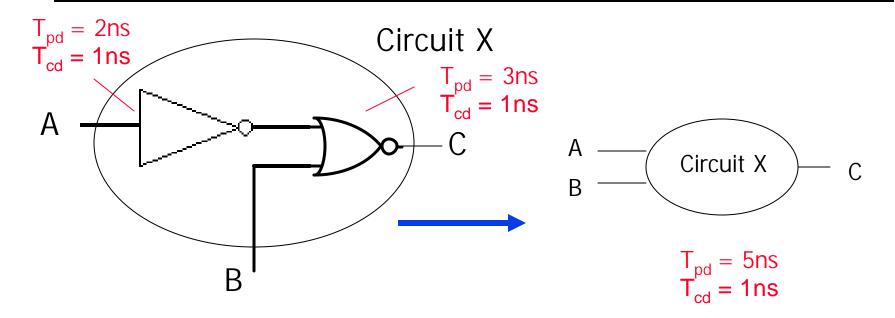

# **Combinational Logic Timing: complex circuits**

- Propagation delays are additive

- Locate the longest combination of t<sub>pd</sub>

- ° Contamination delays may not be additive

- Locate the shortest path of t<sub>cd</sub>

- Find propagation and contamination delay of new, combined circuit

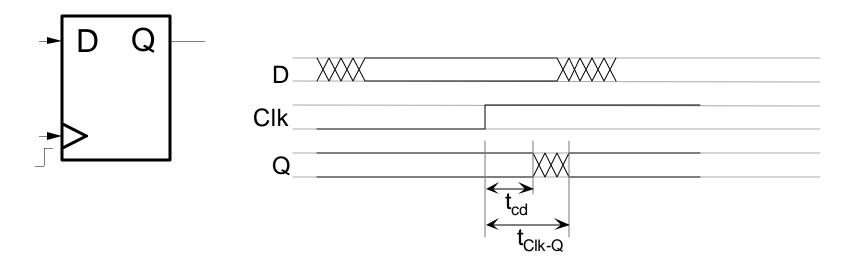

# **Clocked Device: Contamination and Propagation Delay**

- Timing parameters for clocked devices are specified in relation to the clock input (rising edge)

- Output unchanged for a time period equal to the contamination delay, t<sub>cd</sub> after the rising clock edge

- New output guaranteed valid after time equal to the propagation delay, t<sub>Clk-Q</sub>

- Follows rising clock edge

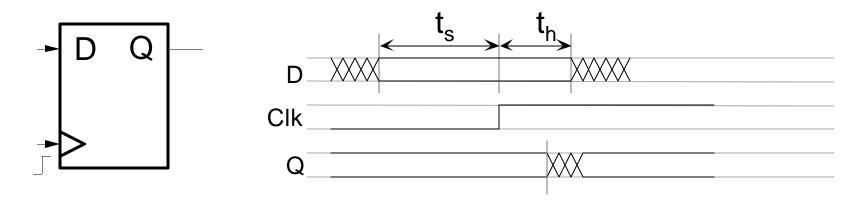

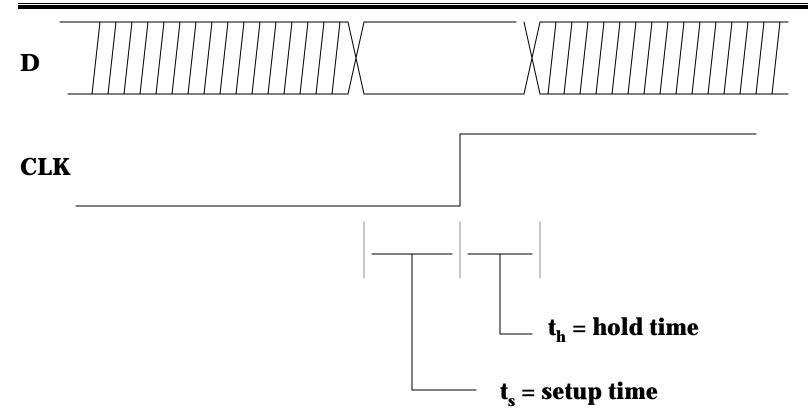

# **Clocked Devices: Setup and Hold Times**

- Timing parameters for clocked devices are specified in relation to the clock input (rising edge)

- D input must be valid at least t<sub>s</sub> (setup time) before the rising clock edge

- D input must be held steady t<sub>h</sub> (hold time) after rising clock edge

- Setup and hold are input restrictions

- Failure to meet restrictions causes circuit to operate incorrectly

# **Edge-Triggered Flip Flop Timing**

- The logic driving the flip flop must ensure that setup and hold are met

- Timing values (t<sub>cd</sub> t<sub>pd</sub> t<sub>Clk-Q</sub> t<sub>s</sub> t<sub>h</sub>)

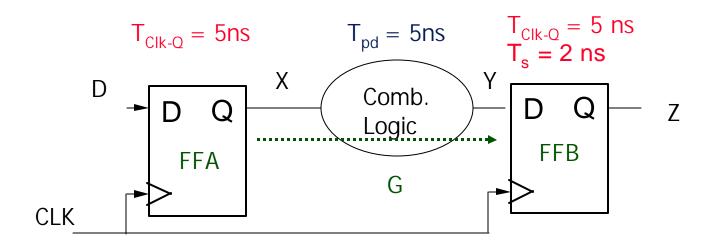

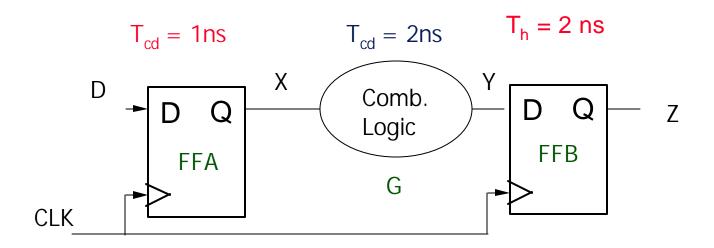

# **Analyzing Sequential Circuits**

- ° What is the minimum time between rising clock edges?

- $T_{min} = T_{CLK-Q} (FFA) + T_{pd} (G) + T_{s} (FFB)$

- Trace propagation delays from FFA to FFB

- o Draw the waveforms!

# **Analyzing Sequential Circuits**

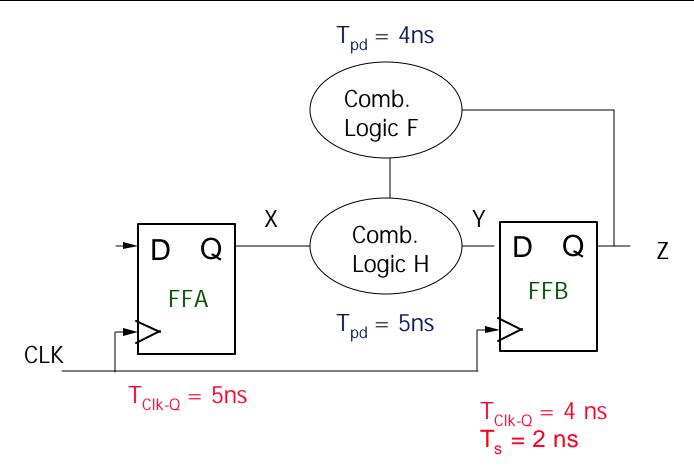

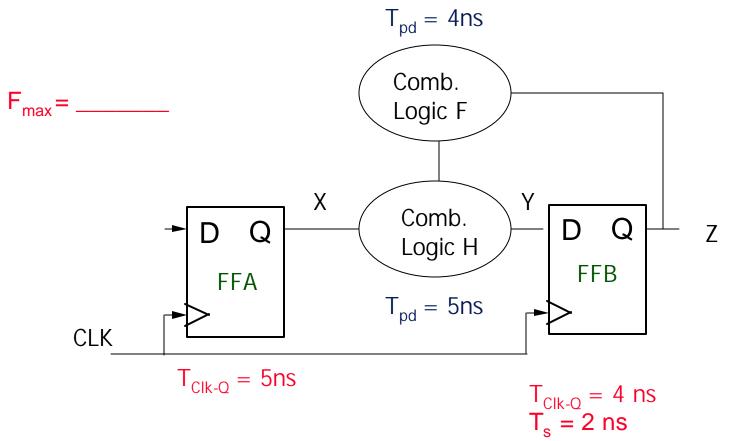

- ° What is the minimum clock period (T<sub>min</sub>) of this circuit? Hint: evaluate all FF to FF paths

- Maximum clock frequency is 1/T<sub>min</sub>

November 7, 2003

# **Analyzing Sequential Circuits**

### ° Path FFA to FFB

•

$$T_{Clk-Q}(FFA) + T_{pd}(H) + T_{s}(FFB) = 5ns + 5ns + 2ns = 12ns$$

### ° Path FFB to FFB

•

$$T_{CLK-Q}(FFB) + T_{pd}(F) + T_{pd}(H) + T_{s}(FFB) = 4ns + 4ns + 5ns + 2ns$$

# **Analyzing Sequential Circuits: Hold Time Violation**

- One more issue: make sure Y remains stable for hold time (T<sub>h</sub>) after rising clock edge

- Remember: contamination delay ensures signal doesn't change

- ° How long before first change arrives at Y?

- T<sub>cd</sub>(FFA) + T<sub>cd</sub>(G) >= T<sub>h</sub>

1ns + 2ns > 2ns

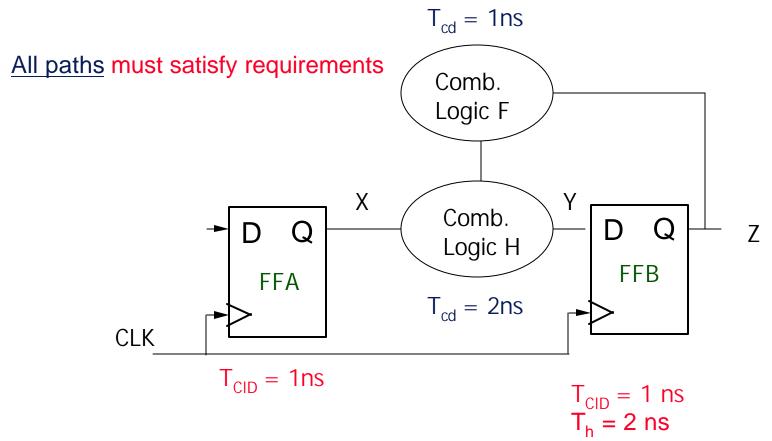

### **Analyzing Sequential Circuits: Hold Time Violations**

### ° Path FFA to FFB

•

$$T_{CD}(FFA) + T_{CD}(H) > T_h(FFB) = 1 \text{ ns} + 2 \text{ns} > 2 \text{ns}$$

### ° Path FFB to FFB

•

$$T_{CD}(FFB) + T_{CD}(F) + T_{Cd}(H) > T_h(FFB) = 1ns + 1ns + 2ns > 2ns$$

# **Summary**

- Maximum clock frequency is a fundamental parameter in sequential computer systems

- Possible to determined clock frequency from propagation delays and setup time

- ° The longest path determines the clock frequenct

- All flip-flop to flip-flop paths must be checked

- Hold time are satisfied by examining contamination delays

- The shortest contamination delay path determines if hold times are met

- ° Check handout for more details and examples.