# Canonical Graph-based Representations for Verification of Logic and Arithmetic Designs

Maciej Ciesielski

Department of Electrical and Computer Engineering University of Massachusetts, Amherst, MA 01003, USA

| Abusaleh M. Jabir            | Dhiraj K. Pradhan              |

|------------------------------|--------------------------------|

| School of Technology         | Department of Computer Science |

| Oxford Brookes University    | University of Bristol          |

| Oxford OX33 1HX, UK          | Bristol BS8 1UB, UK            |

| E-mail: ajabir@brookes.ac.uk | E-mail: pradhan@cs.bris.ac.uk  |

**Index Terms:** *Decision Diagrams, Canonical Representations, Word-level Diagrams, Galois Fields, Verification.*

#### Abstract

This chapter presents several canonical, graph-based representations used in design and verification of logic and arithmetic circuits on different levels of abstraction. In particular, canonical diagram representations are described for Boolean, word-level, integer, and finite field multiple-output functions. They include Binary Decision Diagrams (BDDs), a number of Word-Level Decision Diagrams (WDDs), Binary Moment Diagrams (BMDs), Taylor Expansion Diagrams (TEDs), and Finite Field Decision Diagrams (FFDDs).

All these diagrams are canonical and minimal with respect to a fixed variable order of their input variables. As such, they support equivalence verification of two combinational designs by checking isomorphism of their graph representations. While BDDs have been used extensively in representing and verifying bit-level designs, such as control and random logic, several WDDs and BMDs find important applications in verifying arithmetic designs with bit-level inputs and integer outputs. TEDs and FFDDs further extend these forms by allowing inputs and outputs to take integer or multiple (finite-field) values. Of particular interest is application of these structures to verification of designs with significant arithmetic component. These computations can often be expressed as multi-variate polynomials and require efficient abstract models for their representation.

## **1** Introduction

Having matured over the years, formal design verification methods, such as theorem proving, property and model checking, and equivalence checking, have found increasing application in industry. Canonical graph-based representations, such as Binary Decision Diagrams (BDDs) [1], Binary Moment Diagrams (BMDs) [2] and their variants, play an important role in the development of sofware tools for verification. While these techniques are quite mature at the structural level, the high-level verification models are only now being developed. The main difficulty is caused by the fact that such verification must span several levels of design abstraction. Verification of arithmetic designs is particularly difficult because of the disparity in the representations on the different levels and the complexity of logic involved.

This chapter addresses verification based on canonical data structures. It presents several canonical, graph-based representations that are used in formal verification, and in particular in equivalence checking of combinational designs specified at different levels of abstraction. These representations are commonly known under the term "decision diagrams", even though not all of them are actually decision-based forms. They are graph-based structures whose nodes represent the variables and the directed edges represent the result of the decomposition of the function with respect to the individual variables. Particular attention is given to arithmetic and word-level representations.

An important common feature of all these representations is canonicity, which is essential in combinational equivalence checking. A form is canonical if representation of a function in that form is unique. Canonical graph-based representations make it possible to check if two combinational functions are equivalent by checking if their graph-based representations are isomorphic. Checking for isomorphism can be done in constant time, once the representation has been constructed, by testing if the two functions share the same root of the diagram.

The canonical diagrams can be fully characterized by the following basic properties, described in details in this chapter:

- 1. **Decomposition principle**, which defines the type of function that can be modeled by the diagram and the underlying decomposition method. They include binary decomposition for Boolean functions; some form of multi-valued decomposition for integer-valued functions; and moment decomposition or other non-binary expansions for arithmetic functions.

- 2. **Simplification rules** that make the diagram minimal and irredundant, hence canonical. Different rules apply to different types of diagrams.

- 3. Composition algorithms, which, given graph-based representations for functions F and G, specify how to construct a similar representation for function F < op > G, where < op > represents an arbitrary operation defined for the given application domain (Boolean, arithmetic, finite field, etc). The composition algorithms, commonly known as APPLY algorithms, recursively apply the given operation < op > to the decomposed functions, depending on the type of functions and operations allowed.

One of the most known and commonly used canonical diagram representation is Binary Decision Diagram (BDD) [1]. BDDs are based on the well known Shannon (or more accurately, Boole)

function expansion, which decomposes the function into two co-factors, f(x = 0) and f(x = 1). Each subgraph resulting from such a decomposition can be viewed as as a decision (x = 0 or x = 1) taken at a decomposing variable, justifying the name *decision diagram*. BDDs have been developed for Boolean functions and logic circuits represented at the bit level and used extensively in representing and verifying bit-level designs, such as control and random logic. Thanks to their compact, canonical form they truly revolutionized the field of combinational verification and logic synthesis and found applications to many other fields, such as satisfiability, testing and synthesis. However, because of their exponential worst-case size complexity, they have had limited success in modeling and verifying RTL designs with significant arithmetic component, especially with multipliers.

Another canonical form described in this chapter is a Binary Moment Diagram (BMD) [2], developed specifically for arithmetic functions. BMDs are based on a moment decomposition principle, which treats an arithmetic function as a linear function with Boolean inputs and integer (or real-valued) outputs. The two sub-functions resulting from the decomposition represent the two moments (constant and linear) of the function, rather than a "decision". For this reason BMDs do not technically belong to a category of decision diagrams but form a class of their own. BMDs find important applications in verifying arithmetic designs with bit-level inputs and integer outputs.

Two newer types of diagrams, called Taylor Expansion Diagram (TED) and Finite Field Decision Diagram (FFDD), have been recently introduced to address the need for a more abstract design representation, with inputs and outputs allowed to take either integer or discrete (finite-field) values. Both of these diagrams can be thought of as extensions of BDDs and BMDs, with inputs and outputs represented as symbolic variables. The two diagrams differ in arithmetic representation of the data (infinite precision integer vs finite field arithmetic) and the type of decomposition used (Taylor expansion vs multi-valued GF decomposition).

Taylor Expansion Diagram (TED) [3] is based on Taylor expansion of polynomial representation of the computation expressed in the design. Both inputs and outputs are treated as infinite precision integers (or real numbers) and are represented by symbolic variables. The power of abstraction, combined with canonicity and compactness makes the TED particularly attractive for verification of designs specified at the behavioral and algorithmic levels, such as datapaths and signal processing systems. Computations performed by those designs can often be expressed as polynomials and be efficiently represented with TEDs, with memory requirements several orders of magnitude smaller than those of other known representations. TEDs can also serve as a vehicle to transform the initial functional representation of the design into a structural representation in form of a data flow graph (DFG); as such they are applicable to behavioral synthesis, or, more specifically, to behavioral transformations which can also be used in verification.

Finite Field Decision Diagram (FFDD) [4] is an extension of multiple-terminal decision diagrams, but with inputs and outputs represented in finite field (also called Galois Field, GF) arithmetic rather than in the integer domain. Finite field representation has numerous applications in cryptography, error control systems, fault tolerant designs, and digital signal processing. FFDD representation allows the simulation and verification of such systems to be performed more efficiently on a higher level of abstraction. The verification can be performed either at the bit or the word-level; it is not restricted to word boundaries and can be used to model and verify any combination of output bits.

### **2** Decision Diagrams

Binary Decision Diagrams (BDD) have emerged as representation of choice for many applications, ranging from representation of Boolean function, to verification and satisfiability, to logic synthesis. Even though BDDs (albeit under different name) have been known since late 1950s it was the seminal work of Bryant [1] that brought to light their importance as canonical representations for Boolean logic. This section briefly reviews basic theory and algorithms for BDDs, taken from multiple sources [1,5–7].

#### 2.1 Binary Decision Diagrams (BDD)

A binary decision diagram is a graph-based data structure, which represents a set of binary-valued decisions, culminating at the overall decision that can be either true or false. Specifically, BDD is a directed acyclic graph (DAG) whose nodes represent the decisions, and edges represent the decision types (true or false). The final decision evaluated at the root represents the overall function encoded by the BDD. Ordered and reduced BDD is irredundant and canonical, i.e., a representation of a function in that form is unique. Formally, BDD is defined as follows:

**Definition 2.1** A Binary Decision Diagram (BDD) is a rooted directed acyclic graph G(V, E) with a set of nodes V and set of edges E. The vertex set V contains two types of vertices:

- Two terminal nodes (leaves), corresponding to constant 0 and 1.

- A set of variable nodes {u}, each associated with a Boolean variable v = var(u). Each node has exactly two out-going edges, pointing to two children functions, low(u) and high(u). (In the figures, the two children edges are represented as dotted and solid lines, respectively.)

The function of node  $u \in V$ , associated with variable v = var(u) is given by  $f^u = \overline{v} \cdot low(u) + v \cdot high(u)$ , where low(u) and high(u) are the functions of the low and high children of u, respectively. In particular, the function evaluated at the root represents the logic function encoded in the BDD.

The Decomposition Principle. The above definition basically states that BDD is based on a Shannon (Boole) expansion of function f, applied recursively to its variables. That is,

$$f^{u} = \bar{v} \cdot f_{\bar{v}} + v \cdot f_{v} \tag{1}$$

where  $f_{\bar{v}} = low(u)$  and  $f_v = high(u)$  are the negative and positive cofactors of f with respect to the decomposing variable v.

**Definition 2.2** A BDD is ordered (denoted OBDD) if on all paths from the root to its terminal nodes, the variables appear in the same linear order:  $x_1 < x_2 < ... < x_n$ . Furthermore, OBDD is reduced (denoted ROBDD) if it satisfies two properties:

1. (Irredundancy) No variable node u has identical low and high children, i.e.,  $low(u) \neq high(u)$ .

2. (Uniqueness) No two distinct nodes u and v have the same variable name and the same low and high children That is, var(u) = var(v), low(u) = low(v),  $high(u) = high(v) \Rightarrow u = v$

The above definition provide the *reduction rules* for BDDs: rule 1 removes redundant nodes with same low and high children; rule 2 merges isomorphic subgraphs. The resulting ROBDDs is an irredundant representation, i.e., no two nodes of the ROBDD represent the same Boolean function. Two ROBDDs are *isomorphic* if there is a one-to-one mapping between the vertex sets that preserves adjacency, indices and leaf values. Thus two isomorphic ROBDDs represent the same function. Conversely, two Boolean expressions that represent the same logic function have isomorphic ROBDDs for a given ordering of variables. In this sense ROBDDs are a canonical representation.

The following lemma, due to Bryant, states the canonicity of ROBDDs [1].

**Lemma 1** For any Boolean function f there is exactly one ROBDD with root node u and variable order  $x_1 < x_2 < ... < x_n$  such that  $f^u = f(x_1, x_2, ..., x_n)$ .

**BDD Construction.** An algorithm has been proposed by Bryant to reduce OBDD. The resulting diagram, ROBDD, is irredundant, minimal and canonical. The algorithm visits the OBDD bottom up, from the leaf nodes to the root, and labels each vertex  $v \in V$  with an identifier id(v). The reduction rules are then applied to remove redundant nodes and merge isomorphic subgraphs. As a result, an ROBDD is identified by a subset of vertices with different identifiers.

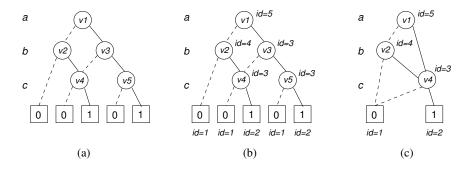

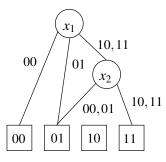

The algorithm is illustrated in Figure 1, taken from [5] for function f = (a+b)c. OBDD is constructed from the original expression, as shown in Figure 1(a). Then, the nodes of the OBDD are labeled with identifiers, as a function of the variable name and their children. First, the leaf nodes (0 and 1) are labeled with identifiers id = 1 and id = 2, respectively. Then the vertices  $v_4, v_5$  on the bottom most level, corresponding to variable c, are labeled with their identifiers. In this case both nodes are assigned the same identifier, id = 3, since they correspond to the same variable and have children with same identifiers. They are replaced by a single node,  $v_4$  (visited first), added to the ROBDD. Next, the algorithm visits vertices  $v_2, v_3$ , associated with variable b. Vertex  $v_2$  is assigned identifier id = 4 and is added to the ROBDD. The left (low) and right (high) children of node  $v_3$  have the same identifier, so  $v_3$  inherits their identifier and is discarded as redundant. Finally, the root  $v_1$ , associated with variable a is visited and assigned the identifier id = 5. It is added to the ROBDD as a unique node with this identifier. The resulting ROBDD is shown in Figure 1(c).

Figure 1: Construction of a ROBDD for f = (a+b)c: a) OBDD for the variable order a, b, c; b) OBDD with unique identifiers; c) ROBDD for variable order a, b, c.

In practice, ROBDDs are built directly from a Boolean formulae, avoiding the reduction step and possible memory overflow problems. This approach is based on applying the Shannon decomposition,  $f = \bar{v} \cdot f_{\bar{v}} + v \cdot f_{v}$ , iteratively to the variables of the formulae in the predetermined order. Canonicity and minimality of such constructed ROBDD are accomplished by using a hash table, called the *unique table*, which contains a key for each vertex of an ROBDD and which uniquely identifies the function associated with that node. The key is a triple, composed of the variable name and the identifiers of the low and high children. The unique table is constructed bottom up. When a new node is considered for addition to the ROBDD, a lookup in the table determines if another vertex in the table already implements the same functionality by comparing the keys. If this is the case, the pointer of the new node. This way, no redundant nodes are added to the table and the table represents an ROBDD. The run-time complexity of this and other ROBDD construction algorithms is  $O(2^n)$ , where *n* is the number of variables. Similarly, the size of the ROBDD is, in the worst case, exponential. The details of the construction of an ROBDD can be found in [1,5].

BDDs provide a compact representation of Boolean logic. Each path of the BDD from root to terminal node 1 represents a product term (on-set cube) of the function encoded in the BDD. It is computed as a product of variables, along the path, at their respective polarity. For example, for a BDD in Figure 1, a path  $\{v_1, v_2, v_4, 1\}$  corresponds to the product term  $\bar{a}bc$ . Logic function encoded in a BDD is then evaluated as a logical sum (OR) of products terms associated with the on-paths. Similarly, a path from root to terminal node 0 represents a complement of the function. This feature is useful for function complementation, which can be done in constant time by simply exchanging the 0 and 1 terminal nodes.

ROBDDs can naturally represent multiple-output functions by modeling them as ROBDDs with shared subgraphs. In the sequel, we will refer to ROBDD simply as BDD, since some ordering of the variables is always imposed on the BDD, and the OBDD must be reduced in order to be canonical.

**BDD Composition - The** APPLY **Algorithm.** Another way of constructing a BDD for a given Boolean expression is to compose BDDs of its subexpressions using Boolean connectives, like AND, OR, XOR, etc. The algorithm that performs such a composition is known as the APPLY algorithm.

The basic idea comes, again, from the recursive application of Shannon expansion theorem for arbitrary binary operator  $\langle op \rangle$ :

$$f < op > g = \bar{v}(f_{\bar{v}} < op > g_{\bar{v}}) + v(f_{v} < op > g_{v})$$

(2)

Starting with the top most variable v in the two functions the formula is applied recursively to all the variables in the order they appear in their respective BDDs (f and g must have compatible ordering for the algorithm to work). If v is the top variable of f and g, then the operator  $\langle op \rangle$  is applied to their respective cofactors. If f does not depend on v, then  $f_v = f_{\bar{v}} = f$  and the cofactor is the function itself. The worst case complexity of the APPLY algorithms is  $O(n_1n_2)$ , where  $n_1$  and  $n_2$  are the number of variables in the two BDDs.

Using the above algorithm, one can construct a BDD for an arbitrary Boolean network or a gatelevel netlist. First, a trivial BDD is build for the variables representing primary inputs, and then BDDs of each expression or logic gate are constructed from the BDDs of their immediate inputs, in the topological order, from primary inputs to primary outputs.

Operations on BDDs can be done in polynomial time of their size (number of nodes). However, the real complexity is hidden in their construction, which is expensive both in time and space. BDDs can be exponential in size and cause memory explosion, especially for designs containing arithmetic functions, such as multipliers (BDDs cannot be built for multipliers larger than  $16 \times 16$  bits).

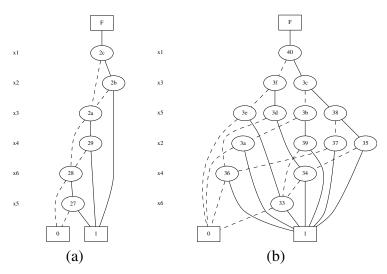

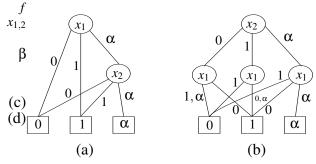

**Variable Ordering**. The size of a BDD strongly depends on the ordering of the variables. The size of the BDD (measured in the number of nodes) is, in the worst case, exponential in the number of variables. ROBDDs representing adder functions are particularly sensitive to the variable order; they can have exponential size in the worst case and a linear size in the best case. There are functions (such as multipliers), whose BDD size is exponential regardless of the ordering. Furthermore, there are functions for which the sum of products (SOP) or product of sums (POS) forms are more compact than the BDDs. Many constraint functions of covering problems fall in this category. Figure 2 shows two BDDs for function  $F = x_1x_2 + x_3x_4 + x_5x_6$  constructed with two different ordering of variables, lexicographical, and interleaved. One can see significant difference in BDD size.

Figure 2: Effect of variable ordering on BDD size for function  $F = x_1x_2 + x_3x_4 + x_5x_6$ : a) for variable order  $x_1, x_2, x_3, x_4, x_5, x_6$  b) for variable order  $x_1, x_3, x_5, x_2, x_4, x_6$ .

While the variable ordering problem is NP-complete, efficient heuristic variable ordering algorithm exist, based on both static (related to lexicographical) and dynamic ordering (swapping variables on two adjacent levels) [8].

**Extensions.** Several extensions have been proposed for BDDs. One of them makes a use of *complemented edges* by labeling BDD edges with complement attributes. This feature makes it possible to represent a function and its complement as a single subgraph with two edges coming into the root of the subgraph, one with positive polarity and the other with negative polarity. In general, BDDs with complemented edges result in a smaller BDD size and provide a means to complement a BDD in constant time. To maintain the canonicity, certain restrictions are imposed on the placement of the complemented edges. Namely, only *low* edges, corresponding to negative

cofactors, may be assigned complement attributes. Notice that for BDD with complemented edges, only one constant function (1) and hence only one terminal node (leaf 1) is needed, since 0 can be derived from its complement.

**Applications and Limitations of BDDs.** Owing to their compactness, canonicity and ease of manipulation, BDDs have found numerous applications in design, synthesis, verification and testing of digital designs. In general, BDDs are an efficient data structure for storing and evaluating Boolean function and discrete structures. Large sets of discrete elements can be encoded in binary and compactly represented as characteristic functions in BDDs. BDDs come particularly handy in representing transition relations of product machines for the purpose of sequential equivalence checking using state traversal [7].

In particular, BDDs have found a widespread application in a number of verification problems, including combinational equivalence checking [9], implicit state enumeration and FSM traversal [7, 10], symbolic model checking [11] [12], test vector generation, and many others. The biggest claim to fame comes from their applications to *combinational equivalence checking*. Once two logic functions are represented by their respective ROBDDs (with the same variable order), one can test whether two Boolean functions are equivalent by testing if their ROBDDs are isomorphic. In practice, checking for equivalence between two functions is performed by constructing a single, multi-rooted BDD, rather than checking for graph isomorphism. The two functions are equivalent if they share the same root. This test can be done in constant time once the BDD is built for the two functions.

Logic equivalence can be illustrated with the BDD shown in Figure 1(c). The ROBDD in the figure, constructed for function f = (a+b)c, also represents function  $g = a \cdot c + b \cdot c$ , as well as a number of other equivalent functions, all having the same BDD for a fixed variable order. As mentioned earlier, BDDs can be built for an arbitrary gate-level network or a multiple-output Boolean function. Such created BDD can then be used to check equivalence of the netlist against another netlist, or against the initial Boolean specification of the design.

Another obvious application of BDDs is *satisfiability* (SAT). A Boolean function is satisfiable if there exists an assignment of Boolean values to its variables that makes the function true (f = 1). Many verification, synthesis and optimization problems can be reduced to the SAT problem. Being a decision diagrams, BDD can be used to solve the SAT problem in linear time in its size. Once the formula to be satisfied is converted to a BDD, the BDD is traversed to find one or more paths from the root to the terminal node 1. A satisfying solution exists as long as the BDD is not empty. This important feature of decision diagrams finds its application in deterministic *test generation*, used in simulation based verification. A target assignment, not adequately covered by semi-random or directed simulation, is specified and solved using BDD-based SAT.

The BDD-based approach to the SAT problem can be illustrated with the example in Figure 1(c). Two satisfying solution for f = 1, corresponding to the paths from the root to node 1, are  $\{ac\}$  and  $\{\bar{a}bc\}$ .

A special case of SAT is related to finding a satisfying assignment for f = 0. A notion of *easily invertible* form was introduced by Bryant to denote a representation for which it is always possible to find a zero of the function (solve for f = 0) in polynomial time [13]. Clearly, BDDs are easily convertible functions, since one can find a solution to the problem by tracing the path from the

root to terminal node 0. Another special case of SAT involves testing for *tautology*, i.e., testing if function is identically equal to 1 (for all assignments of Boolean variables). This can be done in constant time by testing if BDD for the function is reduced to constant 1.

Several efficient implementation of software program supporting BDDs have been developed for a wide set of purposes [14]. One of the most popular packages, available on the world wide web is the CUDD package [15].

In summary, BDDs have been very successful in verifying control-dominated applications and are a part of a number of formal verification systems, such as SMV [12] and VIS [16]. However, as the designs have grown in size and complexity, the size-explosion problems of BDDs have limited their scope. Furthermore, their use in designs containing large arithmetic data-path units have not been very limited due to prohibitive memory requirements, especially for large multipliers.

#### 2.2 Beyond BDDs

In an attempt to obtain a more compact representation for Boolean functions, different flavors of Boolean decomposition have been tried. These diagrams, collectively known as *Decision Diagrams*, are still based on a "point-wise" binary decomposition, but use a different interpretation of the diagram nodes.

One such representation is based on the XOR (exclusive OR) decomposition:

$$f = f_{\bar{x}} \oplus x f_{\Delta x} = f_x \oplus \bar{x} f_{\Delta x} \tag{3}$$

also known as Red-Miller or Davio decomposition. Here,  $f_{\Delta x}$  denotes the Boolean difference of function f w.r.t. variable x, i.e.,  $f_{\Delta x} = f_x \oplus f_{\bar{x}}$ , where  $\oplus$  represents an XOR operation.

Ordered Functional Decision Diagrams (*OFDDs*) [17] are based on such a decomposition. This representation is analogous to that of OBDDs, except that the two outgoing arcs at each node represent the negative cofactor and the Boolean difference of the function w.r.t. the node variable. Similar to OBDDs, OFDD representation is canonical and many operations can be implemented with algorithms of polynomial complexity. However, several important features differentiate the two representations. First, different reduction rules are applied to make the graph canonical. Second, the evaluations of a function on a OFDDD involves more than tracing a path. In particular for a node variable *x*, both subgraphs must be evaluated and an XOR computed. Such an evaluation can be performed in linear time in the number of nodes by a postorder traversal of the graph. An interesting feature of the OFDDs is that, for certain classes of functions (in particular, arithmetic functions based on XORs), OFDDs are exponentially more compact than ROBDDs, but the reverse is also true. To obtain the advantages of each representation, Drechsler *et al* proposed a hybrid form, called Ordered Kronecker FDD (OKFDD) [18]. In this representation, each variable can use any of the three decompositions given by equations 1 - 3, potentially leading to a reasonable reduction in the graph size.

Another variant of BDD representation, called Zero-Suppressed BDDs (ZBDDs), was developed by Minato for solving combinatorial problems [19]. ZDDS are particularly suitable for applications involving sparse sets of bit vectors. It can be shown that ZBDDs reduce the size of the representation of a set of n-bit vectors over OBDDs by at most a factor of n. In practice, the reduction is large enough to have a significant impact.

Numerous attempts have been made to extend the capabilities of BDDs to target arithmetic circuits and designs with word-level specifications. This requires extending the concept of Boolean function representation to integer and real-valued functions over Boolean variables. The resulting graph-based representations are commonly known as *Word Level Decision Diagrams* (WLDDs) [20,21].

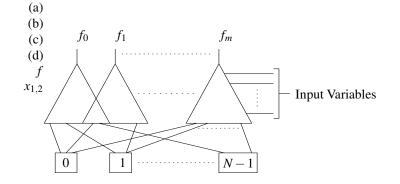

One straightforward way to represent numeric-valued functions is to use branching structure of a BDD, but to allow arbitrary values on the terminal nodes. Such a representation is referred to as Multi-terminal BDD (MTBDD) [22] or Algebraic Decision Diagram (ADD) [23]. Evaluating an MTBDD or ADD for a given variable assignment is similar to that of BDD. However, MTBDDs are inefficient in representing functions yielding values over a large range, as this requires a large number of terminal nodes and results in a large number of paths (MTBDDs tend to be trees rather than graphs).

For such applications, alternative representations have been proposed, such as edge-valued BDDs (EVBDDs) [24]. These forms incorporate numeric weights on the edges in order to allow greater sharing of subgraphs and to reduce the size of the overall representation. Evaluating a function represented by an EVBDD involves adding the products of variable values along the path, weighted by the corresponding edge weights. This representation grows linearly in the number of bits, a major improvement over MTBDDs. However, the overhead for storing and normalizing the edge weights to make the representation canonical makes it them less efficient. There are classes of functions, such as arithmetic functions, for which EVBDD has unacceptable size complexity. In particular, the EVBDD representation for integer multipliers,  $F = X \cdot Y$ , grows exponentially with the number of bits of its operands. A good review of WLDDs can be found in [20, 21].

In the next section, another type of word-level diagram is described, based on a different, non-pointwise decomposition principle.

### **3** Binary Moment Diagrams (BMD)

An alternative approach to representing numeric functions, especially those encountered in arithmetic circuits, involves changing the function decomposition with respect to its variables.

**The Decomposition Principle.** Binary Moment Diagrams (BMD), introduced by Bryant [13], use a modified Shannon's expansion, in which a Boolean variable is treated as a binary, (0,1) integer variable. The complement of x is modeled as  $\bar{x} = 1 - x$ , and the terms of the expansion are regrouped around variable x resulting in the following formula:

$$f(x) = (1 - x) \cdot f_{\bar{x}} + x \cdot f_x$$

$$= f_{\bar{x}} + x \cdot (f_x - f_{\bar{x}})$$

$$= f_{\bar{x}} + x \cdot f_{\Delta x}$$

$$(4)$$

where ".'", "+" and "-" denote multiplication, addition and subtraction, respectively. The above decomposition is termed as *moment* decomposition;  $f_{\bar{x}}$  is the *constant moment*, and  $(f_{\Delta x} = f_x - f_{\bar{x}})$

is the *linear moment*. In this form, f can be viewed as a *linear function* in x, with  $f_{\bar{x}}$  as the constant term, and  $(f_{\Delta x}$  as the linear coefficient of f (the partial derivative of f with respect to x). This expansion still relies on the assumption that variable x is Boolean, i.e., evaluates to either 0 or 1. However, it departs from a point-wise, decision-based decomposition and performs the decomposition of a linear function based on its first two moments.

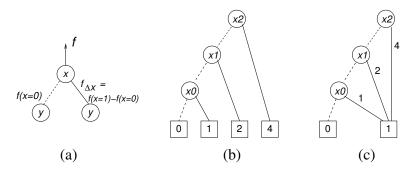

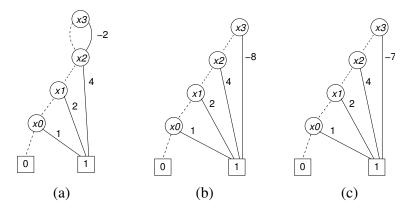

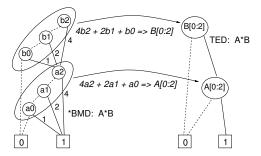

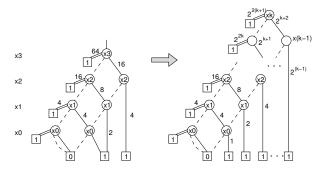

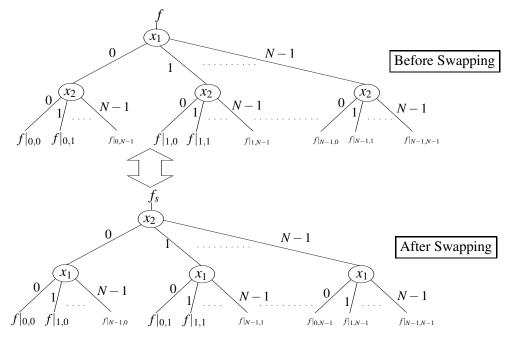

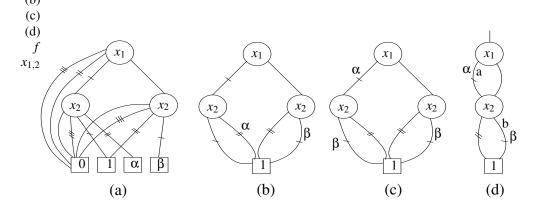

Each node of a BMD describes a function in terms of its moment decomposition with respect to the variable labeling the node, as shown in Figure 3(a). The two outgoing arcs from each node denote the constant moment (shown as dashed line) and the first moment (solid line) of the function w.r.t. the decomposing variable. Part (b) of the figure shows the BMD representation of the unsigned integer  $X = 4x_2 + 2x_1 + x_0$  encoded with n = 3 bits. The constants in the terminal nodes of the BMD can be moved from to their edges, and represented as edge-weights, as shown in Figure 3(c). The resulting diagram is termed Multiplicative Binary Moment Diagram, or \*BMD. The term "multiplicative" derives from the fact that, when evaluating a function along a path from root to one of its terminal nodes, the weights combine multiplicatively along the path.

Figure 3: Binary Moment Diagrams: (a) The moment decomposition principle; (b) BMD for binary encoded integer  $X = 4x_2 + 2x_1 + x_0$ ; (c) \*BMD for X.

Similarly to BDDs, function encoded in a \*BMD is evaluated by adding the terms encoded in the paths. However, two major features differentiate (\*)BMDs from decision diagrams discussed earlier: 1) \*BMDs are *not* decision diagrams, since they are based on the moment decomposition, rather than a point-wise Shannon expansion. 2) \*BMDs are *multiplicative* diagrams, in the sense that each path from root to terminal node is a product of the variables labeling the nodes and the edge weights along the path.

Figure 4 shows \*BMDs for addition and multiplication expressed at word levels. Note that the size of \*BMDs for these operations grows linearly with the word size *n*.

**Reduction Rules** Each node in the \*BMD is represented as a triple  $\langle v, low(v), high(v) \rangle$ , with two weights associated with the constant and linear moments,  $w_0(v), w_1(v)$ . It is assumed that the set of variables is totally ordered, like in a BDD. To maintain the canonical form certain reduction rules must be imposed on the \*BMD during node creation and weight manipulation (normalization). In principle, these rules are similar to those in BDDs, but must follow rules of regular algebra over  $(+, \cdot)$  rather than Boolean algebra  $(\lor, \land)$ .

1. (Irredundancy) When a linear moment at node *v* is 0, the function at the node evaluates to its constant moment, i.e., does not depend on *v*. In this case node *v* is redundant and is removed. (Note that this rules differs from the redundancy reduction rule for BDD).

Figure 4: \*BMD representations for word-level operations: (a) Sum X + Y; (b) Product  $X \cdot Y$ .

2. (Uniqueness) This rule is similar to that of BDD: any two nodes indexed by the same variable and have same two moments represent the same function and are merged in the BMD into a single node. This rule, however, is applied after the normalization, described next.

**Normalization:** Several rules for manipulating edge weights are imposed on the graph to make the graph canonical. For non-zero value of the linear moment at node v, the weights of its two edges are normalized by factoring out the greatest common divisor (*gcd*) of the argument weights  $w = gcd(w_0(v), w_1(v))$ , which is then pushed to the root edge of node v. By convention, the sign of the extracted weight must match the sign of the constant moment; this way *gcd* always returns non-negative value. Normalization is performed bottom up, from the leaf nodes to the root. Each normalized node is stored in the hash table, where each entry is indexed by a key composed of the variable and the two moments. Duplicate entries are automatically removed, resulting in an irredundant, minimal and canonical representation.

As with BDDs, the \*BMD representation of a function depends on the variable ordering, but \*BMDs are much less sensitive to variable ordering than BDDs.

**The** APPLY **Algorithms.** Similarly to BDDs, \*BMDs are constructed by starting with base functions, corresponding to constants and single variables, and then building more complex functions according to some operation. Algorithms similar to the APPLY algorithm for BDDs have been proposed. However, while there is a single APPLY algorithm for BDDs for an arbitrary Boolean operator, \*BMDs require algorithms tailored specifically for the individual operations, such as ADD, SUB and MULT [13]. In general,

$$f < op > g = (f < op > g)_{\bar{x}} + x(f < op > g)_{\Delta x}$$

(5)

where

$$(f < op > b)_{\bar{x}} = (f_{\bar{x}} < op > g_{\bar{x}})$$

(6)

and

$$(f < op > g)_{\Delta x} = (f < op > g)_x - (f < op > g)_{\bar{x}}$$

(7)

$$= (f_x < op > g_x) - (f_{\bar{x}} - g_{\bar{x}})$$

$$= ((f_x + f_{\Delta x}) < op > (g_x + g_{\Delta x}) - (f_{\bar{x}} - g_{\bar{x}})$$

However, in case of the multiply operation, special attention must be paid because of the introduction of the term containing  $x^2$ .

$$f \cdot g = (f_{\bar{x}} + x \cdot f_{\Delta x}) \cdot (g_{\bar{x}} + x \cdot g_{\Delta x}) = f_{\bar{x}} \cdot g_{\bar{x}} + x \cdot (f_{\bar{x}} \cdot g_{\Delta x} + f_{\Delta x} \cdot g_{\bar{x}}) + x^2 \cdot f_{\Delta x} \cdot g_{\Delta x}$$

(8)

The multiply operation must be linearized by replacing  $x^2$  with x, since x is a Boolean variable. This gives the following result for multiplication

$$f \cdot g = f_{\bar{x}} \cdot g_{\bar{x}} + x \cdot (f_{\bar{x}} \cdot g_{\Delta x} + f_{\Delta x} \cdot g_{\bar{x}} + f_{\Delta x} \cdot g_{\Delta x})$$

(9)

The APPLY algorithms proceed by traversing the argument graphs and recursively apply the operation to the subgraphs. To reduce the number of recursive calls, a hash table is maintained keyed by the arguments of the previous calls, allowing the program to reuse previous computations.

Unlike operations on BDDs, which have run-time complexities polynomial in the number of variables, most operations on \*BMDs potentially have exponential complexity. However, as demonstrated by Bryant, these exponential cased do not arise in practical applications [13]. Furthermore, the size of the arguments is significantly smaller in word-level applications than in bit-level applications, resulting in reasonable run-times.

For word-level expressions (X + Y) and (X \* Y), where X and Y are *n*-bit vectors, \*BMD representation is linear in the number of bits *n*. Also, function  $c^X$ , where *c* is a constant, have linear size representation in \*BMD. However, the size of \*BMD for  $X^k$  is  $O(n^k)$ . Thus, for high-degree polynomials defined over words with large bit-width, as commonly encountered in many DSP applications, filters, etc., \*BMD remains an expensive representation.

**Boolean Logic.** \*BMD can be adapted to also represent Boolean logic, which is important for designs with Boolean connectives. The following equations are used to model Boolean logic.

$$NOT: \quad \bar{x} = (1-x) \tag{10}$$

$$AND: \quad x \land y = x \cdot y \tag{11}$$

$$OR: \quad x \lor y = \quad x + y - x \cdot y \tag{12}$$

$$XOR: \quad x \oplus y = x + y - 2x \cdot y \tag{13}$$

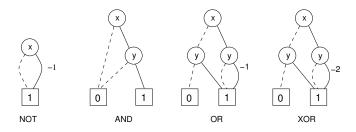

Figure 5 shows BMD representations for these basic Boolean operators [2]. In the diagrams, x and y are Boolean variables represented by binary variables, and + and  $\cdot$  represent algebraic operators of ADD and MULT, respectively. The resulting functions are 0,1 integer functions.

\*BMDs provide a concise representation of functions defined over bit vectors, or words of data, having a numeric representation. In particular they can efficiently encode integer-valued functions defined over binary-encoded words,  $X = \sum_i 2^i x_i$ , where each  $x_i = 0$  or 1. Figure 6 shows examples of \*BMD representation for signed integers several sign schemes (signed magnitude, ones complement, and twos complement). All commonly used encodings can be similarly represented.

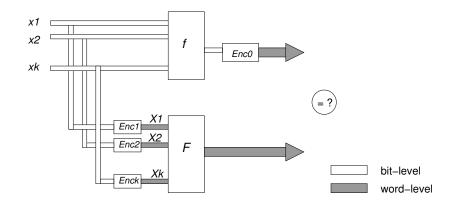

**Applications to Word-level Verification.** (\*)BMDs have been successfully used in formal verification of arithmetic circuits. Figure 7 illustrates an approach to arithmetic circuit verification

Figure 5: \*BMD representation for Boolean operators: a) NOT:  $\bar{x} = (1-x)$ ; b) AND:  $x \wedge y = x \cdot y$ ; c) OR:  $x \vee y = x + y - xy$ ; d) XOR:  $x \oplus y = x + y - 2xy$ .

Figure 6: \*BMD representations for word-level operations: a) Sign magnitude; b) Two's complement; c) One's complement.

proposed in [13,25]. The goal is to prove a correspondence between a logic circuit, represented by a vector of Boolean functions f, and the design specification, represented by a word-level function F. The inputs to the Boolean circuit f are vectors of Boolean signals,  $x_1, x_2, ..., x_k$ ; the inputs to the specification function F are word-level signals (symbolic variables)  $X_1, X_2, ..., X_k$ . In order to compare the two designs, each of the Boolean vectors  $x_i$  is transformed into a word-level signal  $X_i$ using an encoding function  $Enc_i(x_i)$ , and connected to the appropriate input of F. An encoding function simply provides the interpretation of the bit vectors. An example of such an encoding function (in this case, unsigned integer) is shown in Figure 3. Similarly, the output of the logic circuit f is transformed to a word-level function using an encoding function  $Enc_0$ . The general task of verification is then to prove the equivalence between the circuit output, interpreted as a word, and the output of the word-level specification.

$$Enc_0(f(x_1,\ldots,x_k)) = F(Enc_1(x_1),\ldots,Enc_k(x_k))$$

(14)

\*BMDs can provide suitable data structure for this form of verification. TEDs, described in the next section, can be used for for the final comparison at the word-level.

A serious limitation of (\*)BMDs is that they cannot be used for solving SAT problems. This is because (\*)BMDs are multiplicative diagrams, i.e., the weights combine multiplicatively along the path from terminal node to root. Solving the integer-valued SAT problem in this structure is equivalent to solve the integer factorization problem. They are also not "easily invertible", as defined earlier in the context of the decision diagrams.

Figure 7: General verification problem: prove correspondence between a word-level specification and bit-level implementation.

Several variants of \*BMD representation have been proposed in literature. Chen *et al* introduced Multiplicative Power Hybrid Decision Diagrams (PHDDs) that allows it to handle floating point arithmetic [26]. This is the only known form that supports floating point operation in a graph without introducing rational numbers, by representing the mantissa and exponent as connected subgraphs. However, the size of the graph, even for the adder function, grows exponentially with the size of the exponent size.

Drechsler *et al* extended \*BMDs to a form called K\*BMD to make the decomposition more efficient in terms of the graph size. This is done by admitting multiple decomposition types and allowing both additive and multiplicative edge weights [27]. However, a set of restrictions imposed on the edge weights to make it canonical makes such a graph difficult to construct. K\*BMD is characterized by linear complexity of the word-level operations for sum, product and  $c^X$ , and can represent  $X^k$  in  $O(n^{k-1})$  nodes. As we will see in the next section, this result can be further improved with TEDs [3], which offer linear size complexity for this and other word-level operations.

### **4** Taylor Expansion Diagrams (TED)

Before formally introducing TEDs, we briefly review previous work and recent advances in wordlevel equivalence checking and the supporting symbolic representations.

#### 4.1 Related Work.

In the realm of high-level design verification, the issue of abstraction of symbolic, word-level computations have received a lot of attention. This is visible in theorem-proving techniques, automated decision procedures for Presburger arithmetic [28] [29], techniques using algebraic manipulation [30], symbolic simulation [31], or in the decision procedures that use a combination of theories [32] [33]. *Term rewriting* systems, particularly those used for hardware verification [34–36] also represent computations in high-level symbolic forms. The above representations and verification techniques, however, do not rely on canonical forms. For example, verification techniques using term rewriting are based on rewrite rules that lead to normal forms. Such forms may produce false negatives, which may be difficult to analyze and resolve.

Various forms of *high-level logics* have been used to represent and verify high-level design specifications. Such representations are mostly based on quantifier free fragments of first order logic. The works that deserve particular mention include: the logic of equality with uninterpreted functions (EUF) [37] and with memories (PEUFM) [38] [39], and the logic of counter arithmetic with lambda expressions and uninterpreted functions (CLU) [40]. These logics are often transformed into canonical representations, such as BDDs and BMDs, or into SAT instances or other normal forms [41] [42]. To avoid exponential explosion of BDDs, equivalence verification is generally performed by transforming high-level logic description of the design into propositional logic formulas [40] [33] [38] and employing satisfiability tools [43] [44] for testing the validity of the formulas. While these techniques have been successful in the verification of control logic and pipelined microprocessors, they have found limited application in the verification of large datapath designs.

Word-Level ATPG techniques [45] [46] [47] [48] [49] have also been used for RTL and behavioral verification. However, their applications are generally geared toward simulation, functional vector generation or assertion property checking, but not so much toward high-level equivalence verification of arithmetic designs.

**Symbolic Algebra Methods.** Many computations encountered in behavioral design specifications can be represented in terms of polynomials. This includes digital signal and image processing designs, digital filter designs, and designs that employ complex transformations, such as DCT, DFT, WHT, etc. Polynomial representations of discrete functions have been explored in literature long before the advent of contemporary canonical graph-based representations. Particularly, Taylor's expansion of Boolean functions has been studied in [50] [51]. However, these works mostly targeted classical switching theory problems: logic minimization, functional decomposition, fault detection, etc. The issue of abstraction of bit-vectors and symbolic representation of computations for high-level synthesis and formal verification was not their focus.

Commercial symbolic algebra tools, such as Maple [52], Mathematica [53], and MatLab [54], use advanced symbolic algebra methods to perform efficient manipulation of of mathematical expressions, including fast multiplication, factorization, etc. However, despite the unquestionable effectiveness of these methods for classical mathematical applications, they are less effective in modeling of large scale digital circuits and systems, and in particular in polynomial verification. For example, symbolic algebra tools offered by Mathematica and alike cannot unequivocally determine the *equivalence* of two polynomials. The equivalence is checked by subjecting each polynomial to a series of *expand* operations and comparing the coefficients of the two polynomials ordered lexicographically. As stated in the manual of Mathematica 5, "*it would be quite impossible for Mathematica to match patterns by mathematical, rather than structural, equivalence.*" And "*there is no general way to find out whether an arbitrary pair of mathematical expressions are equal*" [53]. Furthermore, Mathematica "*cannot guarantee that any finite sequence of transformations will take any two arbitrarily chosen expressions to a standard form.*"

In contrast, the TED data structure described in the sequel provides an important support for equivalence verification by offering a canonical representation for multi-variate polynomials. **Equivalence Checking.** Equivalence checking has been researched thoroughly and vast literature exists on the topic, including satisfiability (SAT) approaches [45, 48, 49, 55, 56] verification of arithmetic on bit-level [57–59], symbolic approaches and others [60–66].

Typical approach to equivalence checking (EC) employed by industrial tools, involves identifying structural equivalences or "similarities" between pairs of points (called *cut points*) in the two designs. The portions of designs identified as having equivalent cut points are removed from the design and the EC verification is repeated on the reduced designs. However, the main difficulty lies in identifying such cut points in designs described in different levels (e.g., RTL and algorithmic). Another challenge in EC verification comes from structural optimizations, employed by behavioral or high-level synthesis (such as factorization, resource sharing, change of order of operators, operator merging, etc.), which reduce the level of similarity between the candidate cut points. The next section provides a motivating example for the development of symbolic equivalence technique based on functional, rather than structural approach and the associated canonical representation.

#### 4.2 Motivation

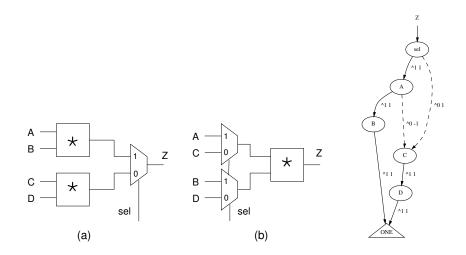

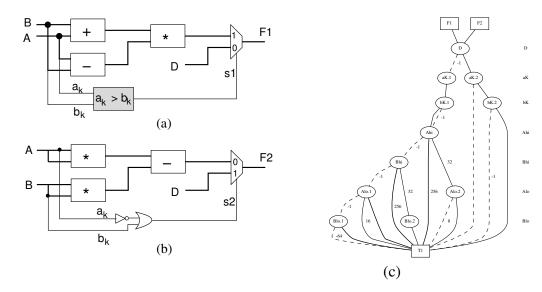

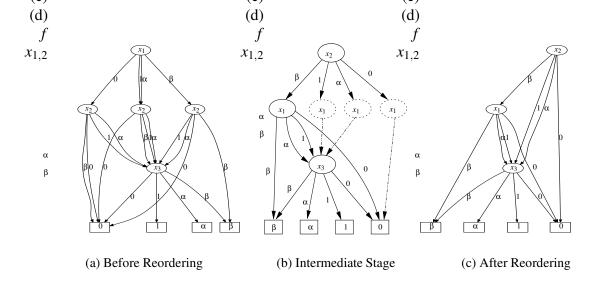

The following example, Figure 8(a),(b), taken from the Synopsys technical bulletin [67], illustrates the perceived difficulty of functional verification of arithmetic designs in case of a combinational transformation, called resource sharing. Resource sharing transforms the netlist by moving the operators in order to maximize sharing of the resources, in this case the multiplication. Arithmetic Proof Engine (APF) of Synopsys' Formality tool cannot solve this problem using cut-points because internally equivalent points are lost during such a transformation.

Figure 8: Verification of resource sharing: (a) z = sel?  $(A \cdot B)$ :  $(C \cdot D)$ ; (b) z = (sel?  $A : C) \cdot (sel$ ? B : D); (c) Canonical TED showing functional equivalence of the two structures:  $z = A \cdot B \cdot sel + C \cdot D \cdot (1 - sel) = (A \cdot sel + C \cdot (1 - sel)) \cdot (B \cdot sel + D \cdot (1 - sel))$  for sel = 0, 1.

This problem can be solved, however, by generating the symbolic expressions for the original and the transformed forms in a canonical form, and proving that they are equivalent. Namely, the

function computed by the original design shown in Figure 8(a) can be written as

$$z = A \cdot B \cdot sel + C \cdot D \cdot (1 - sel) \tag{15}$$

while the design in Figure 8(b) can be expressed as

$$(A \cdot sel + C \cdot (1 - sel)) \cdot (B \cdot sel + D \cdot (1 - sel))$$

$$(16)$$

Since *sel* is a binary variable,  $sel^2 = sel$  and  $sel \cdot (1 - sel) = 0$ , and the above expression reduces to the expression (16). These expressions can be captured by a canonical data structure with symbolic input variables *A*, *B*, *sel*. Such a diagram is shown in Figure 8(c). The equivalence of the two designs can be verified by testing if the diagrams corresponding to the two designs are isomorphic, which is the case here (only one graph is shown). This is the main idea behind Taylor Expansion Diagrams, described next. Note that, unlike BMDs, this diagram represents the designs with arbitrary bit-width; that is the designs can verified for equivalence regardless of their word sizes, assuming infinite precision arithmetic.

#### 4.3 The Taylor Series Expansion

A known limitation of all decision and moment diagram representations is that *word-level* computations, such as A + B, require the function to be decomposed with respect to *bit-level* variables A[k], B[k]. Such an expansion creates a large number of variables in the respective diagram framework and requires excessive memory and time to operate upon them. In order to efficiently represent and process the HDL description of a large design, it is desirable to treat the word-level variables as *algebraic symbols*, expanding them into their bit-level components only when necessary.

Figure 9: Abstraction of bit-level variables into algebraic symbols for  $F = A \cdot B$ .

Consider the \*BMD for  $A \cdot B$ , shown in Fig. 9 (a), which depicts the decomposition with respect to the bits of A and B. It would be desirable to group the nodes corresponding to the individual bits of these variables to *abstract* the integer variables they represent, and use the abstracted variables directly in the design. Fig. 9 depicts the idea of such a *symbolic abstraction* of variables from their bit-level components.

In order to achieve the type of abstracted representation depicted above, one can rewrite the moment decomposition  $f = f_{\overline{x}} + x \cdot (f_x - f_{\overline{x}})$  as  $f = f(x = 0) + x \cdot \frac{\partial(f)}{\partial x}$ . This equation resembles a truncated *Taylor series expansion* of the linear function f with respect to x. By allowing x to take integer values, the binary moment decomposition can be generalized to a Taylor's series expansion, where integer variables do not need to be expanded into bits.

In this approach, an algebraic, multi-variate expression, f(x, y, ...), can be viewed as continuous, differentiable function oever a real domain. It can be decomposed using the Taylor series expansion with respect to variable x as follows [68]:

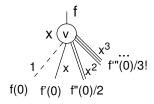

$$f(x) = \sum_{k=0}^{\infty} \frac{1}{k!} (x - x_0)^k f^k(x_0) = f(0) + xf'(0) + \frac{1}{2} x^2 f''(0) + \dots$$

(17)

where  $f'(x_0)$ ,  $f''(x_0)$ , etc., are first, second, and higher order derivatives of f with respect to x, evaluated at  $x_0 = 0$ . The derivatives of f evaluated at x = 0 are independent of variable x, and can be further decomposed w.r.t. the remaining variables, one variable at a time. The resulting recursive decomposition can be represented by a decomposition diagram, called the *Taylor Expansion Diagram*, or TED.

The Taylor series expansion can be used to represent computations over integer and Boolean variables, commonly encountered in HDL descriptions. Arithmetic functions and dataflow portions of those designs, can be expressed as multi-variate polynomials of finite degree, for which Taylor series is finite.

**Definition 4.1** The **Taylor Expansion Diagram**, or **TED**, is a directed acyclic graph  $(\Phi, V, E, T)$ , representing a multi-variate polynomial expression  $\Phi$ . V is the set of nodes, E is the set of directed edges, and T is the set of terminal nodes in the graph. Every node  $v \in V$  has an index var(v) which identifies the decomposing variable. The function at node v is determined by the Taylor series expansion at x = var(v) = 0, according to equation 17. The number of edges emanating from node v is equal to the number of nonempty derivatives of f (including f(0)) w.r.t. variable var(v). Each edge points to a subgraph whose function evaluates to the respective derivative of the function with respect to var(v). Each subgraph is recursively defined as TED w.r.t. the remaining variables. Terminal nodes evaluate to constants.

Figure 10: A decomposition node in a TED.

Starting from the *root*, the decomposition is applied recursively to the subsequent children nodes. The internal nodes are in one-to-one correspondence with the successive derivatives of function f w.r.t. variable x evaluated at x = 0. Figure 10 depicts one-level decomposition of function f at variable x. The k-th derivative of a function rooted at node v with var(v) = x is referred to as a k-child of v; f(x=0) is a 0-child, f'(x=0) is a 1-child,  $\frac{1}{2!}f''(x=0)$  is a 2-child, etc. We shall also refer to the corresponding arcs as 0-edge (dotted), 1-edge (solid), 2-edge (double), etc.

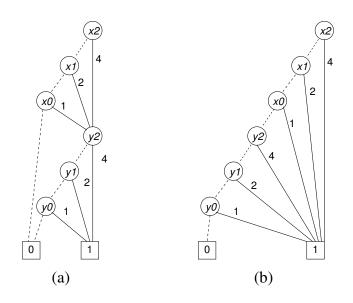

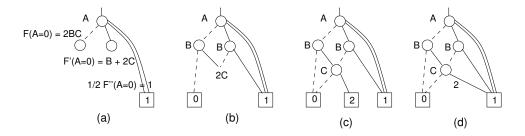

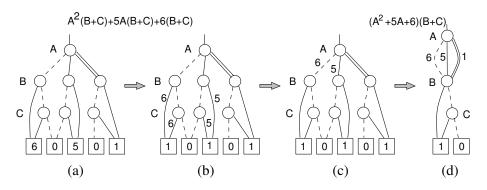

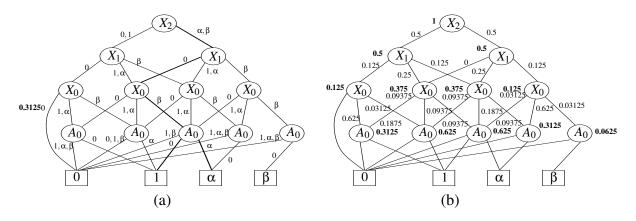

*Example:* Figure 11 shows the construction of a TED for the algebraic expression  $F = A^2 + A \cdot (B + 2 \cdot C + 2 \cdot B \cdot C)$ . Let the ordering of variables be A, B, C. The decomposition is performed first with respect to variable A. The constant term of the Taylor expansion  $F(A = 0) = 2 \cdot B \cdot C$ . The linear term of the expansion gives  $F'(A = 0) = B + 2 \cdot C$ ; the quadratic term is  $\frac{1}{2} \cdot F''(A = 0) = \frac{1}{2} \cdot 2 = 1$ . This decomposition is depicted in Fig. 11 (a). Now the Taylor series expansion is applied recursively to the resulting terms with respect to variable B, as shown in Fig. 11(b), and subsequently with respect to variable C. The resulting diagram is depicted in Fig. 11(c), and its final reduced and normalized version (to be explained in Section 4.4) is shown in Fig. 11(d). The function encoded by the TED can be evaluated by adding all the paths from non-zero terminal nodes to the root, each path being a product of the variables in their respective powers and the edge weights, resulting in  $F = A^2 + AB + 2AC + 2BC$ .

Figure 11: Construction of a TED for  $F = F = A^2 + AB + 2AC + 2BC$ : (a)-(c) decomposition w.r.t. individual variables; (d) normalized TED

Using the terminology of computer algebra [69], TED employs a *sparse recursive representation*, where a multivariate polynomial  $p(x_1, \dots, x_n)$  is represented as:

$$p(x_1, \dots, x_n) = \sum_{i=0}^{m} p_i(x_1, \dots, x_{n-1}) x_n^i$$

(18)

The individual polynomials  $p_i(x_1, \dots, x_{n-1})$  can be viewed as "coefficients" of the leading variable  $x_n$  at the decomposition level corresponding to  $x_n$ . By construction, the sparse form stores only non-zero polynomials as the nodes of the TED.

#### 4.4 Reduction and Normalization

It is possible to further reduce the size of an ordered TED by a process of TED *reduction* and *normalization*. Analogous to BDDs and \*BMDs, Taylor Expansion Diagrams can be reduced by removing redundant nodes and merging isomorphic subgraphs. In general, a node is redundant if it can be removed from the graph, and its incoming edges can be redirected to the nodes pointed to by the outgoing edges of the node, without changing the function represented by the diagram.

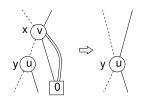

Definition 4.2 A TED node is redundant if all of its non-0 edges are connected to terminal 0.

If node v contains only a constant term (0-edge), the function computed at that node does not depend on the variable var(v), associated with the node. Moreover, if all the edges at node v point

Figure 12: Removal of redundant node with only a constant term edge.

to the terminal node 0, the function computed at the node evaluates to zero. In both cases, the parent of node v is reconnected to the 0-child of v, as depicted in Fig. 12.

Identification and merging of isomorphic subgraphs in a TED are analogous to that of BDDs and \*BMDs. Two TEDs are considered *isomorphic* if they match in both their structure and their attributes; *i.e.* if there is a one-to-one mapping between the vertex sets and the edge sets of the two graphs that preserve vertex adjacency, edge labels and terminal leaf values. By construction, two isomorphic TEDs represent the same function. In order to make the TED canonical, any redundancy in the graph must be eliminated and the graph must be reduced. The reduction process entails merging the isomorphic sub-graphs and removing redundant nodes.

**Definition 4.3** A Taylor expansion diagram is **reduced** if it contains no redundant nodes and has no distinct vertices v and v', such that the subgraphs rooted at v and v' are isomorphic. In other words, each node of the reduced TED must be unique.

It is possible to further reduce the graph by performing *normalization*, similar to the one described for \*BMDs [2]. The normalization procedure starts by moving the numeric values from the non-zero terminal nodes to the terminal edges, where they are assigned as edge *weights*. This is shown in Fig. 11(d) and Fig. 13(b). By doing this, the terminal node holds constant 1. This operation applies to all terminal edges with terminal nodes holding values different than 1 or 0. As a result, only terminal nodes 1 and 0 are needed in the graph. The weights at the terminal edges may by further propagated to the upper edges of the graph, depending on their relative values. The TED normalization process that accomplishes this is defined as follows.

**Definition 4.4** A reduced, ordered TED representation is **normalized** when:

- The weights assigned to the edges spanning out of a given node are relatively prime.

- Numeric value 0 appears only in the terminal nodes.

- The graph contains no more than two terminal nodes, one each for 0 and 1.

By ensuring that the weights assigned to the edges spanning out of a node are relatively prime, the extraction of common subgraphs is enabled. Enforcing the rule that none of the edges be allowed zero weight is required for the canonization of the diagram. When all the edge weights have been propagated up to the edges, only the value 0 and 1 can reside in the terminal nodes.

The normalization of the TED representation is illustrated by an example in Fig. 13. First, as shown in Fig. 13(b), the constants (6, 5) are moved from terminal nodes to terminal edges. These

Figure 13: Normalization of the TED for  $F = (A^2 + 5A + 6)(B + C)$

weights are then propagated up along the linear edges to the edges rooted at nodes associated with variable *B*, see Fig. 13(c). At this point the isomorphic subgraphs (B + C) are identified at the nodes of *B* and the graph is subsequently reduced by merging the isomorphic subgraphs, as shown in Fig. 13(d).

It can be shown that normalization operation can reduce the size of a TED exponentially. Conversely, transforming a normalized TED to a non-normalized TED can, in the worst-case, result in an exponential increase in the graph size. This result follows directly from the concepts of normalization of BMDs to \*BMDs [2].

#### 4.5 Canonicity of Taylor Expansion Diagrams

It now remains to be shown that an ordered, reduced and normalized Taylor Expansion Diagram is canonical; *i.e.* for a fixed ordering of variables, any algebraic expression is represented by a unique reduced, ordered and normalized TED. First, we recall the following Taylor's Theorem, proved in [68].

**Theorem 1** (Taylor's Theorem [68]) Let f(x) be a polynomial function in the domain R, and let  $x = x_0$  be any point in R. There exists one and only one unique Taylor's series with center  $x_0$  that represents f(x) according to the equation 17.

The above theorem states the uniqueness of the Taylor's series representation of a function, evaluated at a particular point (in our case at x = 0). This is a direct consequence of the fact that the successive derivatives of a function evaluated at a point are unique. Using the Taylor's theorem and the properties of reduced and normalized TEDs, it can be shown that an ordered, reduced and normalized TED is canonical.

**Theorem 2** For any multivariate polynomial f with integer coefficients, there is a unique (up to isomorphism) ordered, reduced and normalized Taylor Expansion Diagram denoting f, and any other Taylor Expansion Diagram for f contains more vertices. In other words, an ordered, reduced and normalized TED is minimal and canonical.

**Proof:** The proof of this theorem follows directly the arguments used to prove the canonicity and minimality of BDDs [1] and \*BMDs [2].

*Uniqueness*. First, a reduced TED has no trivial redundancies; the redundant nodes are eliminated by the reduce operation. Similarly, a reduced TED does not contain any isomorphic subgraphs. Moreover, after the normalization step, all common subexpressions are shared by further application of the reduce operation. By virtue of the Taylor's Theorem all the nodes in an ordered, reduced and normalized TED are unique and distinguished.

*Canonicity.* We now show that the individual Taylor expansion terms, evaluated recursively, are uniquely represented by the internal nodes of the TED. First, for polynomial functions the Taylor series expansion at a given point is finite and, according to the Taylor's Theorem, the series is unique. Moreover, each term in the Taylor's series corresponds to the successive derivatives of the function evaluated at that point. By definition, the derivative of a differentiable function evaluated at a particular point is also unique. Since the nodes in the TED correspond to the recursively computed derivatives, every node in the diagram uniquely represents the function computed at that node. Since every node in an ordered, reduced and normalized TED is distinguished and it uniquely represents a function, the Taylor Expansion Diagram is canonical.

*Minimality.* We now show that a reduced, ordered and normalized TED is also minimal. This can be proved by contradiction. Let G be a graph corresponding to a reduced, normalized and hence canonical TED representation of a function f. Assume there exists another graph G', with the same variable order as in G, representing f that is smaller in size than G. This would imply that graph G could be reduced to G' by the application of reduce and normalize operations. However, this is not possible as G is a reduced and normalized representation and contains no redundancies. The sharing of identical terms across different decomposition levels in the graph G has been captured by the reduction operation. Thus G' cannot have a representation for f with fewer nodes than G. Hence G is a minimal and canonical representation for f. [Q.E.D.]

### 4.6 Complexity of Taylor Expansion Diagrams

Let us now analyze the worst-case size complexity of an ordered and reduced Taylor Expansion Diagram. For a polynomial function of degree k, decomposition with respect to a variable can produce k+1 distinct Taylor expansion terms in the worst-case.

**Theorem 3** Let f be a polynomial in n variables and maximum degree k. In the worst case, the ordered, reduced, normalized Taylor Expansion Diagram for f requires  $O(k^{n-1})$  nodes and  $O(k^n)$  edges.

**Proof:** The top-level contains only one node, corresponding to the first variable. Since its maximum degree is k, the number of distinct children nodes at the second level is bounded by k + 1. Similarly, each of the nodes at this level produces up to k+1 children nodes at the next level, giving a rise to  $(k+1)^2$  nodes, and so on. In the worst case the number of children increases in geometric progression, with the level *i* containing up to  $(k+1)^{i-1}$  nodes. For an *n*-variable function, there will be *n*-1 such levels, with the *n*-th level containing just two terminal nodes, 1 and 0. Hence the total number of internal nodes in the graph is  $N = \sum_{i=0}^{n-1} (k+1)^i = \frac{(k+1)^{n-1}}{k}$ . The number of edges *E* can be similarly computed as  $E = \sum_{i=1}^{n} (k+1)^i = \frac{(k+1)^{n+1}-1}{k} - 1$ , since there may be up to  $(k+1)^n$  terminal edges leading to the 0 and 1 nodes. Thus, in the worst-case, the total number

of internal nodes required to represent an *n*-variable polynomial with degree k is  $O(k^{n-1})$  and the number of edges is  $O(k^n)$ . [Q.E.D.]

One should keep in mind, however, that the TED variables represent symbolic, word-level signals, and the number of such signals in the design is significantly smaller than the number of bits in the bit-level representation. Subsequently, even an exponential size of the polynomial with a relatively small number of such variables may be acceptable. Moreover, for many practical designs the complexity is not exponential.

Finally, let us consider the TED representation for functions with variables encoded as *n*-bit vectors,  $X = \sum_{i=0}^{n-1} 2^i x_i$ . For linear expressions, the space complexity of TED is linear in the number of bits *n*, the same as \*BMD. For polynomials of degree  $k \ge 2$ , such as  $X^2$ , etc., the size of \*BMD representation grows polynomially with the number of bits, as  $O(n^k)$ . For K\*BMD the representation also becomes nonlinear, with complexity  $O(n^{k-1})$ , for polynomials of degree  $k \ge 3$ . However, for ordered, reduced and normalized TEDs, the graph remains linear in the number of bits, namely  $O(n \cdot k)$ , for any degree *k*, as stated in the following theorem.

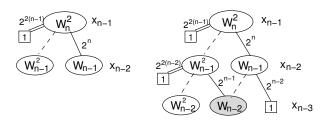

**Theorem 4** Consider variable X encoded as an n-bit vector,  $X = \sum_{i=0}^{n-1} 2^i x_i$ . The number of internal TED nodes required to represent  $X^k$  in terms of bits  $x_i$ , is k(n-1)+1.

**Proof:** We shall first illustrate it for the quadratic case k = 2. Let  $W_n$  be an *n*-bit representation of X:  $X = W_n = \sum_{i=0}^{n-1} 2^i x_i = 2^{(n-1)} x_{n-1} + W_{n-1}$  where  $W_{n-1} = \sum_{i=0}^{n-2} 2^i x_i$  is the part of X containing the lower (*n*-1) bits. With that,  $W_n^2 = (2^{n-1}x_{n-1} + W_{n-1})^2 = 2^{2(n-1)}x_{n-1}^2 + 2^n x_{n-1}W_{n-1} + W_{n-1}^2$ . Furthermore, let  $W_{n-1} = (2^{n-2}x_{n-2} + W_{n-2})$ , and  $W_{n-1}^2 = (2^{2(n-2)}x_{n-2}^2 + 2^{n-1}x_{n-2}W_{n-2} + W_{n-2}^2)$ . Notice that the constant term (0-edge) of  $W_{n-1}$  w.r.to variable  $x_{n-2}$  contains the term  $W_{n-2}$ , while

the linear term (1-edge) of  $W_{n-1}^2$  contains  $2^{n-1}W_{n-2}$ . This means that the term  $W_{n-2}$  can be *shared* at this decomposition level by two different parents. As a result, there are exactly two non-constant terms,  $W_{n-2}$  and  $W_{n-2}^2$  at this level.

Figure 14: Construction of TED for  $X^2$  with *n* bits

In general, at any level *l*, associated with variable  $x_{n-l}$ , the expansion of terms  $W_{n-l}^2$  and  $W_{n-l}$  will create *exactly two* different non-constant terms, one representing  $W_{n-l-1}^2$  and the other  $W_{n-l-1}$ ; plus a constant term  $2^{n-l}$ . The term  $W_{n-l-l}$  will be shared, with different multiplicative constants, by  $W_{n-l}^2$  and  $W_{n-l}$ .

This reasoning can be readily generalized to arbitrary integer degree k; at each level there will always be exactly k different non-constant terms. Since on the top variable  $(x_{n-1})$  level there is only one node (the root), and there are exactly k non-constant nodes at each of the remaining (n-1) levels, the total number of nodes is equal to k(n-1)+1.

The derivation of TED representation for  $X^2$  generalized to *n* bits is shown in Figure 15,

Figure 15: Derivation of TED representation for  $X^2$  with *n* bits

Table 1 compares the worst-case size complexity of the canonical "decision" diagrams described in this chapter in terms of the number of nodes as a function of the size of their operands (bit-width n). It shows significantly lower worst-case complexity of TED compared to other representations.

| Diagram type | X     | X + Y | $X \cdot Y$ | $X^k$     | $c^X$ |

|--------------|-------|-------|-------------|-----------|-------|

| MTBDD        | exp   | exp   | exp         | exp       | exp   |

| EVBDD        | lin   | lin   | exp         | exp       | exp   |

| *BMD         | lin   | lin   | lin         | $n^k$     | lin   |

| K*BMD        | lin   | lin   | lin         | $n^{k-1}$ | lin   |

| TED          | const | const | const       | (n-1)k    | -     |

Table 1: Size complexity of different canonical diagrams

#### 4.7 Composition of Taylor Expansion Diagrams

Taylor Expansion Diagrams can be composed to compute complex expressions from simpler ones. This section describes general composition rules to compute a new TED as an algebraic sum (+) or product (·) of two TEDs. The general composition process for TEDs is similar to that of the APPLY operator for BDD's [1], in the sense that the operations are recursively applied on respective graphs. However, the composition rules for TEDs are specific to the rules of the algebra  $(R, \cdot, +)$ .

Starting from the roots of the two TEDs, the TED of the result is constructed by recursively constructing all the non-zero terms from the two functions, and combining them, according to a given operation, to form the diagram for the new function. To ensure that the newly generated nodes are unique and minimal, the REDUCE operator is applied to remove any redundancies in the graph.

Let *u* and *v* be two nodes to be composed, resulting in a new node *q*. Let var(u) = x and var(v) = y denote the decomposing variables associated with the two nodes. The top node *q* of the resulting TED is associated with the variable with the higher order, i.e., var(q) = x, if  $x \ge y$ , and var(q) = y otherwise. Let *f*, *g* be two functions rooted at nodes *u*, *v*, respectively, and *h* be a function rooted at the new node *q*.

For the purpose of illustration, we describe the operations on linear expressions, but the analysis is equally applicable to polynomials of arbitrary degree. In constructing these basic operators, we must consider several cases:

- 1. Both nodes u, v are terminal nodes. In this case a new *terminal* node q is created as val(q) = val(u) + val(v) for the ADD operation, and as  $val(q) = val(u) \cdot val(v)$  for the MULT operation.

- 2. At least one of the nodes is non-terminal. In this case the TED construction proceeds according to the variable order. Two cases need to be considered here: (a) when the top nodes u, v have the same index, and (b) when they have different indices. The detailed analysis of both cases is given in [70]. Here we show the multiplication of two diagrams rooted at variables u and v with the same index.

$$h(x) = f(x) \cdot g(x) = (f(0) + xf'(0)) \cdot (g(0) + xg'(0))$$

=  $[f(0)g(0)] + x[f(0)g'(0) + f'(0)g(0)] + x^2[f'(0)g'(0)].$  (19)

In this case, the 0-child of q is obtained by pairing the 0-children of u, v. Its 1-child is created as a sum of two cross products of 0- and 1-children, thus requiring an additional ADD operation. Also, an additional 2-child (representing the quadratic term) is created by pairing the 1-children of u, v.

Figure 16: Multiplicative composition for nodes with same variables.

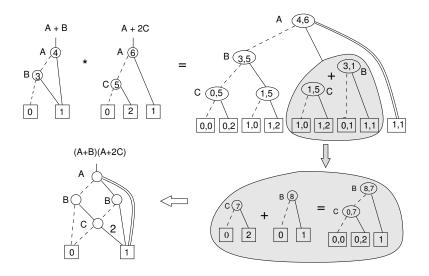

Figure 17 illustrates the application of the ADD and MULT procedures to two TEDs. As shown in the figure, the root nodes of the two TEDs have the same variable index. The MULT operation requires the following steps: (i) performing the multiplication of their respective constant (0-) and linear (1-) children nodes; and (ii) generating the sum of the cross-products of their 0- and 1-children. On the other hand, the two TEDs corresponding to the resulting cross-product, as highlighted in the figure, have different variable indices for their root nodes. In this case, the node with the lower index corresponding to variable *C* is added to the 0-child of the node corresponding to variable *B*.

It should be noted that the ADD and MULT procedures described above will initially produce nonnormalized TEDs, with numeric values residing only in the terminal nodes, requiring further normalization. When these operations are performed on normalized TEDs, with weights assigned to the edges, then the following modification is required: when the variable indices of the root nodes of f and g are different, the edge weights have to be propagated down to the children nodes recursively. Downward propagation of edge weights results in the dynamic update of the edge weights of the children nodes. In each recursion step, this propagation of edge weights down to the children proceeds until the weights reach the terminal nodes. The numeric values are updated only in the terminal nodes. Every time a new node is created, the REDUCE and NORMALIZE operations are required to be performed in order to remove any redundancies from the graph and generate a minimal and canonical representation.

Figure 17: Example of MULT composition: (A+B)(A+2C).

#### 4.8 Design Modeling and Verfication with TEDs

Using the operations described in the previous section, Taylor Expansion Diagrams can be constructed to represent various computations over integers in a compact, canonical form. The compositional operators ADD and MULT can be used to compute any combination of arithmetic functions by operating directly on their TEDs. However, the representation of Boolean logic, often present in the RTL designs, requires special attention since the output of a logic block must evaluate to Boolean rather than to an integer value.

**Boolean Logic.** Similarly to \*BMDs, one can also define TED operators for Boolean logic, OR, AND, and XOR, where both the range and domain of function are Boolean. This can be done in much the same way as it is done for \*BMDs. In fact, the TED and \*BMD for a Boolean logic are identical, because they require only the first moment decomposition (refer to Figure 5).

Similarly one can derive other operators which rely on Boolean variables as one of their inputs, with other inputs being word-level. One such example is the multiplexer,  $MUX(c, X, Y) = c \cdot X + (1-c) \cdot Y$ , where *c* is a binary control signal, and *X* and *Y* are word-level inputs.

In general, TED, which represents an integer-valued function, will also correctly model designs with arithmetic and Boolean functions. Note that the ADD (+) function will always create correct integer result over Boolean and integer domains, because Boolean variables are treated as binary (0,1), a special case of integer. However the MULT (·) function may create powers of Boolean variables,  $x^k$ , which should be reduced to x. A minor modification of TED is done to account for this effect so that the Boolean nature of variable x can be maintained in the representation. Such modified Taylor Expansion Diagrams are also canonical.

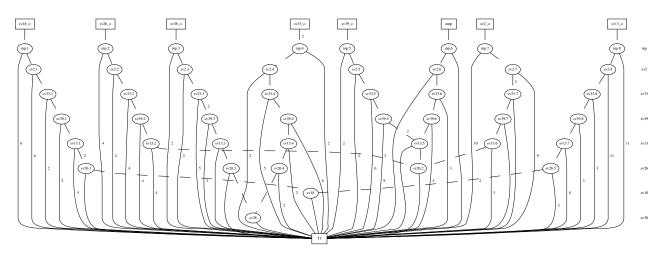

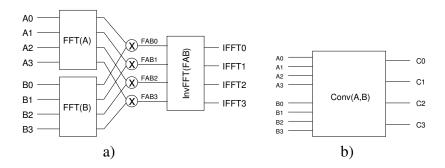

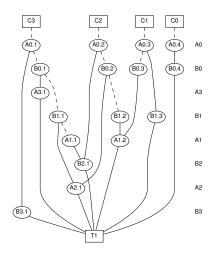

**TED Construction for RTL Designs.** TED construction for an RTL design starts with building trivial TEDs for its primary inputs. Partial expansion of the word-level input signals is often necessary when one or more bits from any of the input signals fan out to other parts of the design. This is the case in the designs shown in Fig. 18 (a) and (b), where bits  $a_k = A[k]$  and  $b_k = B[k]$  are derived from word-level variables A and B. In this case, the word-level variables must be

decomposed into several word-level variables with shorter bit-widths. In our case,  $A = 2^{(k+1)}A_{hi} + 2^k a_k + A_{lo}$  and  $B = 2^{(k+1)}B_{hi} + 2^k b_k + B_{lo}$ , where  $A_{hi} = A[n-1:k+1]$ ,  $a_k = A[k]$ , and  $A_{lo} = A[k-1:0]$ ; and similarly for variable *B*. Variables  $A_{hi}, a_k, A_{lo}, B_{hi}, b_k, B_{lo}$  form the *abstracted* primary inputs of the system. The basic TEDs are readily generated for these abstracted inputs from their respective bases  $(A_{hi}, a_k, A_{lo})$ , and  $(B_{hi}, b_k, B_{lo})$ .

Figure 18: RTL verification using canonical TED representation: (a), (b) Functionally equivalent RTL modules; (c) The isomorphic TED for the two designs.