# On Generating Two Dimensional CMOS Cells

Jack A. Feldman<sup>1</sup> and Israel Koren<sup>2</sup>

2 Dept. of Electrical and Computer Engineering, Univ. of Mass. Amherst MA 01003 1 IBM Israel Scientific Center, Technion City, Haifa 32000, ISRAEL

Abstract. Most standard cell generators for CMOS circuits follow the single row (of transistor pairs) layout style. Multi-row layouts are then obtained by placing and interconnecting basic cells which were generated in the single row style.

In this paper we present an algorithm for generating two dimensional layouts. The number of rows (of transistor pairs) can be imposed by the user. This aspect ratio is selected so as to either minimize the total cell area or meet some height or width requirements.

We illustrate our algorithm through a set of examples, ranging from simple CMOS circuits to complex ones. We then compare the generated multi-row layouts to single row layouts of the same circuits. This comparison demonstrates the advantage of the two dimensional style over the single row style especially for more complex CMOS circuits.

#### 1. INTRODUCTION

and a  $n-{\sf type}$  transistor, which are vertically aligned at the center of their gates. Diffusion the internal connections. These wires are placed between and on top of the two diffusion has to be introduced in the diffusion run. Additional wiring is usually required to complete the same net they are connected as part of the diffusion run, otherwise a gap (or a break) runs horizontally along each side of the row. Whenever adjacent diffusion ports belong to linear arrangement (or a row) of transistor pairs. Each pair consists of a p -type transistor research focused on the layout style proposed by Uehara and vanCleemput [18], namely a Layout generation of standard cells for CMOS circuits has been studied extensively. Most

suggested in [1], employs a depth first search procedure and prunes the search tree by using wire density constraints achieving an optimal solution. are of heuristic nature, tuned towards wire density minimization. Finally, the algorithm The algorithms reported in [13], [15], [18], and [19] search for the optimal solution in as many consecutive transistor pairs as possible abut in their adjacent diffusion In [8] and [14] the authors propose algorithms that can handle general circuits but

circuits in the single row layout style which are then placed and interconnected in a which is then folded to generate a multi-row structure. 2) create the layout of (small) basic multi-row style were proposed: 1) create a single row layout for the given large generating layouts with multiple rows. multi-row structure to generate the given large circuit. The need for exploiting the second dimension lead to the development of strategies for Two approaches to lay out larger circuits in a

applying a set of appropriate rules. However, no algorithmic details are provided in these paction. In [10], [3], and [12] the authors propose an expert system approach to the genthe circuit description at the transistor level. Their experiments show that two or three eration of two dimensional layouts. There the initial placement and routing are improved by initial placement and iterative improvements followed by topological routing and comand interconnecting basic circuits laid out in the single row style. Their algorithm uses times denser layouts can be achieved compared to multi-row layouts obtained by placing In [9], the authors propose an automated system that generates a multi-row layout from

technique results in denser layouts compared to layouts generated in the single row style optimization in one dimension as usually done by the above mentioned algorithms. mize both vertical and horizontal dimensions at the transistor level, rather then perform These observations lead us to develop a more general algorithm, which attempts to opti-

sistor placement, and Section 4 presents the routing steps. Finally, we present some In Section 2 we describe the layout image. Section 3 describes the algorithms for the tranresults and discuss them in Section 5

### 2. IMAGE DEFINITION

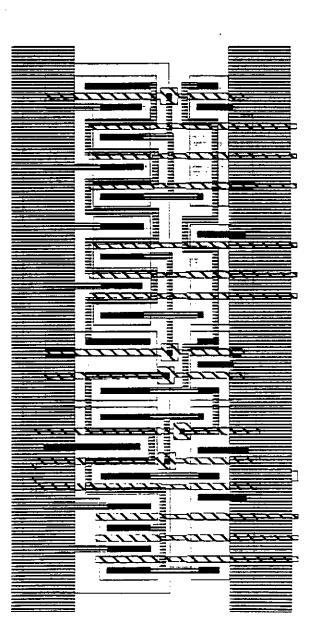

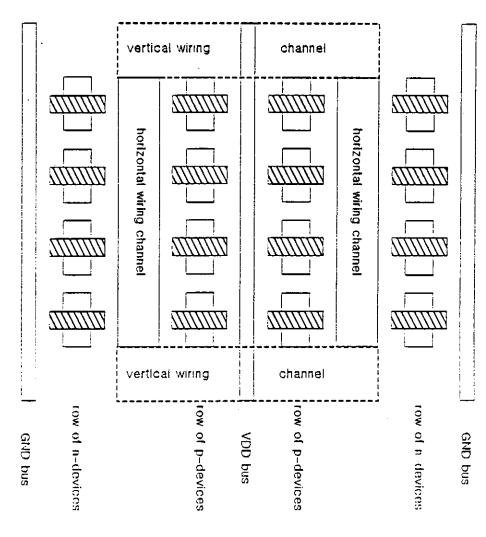

by our algorithm is illustrated in Figure 1. The layout has alternating ho and n transistor and the device width and length are specified. The generic image of the layouts generated For each transistor the type (p or n), the connections to its gate, drain and source ports topological description. Our algorithm generates automatically the symbolic layout of a CMOS cell starting from its rows arranged back to back. Power and ground buses are implemented in metal 1 layer The circuits are described in terms of their constituent transistors.

allows to generate layouts with different aspect ratios, which is useful in the following number of transistor rows versus transistor columns is a parameter of the algorithm. This and lie between consecutive transistor rows of type p and type n, respectively.

- building blocks). A layout with minimal total area is required (this occurs when constructing a library of

- (this occurs when considering the environment in which the cell is used). A layout that meets imposed dimensions, not necessary the minimum ones, is required

are located along different horizontal channels (see Figure 1). Horizontal routing channels are inserted between consecutive  $oldsymbol{p}$  and  $oldsymbol{n}$  transistor rows, for the left and right margins of the layout, and are used for connecting transistor ports that connecting the transistor ports that border the channel. Vertical routing channels extend

that intercell connections are accomplished in additional metal layers which allow to reach and outputs to the circuit are not restricted to specific locations in the layout. We assume I/O terminals on top of the underlying cells. Diffusion, polysilicon and metal 1 layers are used to accomplish internal routing. The inputs

transistors that can be placed in the first row are parameters of the placement program rows 2, 3, and 6 are reserved for n- type transistors. The number of rows and the type of rows. For example, if i=6 then rows 1, 4, and 5 are reserved for p- type transistors, and rows in the placement grid corresponds to a back to back arrangement of p-n transistor  $g_{ij}$ ,  $1 \le j \le m$  that compose a row i, are reserved to one transistor type. The sequence of sistor can be placed, n is the number of rows, and m the number of columns. These two parameters completely define the placement grid for a given circuit. The placement grid is an n imes m matrix G, where  $g_{ij}$  corresponds to a location where a tran-

#### 3. PLACEMENT

sistor orientation step, respectively smaller solution spaces, of size O(n!) and  $O(2^n)$  for the transistor assignment step and tranthe large solution space which is  $\mathit{O}(n! imes 2^n)$  , where n is the number of transistors, by two is determined. Partitioning the transistor placement into two well-defined steps replaces assigned to locations on the placement grid. In the second step the transistor orientation The transistor placement problem is solved in two steps. In the first, transistors are

### 3.1. TRANSISTOR ASSIGNMENT

cussed in the following paragraphs encourage placements for which adjacent transistors share the same nets as much as posmain goal when assigning transistors to locations in the placement grid The definition of the objective functions and the solution technique used are S

#### 3.1.1. Objectives

$g_{ij+1}$ , in a row i, share the same net in their adjacent drain/source ports. The reduction due to drain/source abutting results from the following: A significant reduction in area results if transistors placed in consecutive locations

- No spacing has to be introduced between consecutive transistors

- fusion without any extra wires. Connection between the adjacent drain/source ports is implemented directly in

- One or two contacts are saved, if the corresponding net is a multi-port or a two port net, respectively

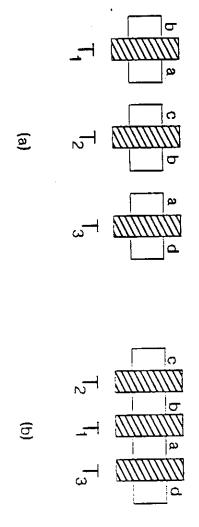

abutting diffusion ports. In case (b), two spaces between the adjacent transistors, tacts and two wires are saved compared to the configuration illustrated in Figure 2a. Figure 2 illustrates two different permutations of three transistors, with abutting and non-

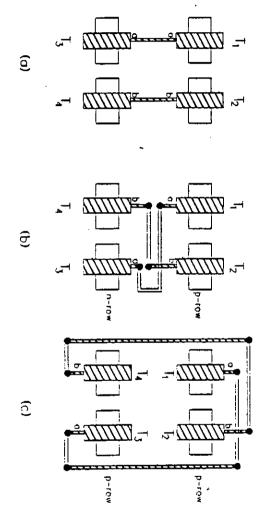

considered for the assignment algorithm are: the channel introduced between the adjacent transistor rows. In summary, the objectives gates to be connected are not aligned, the necessary connections must be accomplished in wire implemented in polysilicon, without any contacts. While, as shown in Figure 3b, if the area reduction is obtained if aligned consecutive transistors share the same net in their transistors placed in consecutive locations  $g_{i,j}$ ,  $g_{i+1,j}$  in the same column. Here a substantial Another factor that eases the routing and contributes to the area reduction is related to In Figure 3a the connection between aligned gates is accomplished by a straight

- In the horizontal direction maximize the number of diffusion abutments

- 'n In the vertical direction - maximize the number of polysilicon abutments

### 3.1.2. Mathematical Formulation

where /≥ e. ments and a set L = (1,...,l) of locations, find a one to one mapping from set E into set L quadratic assignment problem, which is stated as follows: problem of assigning transistors to grid locations can be formulated as the known given a set E = (1,...,e) of ele-

$$Q = [q_{ij}]$$

be a  $e \times e$  matrix, and  $D = [d_{ij}]$  be a  $l \times l$  matrix.

where:

is the measure of the affinity (or attraction) between element i and element j. is the distance between location i and location j.

ρ. Consider now the functional: mapping, and let ho(i) denote the location to which element i was assigned in the mapping Let S be the set of all possible mappings of set E into set L. Let  $\rho \in S$ , be a particular

$$H(\rho) = \sum_{ij} q_{ij} d_{\rho(i)\rho(j)} \tag{1}$$

Then, the quadratic assignment problem can be stated as follows:

# 3.1.3. An Interpretation for the Affinity and Distance Matrices

transistors, and the distance matrix provides some metric on the placement grid compose the set L. Then, the affinity matrix reflects the connectivity between the various The transistors that constitute a given circuit compose the set  ${m E}$  , and the n imes m locations

distance matrix by  $a_i^a$ . Let  $T_i$  and  $T_j$  denote two different transistors, then the element  $a_i^a$  is number of horizontal diffusion abutments. We denote here the affinity matrix by  $q_{\parallel}^{a}$  and the The first objective considered for the transistor assignment problem is to maximize the

$$q_{ij}^{h} = \begin{cases} 2 & \text{if } T_i \text{ and } T_j \text{ have both diffusion ports} \\ 1 & \text{if } T_i \text{ and } T_j \text{ have one diffusion port} \\ 1 & \text{labelled by the same net} \end{cases}$$

$$0 & \text{otherwise}$$

(3)

We label the locations in the placement grid from 1 to  $n \times m$ , with the convention that the rows of the matrix are scanned from left to right and from top to bottom. Let  $x_k$  and  $y_k$

ment grid. Then define denote the x- and y-coordinates associated with location k (1  $\leq k \leq n \times m$ ) in the place-

$$d_{ij}^{h} = \begin{cases} 0 & \text{if } y_i = y_j \land |x_i - x_j| \le 1 \\ c & \text{otherwise} \end{cases}$$

(4)

distinguish between the case where  $T_i$  and  $T_j$  share one diffusion port or two, since for the latter one two diffusion abutments are possible. If transistors  $T_i$  and  $T_j$  have no common case where both diffusion ports of  $T_i$  and  $T_j$  belong to the same nets) is added to  $H(\rho)$ . We added to the cost function  $H(\rho)$ . For any other assignment a penalty equal to c (or 2c in the assigned to adjacent locations in the same row of the placement grid, then no penalty is diffusion port, no penalty is added to the cost function  $extit{ extit{H}}(

ho)$  independent of their positions According to these definitions, if  $T_i$  and  $T_j$  have one or two common diffusion ports and are

For the second objective considered for the transistor assignment, namely, maximizing the matrix d<sub>i</sub>, as follows: number of vertical polysilicon abutments, we define the affinity matrix  $q_i^{\mu}$  and the distance

$$q_{ij}^{V} = \begin{cases} 1 & \text{if } T_i \text{ and } T_j \text{ share the same net in their gates} \\ 0 & \text{otherwise} \end{cases}$$

(5)

$$d_{ij}^{\nu} = \begin{cases} 0 & \text{if } x_i = x_j \ \land \ |y_i - y_j| \le 1 \\ c & \text{otherwise} \end{cases}$$

(6)

to the cost function  $H(\rho)$ , for any other assignment a penalty equal to c is added to  $H(\rho)$ . If transistors  $T_i$  and  $T_j$  do not share the same net in their gate no penalty is added to the cost consecutive locations in the same column of the placement grid, then no penalty is added function H(

ho) , independent of their location In this case, if transistors  $T_i$  and  $T_j$  share the same net in their gates and were assigned to

### 3.1.4. Solution Technique

that belongs to this class is due to Graves and Whinston [6]. posed to solve the quadratic assignment problem. A very efficient constructive algorithm practice we deal with much larger problems, various heuristic algorithms have been pro-Gilmore [7], and the cutting plane method proposed by Bazara and Sherali [2] . Since in lems ( $n \le 15$ ). These include the branch and bound methods proposed by Lawler [11] and methods for finding the optimal solution are computationally feasible only for small prob-The quadratic assignment problem has proven to be NP-complete [5] and consequently,

mean value has been derived in [6] and is reproduced in equation 7. value over all possible completions of a k-partial permutation. first k element-location pairs unchanged. The selection criterion is based on the mean Define the kth partial permutation as a mapping of the set E into the set L that leaves the An expression for this

$$\mu = \sum_{i \in F} \sum_{j \in F} q_{i,j} d_{\rho(i), \rho(j)} + \frac{1}{n-k} \sum_{k \in F} \sum_{j \in F} \sum_{t \in \widetilde{T}} (q_{i,j} d_{\rho(i),t} + q_{j,i} d_{t, \rho(i)})$$

$$+ \frac{1}{(n-k)(n-k-1)} \sum_{u \in F} \sum_{j \in F} q_{j,u} \sum_{s \in \widetilde{T}} \sum_{t \in \widetilde{T}} d_{s,t}$$

$$(7)$$

where

$\tilde{F} = \{i_1,...,i_k\}$ , the set of assigned elements.  $\tilde{F} = \{i_{k+1},...,i_n\}$ , the set of unassigned elements.  $T = \{j_1,...,j_k\}$ , the set of occupied locations.  $\tilde{T} = \{j_{k+1},...,j_n\}$ , the set of free locations.

signed and all locations are free, i.e. F=I, and  $\widetilde{F}=\{i_1,...,i_n\}$  , and  $\widetilde{I}=\{j_1,...,j_n\}$  . The malization factors correspond to the mean values in the case where all elements are unascombine the two objectives, the two mean values  $\mu_h$  and  $\mu_v$  must be normalized. The nor $d_{ij}$  by  $d_{ij}^{\mu}$  in (7). Similarly, we substitute  $q_{ij}$  by  $q_{ij}^{\mu}$  and  $d_{ij}$  by  $d_{ij}^{\mu}$  in (7) to obtain  $\mu_{\nu}$ . In order to and distance matrices. Let  $\mu_h$  and  $\mu_v$  denote the mean value for the horizontal and vertical which the smallest mean is obtained. Note that expression (7) holds valid for any affinity  $(n-k)^{\mu}$  combinations) we compute its mean value, and select that element-location pair for objective, respectively. assignments is not required. For each feasible unassigned element-location pair (out of normalization factors are given therefore, by: An important property of the scheme in [6] is that the enumeration of all the possible Then the expression for  $\mu_h$  is obtained by substituting  $q_{ij}$  by  $q_{ij}^{th}$  and

$$N_{h} = \frac{1}{n^{2}} \sum_{u \in F} \sum_{j \in F} q_{ju}^{h} \sum_{s \in T} \sum_{t \in T} d_{st}^{h}$$

$$(8)$$

$$N_{V} = \frac{1}{n^{2}} \sum_{i} \sum_{f} q_{ju}^{V} \sum_{f} \sum_{\tilde{t} \in \tilde{I}} d_{\tilde{s}\tilde{t}}^{V}$$

$$(9)$$

expression, i.e., Finally, we combine the two normalized objectives and attempt to minimize a single

$$M = w_h \frac{1}{N_h} \mu_h + w_V \frac{1}{N_V} \mu_V \tag{10}$$

relative significance where  $w_h$  and  $w_r$  are weights assigned to the two objectives to allow us to control their

### 3.1.5. Enumeration Scheme

order O(n!). In step k a new element-location pair is selected out of the remaining (n-k)location on the placement grid are of the same type one having the smallest mean. An element-location pair is feasible if the transistor and the pair out of  $(n-k)^2$  possibilities, we compute the corresponding mean value and select the unassigned elements and (n-k) unoccupied locations. For each feasible element-location The enumeration scheme employed, constructs one path within a virtual search tree of

### 3.1.6. Complexity of the Algorithm

mean value of the (k + 1)th partial permutation is given by the following expression: element-location pair, where  $w \in F$  and  $v \in T$ . Then, the contribution of the pair w,v to the to the mean value of the kth partial permutation. Let w and v denote the currently selected k+1 we compute the contribution of the currently selected element-location pair and add it of step k we compute and store the mean value of the kth partial permutation. In step contribution of the currently selected element-location pair. Accordingly, after completion observation: the mean value in step k + 1 differs from the mean value in step k only by the mean value calculation can save O(n) computations. This is due to the following computed and this has an  $O(n^3)$  complexity. However, a careful implementation of the where at step k there are  $(n-k)^2$  combinations of unassigned elements and unoccupied results from the fact that n steps are required to map the n elements into the n locations, A straightforward implementation of the above search algorithm has an  $O(n^{6})$  complexity. It Finally, for each element-location pair considered, the mean value has to be

$$C = \sum_{i} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} \sum_{l} (q_{sw} d_{lv} + q_{ws} d_{vl})$$

$$- \left( \sum_{l} \sum_{t} (q_{iw} d_{\rho(i)t} + q_{wi} d_{t\rho(i)}) + \sum_{l} \sum_{l} (q_{ij} d_{\rho(i)v} + q_{ji} d_{v\rho(i)}) \right)$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) - \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) - \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) - \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (d_{vl} + d_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (q_{vl} + q_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (q_{vl} + q_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (q_{vl} + q_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (q_{vl} + q_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) - \sum_{l} (q_{vl} + q_{lv})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) + \sum_{l} (q_{vl} + q_{ws} d_{vl})$$

$$+ \sum_{l} (q_{iw} d_{\rho(i)v} + q_{wi} d_{v\rho(i)}) + \sum_{s} (q_{ws} + q_{sw}) + \sum_{l} (q_{ws} + q_{ws}) + \sum_{s} (q_{ws}$$

Emplying (11) the computation of the mean value requires  $O(n^2)$  steps as opposed to (7) which requires  $O(n^3)$  steps and consequently,  $O(n^5)$  is the complexity of our search algo-

## 3.1.7. Strategy for Determining the Weights

effort. However, the following heuristic strategy can be employed to select values for w, An additional optimization for the best  $w_1/w_2$  ratio is possible but it does not justify the between  $w_1$  and  $w_2$  for which the best result is obtained, depends on the circuit topology. Weights  $w_1$ ,  $w_2$  are attached to the above two objectives. Intuitively it is clear that the ratio

- given circuit. Set  $w_1 = 1$  and  $w_2 = 0$  and find the number  $x_1$  of potential diffusion abutments for the

- Set  $w_1 = 0$  and  $w_2 = 1$  and find the number  $x_2$  of aligned gates that share the same net.

- Set  $w_1 = 1$  and  $w_2 = 1$  and find  $x'_1$  and  $x'_2$ , the number of potential diffusion abutments and the number of aligned gates that share the same net, respectively.

two objectives should be assigned a higher weight. The values  $(x_1 - x'_1)$  and  $(x_2 - x'_2)$  can be used as a guideline to determine which one of the

## 3.2. OPTIMAL ORIENTATION OF TRANSISTORS

sistor orientation and then proceed with the proposed solution technique the right side or vice versa. In what follows we present the objectives considered for trantwo orientations are possible, the drain port can be at the left side and the source port at However, no decision concerning the transistor orientation was made. For each transistor In the first phase of the placement procedure, transistors were assigned to locations.

#### 3.2.1. Objectives

abutment cost for two transistors placed in consecutive columns in the same row. sistor that was placed in row i column j and has orientation l. Let  $e^h$  denote the horizontal connection is implemented by a straight wire and requires less contacts. Let  $T_{(i,j)}$  be a tranaligned diffusion ports share the same net, as shown in Figure 4a., is preferred over the horizontal abutment cost is defined as follows: orientation shown in Figure 4b. column. Here an orientation of consecutive transistors in the same column such that their The secondary objective considered is related to consecutive transistors in the same fusion breaks. Adjacent diffusion ports in the same row which share the same net are preferred over dif-This is the primary objective considered for the transistor orientation step. The transistor orientation in case (a) is better since the

$$e^{h}(T_{(i,j)}^{l}, T_{(i,j-1)}^{k}) = \begin{cases} if \ T_{(i,j)}^{l} \text{ and } T_{(i,j-1)}^{k} \text{ share the same net} \\ in their adjacent diffusion ports} \\ 0 \ otherwise \end{cases}$$

the same column. The vertical alignment cost is defined as follows: denote the vertical alignment cost for two transistors placed in consecutive rows in

$$e^{V(T_{(i,j)}^{I},T_{(i-1,j)}^{K})} = \begin{cases} 2 & \text{if } T_{(i,j)}^{I} \text{ and } T_{(i-1,j)}^{K} \text{ share the same net} \\ 2 & \text{in their aligned diffusion ports} \\ 1 & \text{if } T_{(i,j)}^{I} \text{ and } T_{(i-1,j)}^{K} \text{ share the same net} \\ 1 & \text{in one of the aligned diffusion ports} \\ 0 & \text{otherwise} \end{cases}$$

### 3.2.2. Solution Technique

technique is extended in what follows to satisfy our requirements gramming algorithm was suggested for finding the optimal solution. posed. This solution technique is computationally too expensive. In [1], a dynamic probranch and bound algorithm, that implicitly enumerates the entire solution space, was promatic cell generation in the single row style of p and n type transistor pairs. In [8] a The transistor orientation problem has been previously mentioned in works related to auto-This solution

The dynamic programming technique is applicable due to the following two properties of

- (j − 1)-th transistor column. Property 1: The optimal orientation of the j-th transistor column depends only on the

- Property 2: Both cost measures are additive functions

sistor that belongs to column j, and its value reflects the transistor's orientation. For each figuration l. A state is coded by a sequence of  $n \, 0/1$  bits where each bit stands for a tran- $1 \le j \le m$  and  $1 \le l \le 2^n$ , denote the orientation for transistors in column j according to conand m represents the number of columns, from left to right, column by column. There are ment cost for concatenating the transistors in columns j and j-1. Its expression is given state (j,l) two costs are computed. The first one reflects the best horizontal diffusion abut- $2^n$  possible configurations for transistor orientations in a column. Let state (j,l) , where The algorithm scans the  $[n \times m]$  placement matrix, where n represents the number of rows

$$C_{(i,j)}^{h} = \max_{1 \le k \le 2^{n}} \{ C_{(j-1,k)}^{h} + \sum_{i=1}^{n} e^{h} (T_{(i,j)}^{l}, T_{(i,j-1)}^{k}) \}$$

(12)

where  $C^h_{(j-1,k)}$  is the best horizontal diffusion abutment cost so far for state (j-1,k)

expression is given by: The second one reflects the best vertical diffusion alignment cost for state (j,l). Its

$$C_{(j,l)}^{\nu} = \sum_{i=2}^{N} e^{\nu} (T_{(i,j)}^{l}, T_{(i-1,j)}^{l}) + \max_{1 \le k \le 2^{n}} \{C_{(j-1,k)}^{\nu}\}$$

(13)

where  $C_{(j-1,k)}^{\nu}$  is the best vertical diffusion alignment cost so far for state (j-1,k).

pred(j,l). For j=m we choose among the states (m,l) the ones for which  $C^h_{m,l}$  is maximum. If  $C_{i,i}^{h}$  and  $C_{i,i}^{v}$  (which are computed by equation (12) and (13) above) and its predecessor  $l=1..2^n$  with costs  $C_{1,l}^h$  and  $C_{1,l}^v$ . For each state (j,l) we keep its horizontal and vertical costs indices  $k_0$  the one which maximizes the expression in (13). Initially we have the states (1,l) backtracking from j = m to j = 1 using the predecessor states. there is more then one such state, we break ties by  $\mathcal{C}_{m,l}^{\mathsf{v}}$  . The final solution is obtained by maximizes expression (12). In case this index is not unique, we choose among all the Let the predecessor to state (j,k), denoted by pred(j,k), be  $k_0$ , where  $k_0$  is the index which

#### 4. ROUTING

than one horizontal channel. The main difference between these two channel types is that internal to these channels. Vertical channels are used to interconnect nets that lie in more illustrated in Figure 1. The horizontal channels are used to interconnect ports which are interconnect the various transistor ports. These wires will be routed through channels as Once the transistor placement and orientation steps have been completed, we need to

the ports in the horizontal channels are distributed along the four sides, whereas for the vertical channels, ports are distributed along one side only

belong to the same net are connected through diffusion. horizontally, as it is usually done in channel routing. Polysilicon layer, and metal 1 layer are used to complete the interconnections in the horizontal and vertical channels. Polysilicon wires run only vertically while metal 1 wires run Adjacent drain/source ports that

The overall strategy used for the routing algorithm is a left to right scan of the routing tem-These steps are as follows: The routing process is partitioned into five steps which are executed sequentially

- tacts and the wiring density in the routing channels. nets in the vertical channels, and as a result reduces the wire length, number of confusion ports which belong to the same net. This step attempts to avoid the routing of belong to the same net and straight vertical diffusion wires that connect aligned difof the same type. Determine and mark the nets that can be routed between consecutive transistor rows straight vertical polysilicon wires that connect aligned transistor gates which The connections allowed between transistor rows of the same type

- Ņ each net so that wire length is minimized. connected in the previous step. Either the right channel or the left one is selected for nets that have their ports distributed on different horizontal channels, and were not Determine the nets to be routed in the left and right vertical channel. These are the

- ω Routing of the left vertical channel. Assignment of wires to tracks is accomplished by

- 4 pattern is a variation of the greedy channel router [17]. Routing of the horizontal channels. The algorithm used to decide upon the routing

- 5 used again to assign wires to tracks in the right vertical channel Finally, routing of the right vertical channel is performed. Interval graph coloring is

### 5. RESULTS AND DISCUSSION

way AND gate, and 9 way OR gate. generating layouts with different aspect ratios Table 1 illustrates the results obtained for the Full-Adder. layouts through a sample of circuits. These include: In this section we demonstrate the advantages that result from generating two dimensional A layout for the full adder is illustrated in Figure 5 a full adder, multiplexor, decoder, 9 It demonstrates the capability of

important to have the capability to generate layouts with different aspect ratios. This capaminimal area layout does not always occur for the same aspect ratio. As was intuitively expected, circuits behave differently for various aspect ratios and the Consequently, it is

obtained when 6 rows were used. By varying  $w_t/w_t$  the layout area might be further the available space on the chip. Note that for this example the minimal area layout was which cells are used. In this case layouts must meet the imposed dimensions according to bility is also important if area constraints are imposed by the surrounding environment in

Tatter was developed to handle standard cells in the style of one dimensional arrangement layouts were generated for the same technology with the same ground rules, which makes technique that searches for the optimal solution in terms of diffusion breaks and wiring achieved by the two tools. the comparison fair from this point of view. Table 2 presents the comparison of the results density. The same compactor was used as the back end tool for both systems. Thus, of p-n transistor pairs. area, with layouts generated automatically by a similar system developed at IBM [1]. The In order to measure the quality of the generated layouts they were compared in terms of There, the placement algorithm is based on a branch and bound

packing the circuits. The two dimensional layout style becomes more effective in terms of under a certain value (say 5 wiring tracks) this layout style is the most effective one for general remark, as long as the wiring density for the linear transistor arrangement is kept the total area for larger circuits. whereas for smaller circuits (e.g., AND and OR gates) the IBM tool performed better. As a multiplexor and decoder) better layouts (in terms of area ) were generated by our tool, results obtained by the IBM tool. For larger and more complex circuits (e.g., full adder, The results demonstrate that the layouts generated by our tool are competitive with the

which allow dynamic exchange of layout styles in the process of composing the chip, will imposed requirements by the surrounding environment. It is our belief that CAD tools is the most important capability, since it allows to select that layout style which best fits the However, the flexibility for generating layouts with different aspect ratios for a given circuit, represent the future trend.

cuted on a 4381 IBM computer. Table 3 shows the computation time required for these cir-Our system was implemented in Pascal containing about 4000 lines, and has been exe-

#### 6. CONCLUSIONS

topology, and accommodates well-defined optimization criterions back. The presented algorithm does not impose structural limitations on the and p -type transistor rows, where alternating p-n transistor rows are arranged back to style of two dimensional layouts has been developed. The proposed image, has  $n-{

m type}$ A new algorithmic method for laying out circuits from their schematic description, in the circuit

rounding environment in which the layouts are used. minimal area layouts are required, and in a dynamic context when considering the surratios for the generated layouts. This allows to use the layouts in a static context, where One of the most important capabilities of the system is that it can deal with different aspect

exploited for reducing the total layout area The presented results demonstrate that optimization in two dimensions can be efficiently

done in the department of Electrical Engineering at the Technion, Israel. The authors wish their useful comments to thank Alfred Bruckstein for helpful discussions, and Shmuel Wimer and Ron Pinter for Acknowledgements. This paper is based on the first author's M.Sc. research which was

#### REFERENCES

- Ξ research in VLSI, Proceedings of the Fifth MIT Conference, 1988, 215-228. Dynamic Programming Algorithms for Efficient CMOS Cell Generation, Advanced Bar-Yehuda R, J.A. Feldman, R.Y. Pinter and S. Wimer, Depth First Search and

- 2 methods for the quadratic assignment problem., J. Op. Res. Soc. 33, 1980, 991-1003. Bazaraa M.S., and H.D. Sherali On the use of exact and heuristic cutting plane

- [3]module synthesis 24th DAC, 1987, 666-671. Cesear T., E. lodice, and C. Tsareff PAMS: An expert system for parameterized

- $\Xi$ System, IBM Journal of Research and Development 28, 5 (September 1984), 572-580 Fiebrich R.-D., Y.-Z. Liao, G. Koppelman, and E. N. Adams, PSI - a Symbolic Layout

- [5] of NP-Completeness., W.H. Freeman, 1979. Garey M.R., and D.S. Johnson Computers and Intractability: A Guide to the Theory

- [9]Mgmt Sci. 16, 1970, 453-471. Graves G.W., and A. Whinston An algorithm for the quadratic assignment problem.

- [7] problem., J. SIAM 10, 1962, 305-313. Gilmore P.C. Optimal and suboptimal algorithms for the quadratic assignment

- 8 1985, 172-174. Hill D., Sc2 - a Hybrid Automatic Layout System, Proceedings of ICCAD, November

- [9] Cells., Proceedings of ICCAD, 1986, 440-443. Hughes T.A., R. Salama and W. Liu, BBC: A Module Generator for Back-to-Back

- [10] transistor connectivity to symbolic cell layout IEEE J. of Solid-State Circuits, Kollaritsch P.W. and N.H.E. Weste, TOPOLOGIZER: An expert system translator of

- Lawler E.L. The Quadratic Assignment Problem., Mgmt Sci. 9, 1963, 586-599

- [12]Lin S., and D. Gajski, LES: A Layout Expert System, 24th. DAC, 1987, 672-678

- [13] Muller R., and T. Lengauer, Linear Algorithms for two CMOS Layout Problems, Proc. Aegean Workshop Comput., July 1986

- [14] for CMOS transistor-pair array LSI, Integration, Vol. 4, 1986, 115-133. Miyashita H., T. Adachi, and K. Ueda, An automatic cell pattern generation system

- [15] Nair, R., A. Bruss, and J. Reif Linear Time Algorithms for Optimal CMOS Layout, (North-Holland), 1985, 327-338. VLSI: Algorithms and Architectures, P. Bertolazzi and F. Luccio (Eds), Elsevier

- [16] Ohtsuki T., Layout design and verification, North-Holland, 1986.

- [17] Rivest, R. L., and C. M. Fiduccia, A "Greedy" Channel Router, Proceedings of the Nineteenth Design Automation Conference, June 1982, 418-424.

- [8] Uehara T., and W. M. vanCleemput, Optimal Layout of CMOS Functional Arrays. IEEE Transactions on Computers C-30, 5, May 1981, 305-312.

- [19] Wimer S., R.Y. Pinter, J.A. Feldman Optimal Chaining of CMOS Transistors in a Functional Cell, IEEE Transaction on Computer Aided Design, Vol. CAD-6, No. 5, 1987, 795-801.

| No. of rows | W1 | ₩2 | Layout<br>width | Layout<br>length | Total<br>area | No. of Poly adjacencies | No. of Diffusion abutments |

|-------------|----|----|-----------------|------------------|---------------|-------------------------|----------------------------|

| 2           | _  | _  | 143.7           | 72.9             | 10475.7       | 16                      | 34                         |

| 4           | _  | _  | 83              | 145.8            | 12101         | 23                      | 30                         |

| 4           | _  | 0  | 101             | 143.8            | 14523.8       | 23                      | 24                         |

| 4           | 0  | 1  | 85.3            | 155.5            | 13264.1       | 8                       | 30                         |

| 4           | _  | 2  | 71.9            | 132.8            | 9533.9        | 18                      | 39                         |

| 6           | _  | _  | 65.3            | 141              | 9207.3        | 26                      | 38                         |

| 6           | 1  | 0  | 92.6            | 189              | 17501.4       | 27                      | 22                         |

| 6           | 0  | 1  | 68.9            | 188.4            | 12980.7       | 11                      | 37                         |

| 8           | 1  | 1  | 67              | 214.9            | 14405         | 25                      | 30                         |

| 8           | 0  | -  | 61              | 238              | 14518         | 11                      | 34                         |

Table 1. Results for FULL-ADDER

| cell        | total area<br>single-row | total area<br>multi-row | no. of rows<br>multi-row |

|-------------|--------------------------|-------------------------|--------------------------|

| Full-Adder  | 9790.4                   | 9207.3                  | 6                        |

| Multiplexor | 39427.3                  | 37959                   | 4                        |

| Decoder     | 44262.8                  | 41760                   | 4                        |

| And gate    | 6554.7                   | 8477                    | 4                        |

| Or gate     | 5216                     | 7810                    | 4                        |

Table 2. Comparison table

| Cell           | No. of rows | No. of No. of rows elements | Assignment Orientation Routing CPU time (sec) CPU time (sec) CPU time (sec) | Orientation<br>CPU time (sec) | Routing<br>CPU time (sec) |

|----------------|-------------|-----------------------------|-----------------------------------------------------------------------------|-------------------------------|---------------------------|

| Full adder     | 8           | 32                          | 27                                                                          | 13                            | 0.7                       |

| Multiplexor    | 8           | 62                          | 245                                                                         | 31.6                          | 1.5                       |

| Decoder        | 8           | 88                          | 773                                                                         | 42.7                          | 2.8                       |

| 9 way AND gate | 8           | 30                          | 28                                                                          | 13.2                          | 0.6                       |

| 9 way OR gate  | 8           | 32                          | 27                                                                          | 13                            | 0.6                       |

|                |             |                             |                                                                             |                               |                           |

rable 3. Computation time

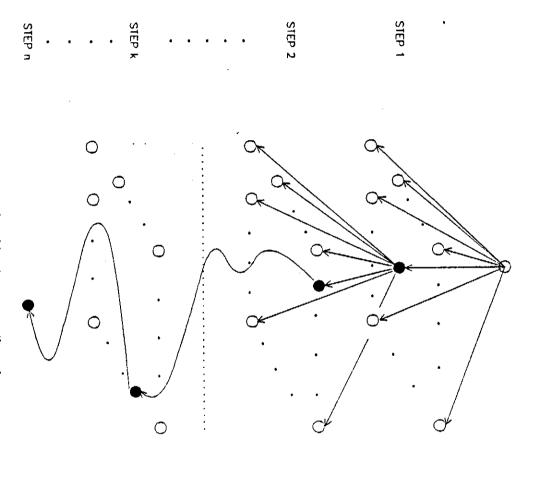

Figure 1. layout in the single row style.

igure 2. layout style.

igure 4. diffusion abutment versus non abutment.

aligned transistor gates sharing the same net versus aligned transistors gates that belong to different nets.

Figure 6. virtual search tree employed for the enumeration scheme.