Csaba Andras-Moritz

andras@ecs.umass.edu

(413) 545-2442

Administrative Asst.

Christine Langlois

Phone:(413)-545-3621

Address

University of Massachusetts, Amherst,

Elect. and Comp. Eng.

Knowles Eng. Building,

209H,

Amherst, MA 01003

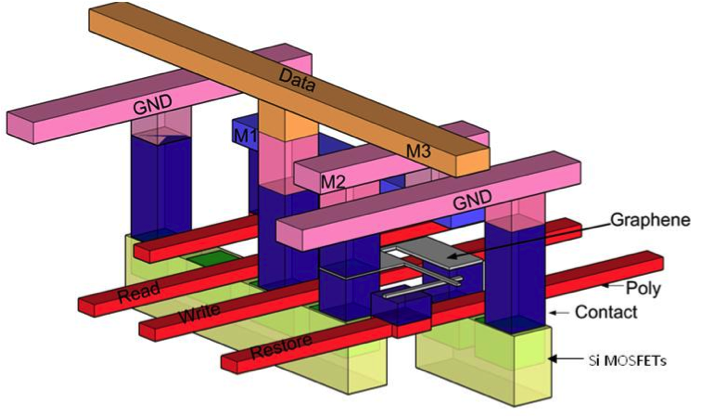

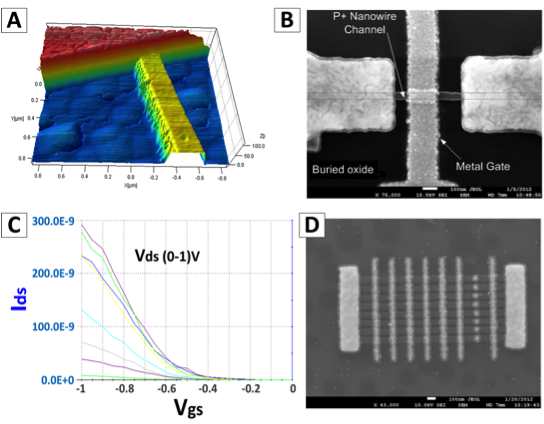

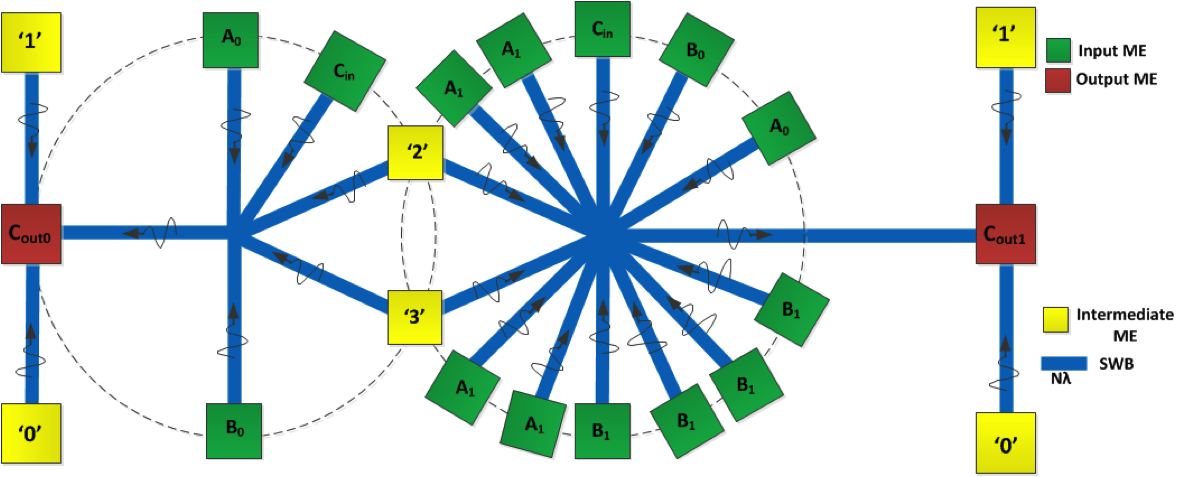

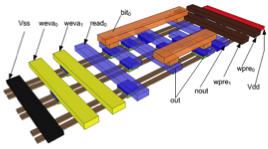

Figures - Below: 2-bit NASIC ALU; Right : nanofabric components -graphene, nanowire, spin based- AFM images sub 30nm

I'm an entrepreneur and professor in the Electrical and Computer Engineering department at the University of Massachusetts in Amherst.

My group's research focus is on novel computing fabrics and models of computation. We often target cross-layer device-circuit-architecture explorations. Current directions include Skybridge 3D nanofabric for digital ICs and various Bayesian Inference Architectures. Other nanofabrics initiated include NASICs, Spin Wave Functions, Magneto-electric designs, etc. We demonstrated the N3ASIC nanofabric at sub-30nm scale in 2014. My group is a winner of 10 Best Paper or Poster awards since 2008.

I founded BlueRISC Inc in 2002. BlueRISC is a cyber-security company that develops system assurance tools & solutions. WindowsSCOPE, another of my initiatives, focuses on forensics tools. Overall BlueRISC systems and tools are sold in 21 countries. I initiated EPRIVO in consumer privacy, that has amassed 100K+ users worldwide.

I am the Director of the Nanoscale Fabrics and Architectures Laboratory. I co-lead the Nanoelectronics Technical Research Group at the CHM/NSEC (NSF-sponsored research center) and was a member of its executive committee. I was a member of the FENA nanoarchitectonics FCRP/Darpa center's executive committee and a Theme Lead for Nanofabrics.

I organized as General Chair of IEEE/ACM International Symposium on Nanoscale Architectures (Nanoarch) in 2011, 2012, 2013, 2014, 2015, 2016 and 2017 (San Diego, Amsterdam, NYC, Paris, Boston, Bejing, and Newport RI editions). I was on the editorial board of several IEEE journals and was the first steering commitee chair of IEEE Transactions on Multi-Scale Systems.

Awards in my group: Best Paper IEEE Symposium on VLSI 2021, IEEE/ACM Symposium on Nanoscale Architectures Best Paper Award 2013 & 2014, Best 20 Last 25 Years Paper Award at IEEE Symposium on Custom Computing Machines 2013, IEEE Symposium on VLSI 2008 Best Paper award (out of 220+ papers), Best Student Paper at IEEE DFT 2010, Best Student Paper Award at IEEE/ACM Symposium on Nanoscale Architectures 2011, Best Student Paper IEEE DFT 2011 and Research Poster awards at the FENA/FCRP annual reviews including at MIT in 2011 and UCLA in 2012.

Former students : My former grad students work in academia (5) or are at Google, Microsoft, Qualcomn, Marwell, IBM Research, Intel, Lattice, BlueRISC, Nvidia, Tensilica, etc. They work on both conventional and emerging computing with AI, and associated technology development.

Rahman Mostafizur is a professor at the Univ of Missouri; Pritish Narayanan is a researcher at IBM Research; Yao Guo is an associate professor at Peking University. Mahmoud Bennaser is a professor at Kuwait University. Osman Unsal (co-advised) is a senior computer architecture researcher at Universitat Politecnica de Catalunia in Barcelona. Santosh Khasanvis is a senior research scrientist at BlueRISC. Tom Wang works on nanoscale CMOS technology at Qualcomm. Raksit Ashok is a compiler architect at Google, Saurabh Chheda is CPU architect at Tensilica. Prasad Shabadi is a CPU architect at Intel.

TEACHING: entrepreneurship, cognitive machines, advanced computer architecture (graduate), nanoscale fabrics (graduate), computer systems lab I and II (undergrad), parallel architectures (graduate), and low-power microprocessors (graduate).

PHD / POST-DOC ADVISORS: Lars-Erik Thorelli (Royal Institute of Technology, Stockholm) / Anant Agarwal (MIT), Saman Amarasinghe (MIT)